思考:1、在經典的 DynamIQ架構 中,數據是什么時候存在L1 cache,什么時候存進L2 cache,什么時候又存進L3 cache,以及他們的替換策略是怎樣的?比如什么時候數據只在L1?什么時候數據只在L2?什么時候數據只在L3?還有一些組合,比如什么時候數組同時在L1和L3,而L2沒有?這一切的規則是怎樣定義的?

2、本文不討論什么MESI協議,也不討論cache基本原理,本文討論的是多級cache之間的替換策略。

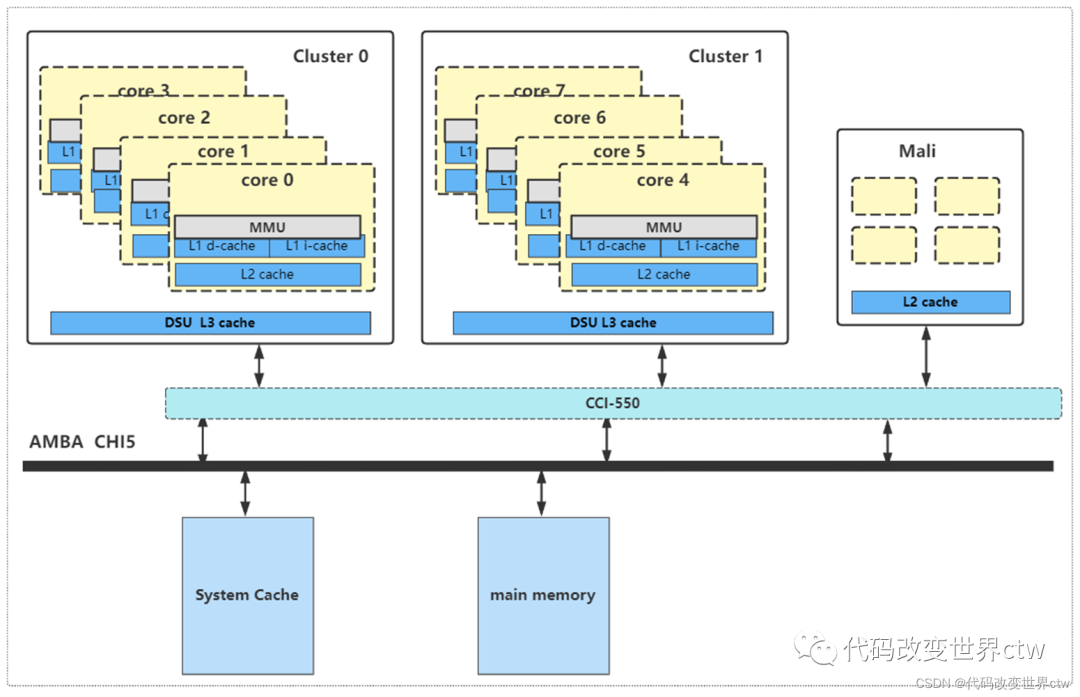

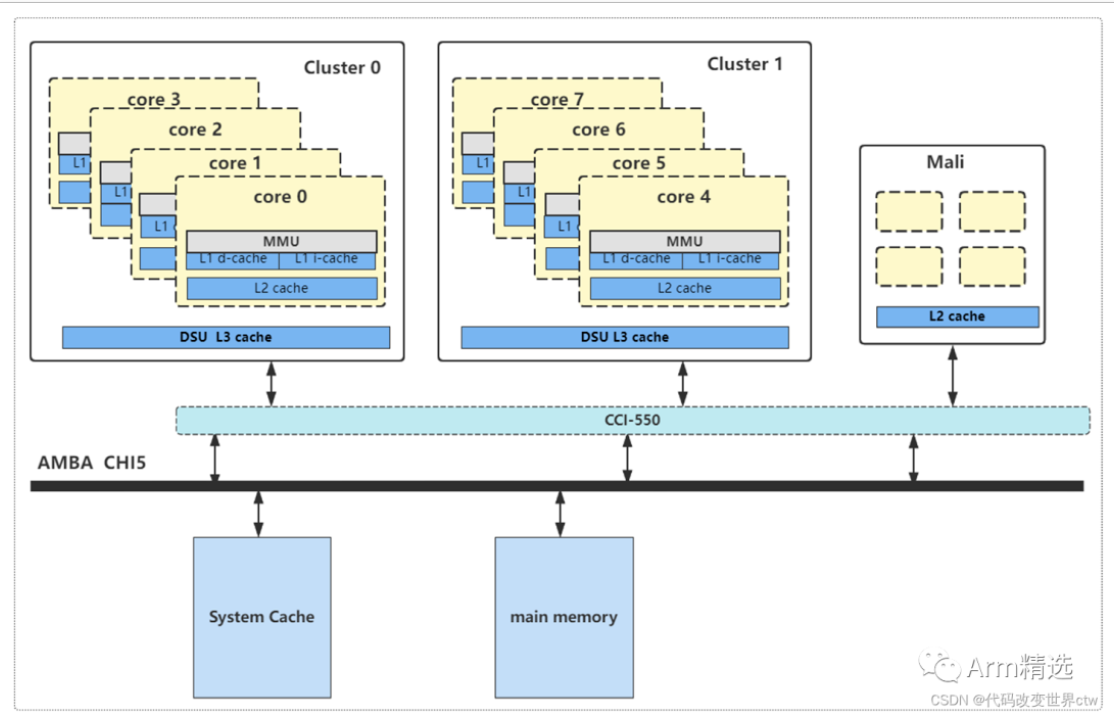

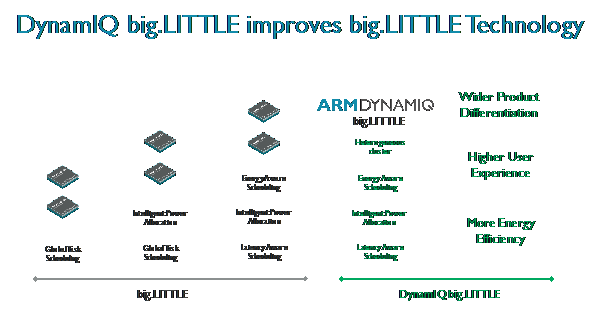

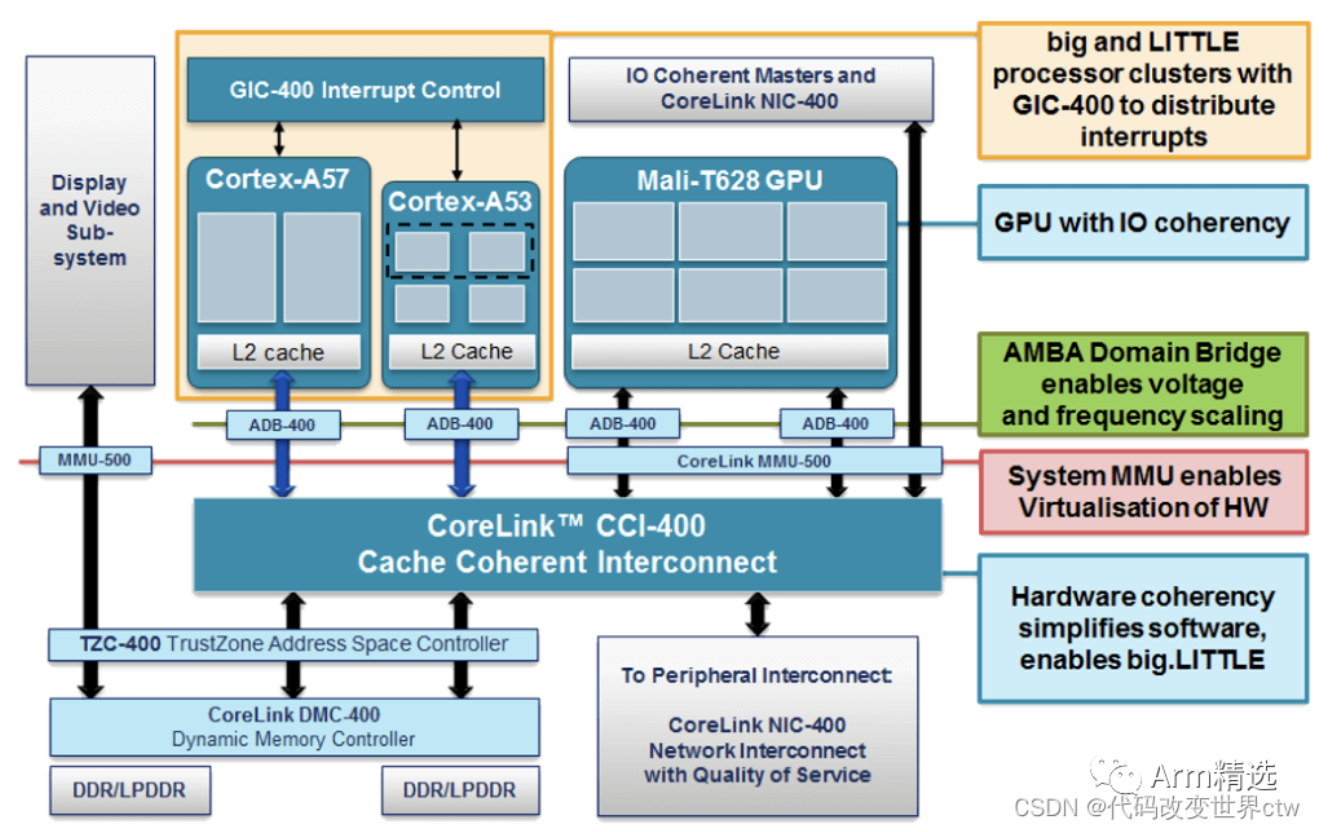

說明:本文討論經典的DynamIQ的cache架構,忽略 big.LITTLE的cache架構

1、L1 / L2 cache直接的替換策略

我們先看一下DynamIQ架構中的cache中新增的幾個概念:

(1)Strictly inclusive: 所有存在L1 cache中的數據,必然也存在L2 cache中

(2)Weakly inclusive: 當miss的時候,數據會被同時緩存到L1和L2,但在之后,L2中的數據可能會被替換

(3)Fully exclusive: 當miss的時候,數據只會緩存到L1

綜上總結:inclusive/exclusive 描述的僅僅是 L1和L2之間的替換策略

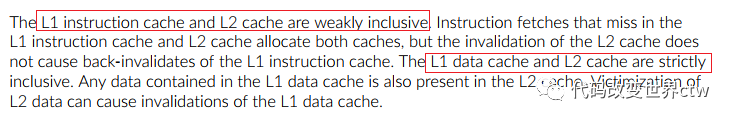

我們再去查閱 ARMV9 cortex-A710 trm手冊,查看該core的cache類型,得知:

L1 I-cache和L2之間是 weakly inclusive的

L1 D-cache和L2之間是 strictly inclusive的

也就是說:

當發生D-cache發生miss時,數據緩存到L1 D-cache的時候,也會被緩存到L2 Cache中,當L2 Cache被替換時,L1 D-cache也會跟著被替換

當發生I-cache發生miss時,數據緩存到L1 I-cache的時候,也會被緩存到L2 Cache中,當L2 Cache被替換時,L1 I- cache不會被替換

再次總結 :L1 和 L2之間的cache的替換策略,I-cache和D-cache可以是不同的策略,每一個core都有每一個core的做法,請查閱你使用core的手冊。

2、core cache / DSU cache / memory 之間的替換策略

說實話, core cache/DSU cache/ 這個名字可能不好,感覺叫 privatecache和share cache更好,我也不知道官方一般使用哪個,反正我們能理解其意思即可吧。

那么他們之間的替換策略是怎樣的呢?

我們知道MMU的頁表中的表項中,管理者每一塊內存的屬性,其實就是cache屬性,也就是緩存策略。其中就有cacheable和shareable、Inner和Outer的概念。如下是針對 DynamIQ 架構做出的總結,注意哦,僅僅是針對 DynamIQ 架構的cache。

如果將block的內存屬性配置成Non-cacheable,那么數據就不會被緩存到cache,那么所有observer看到的內存是一致的,也就說此時也相當于Outer Shareable。其實官方文檔,也有這一句的描述:在B2.7.2章節 “Data accesses to memory locations are coherent for all observers in the system, and correspondingly are treated as being Outer Shareable”

如果將block的內存屬性配置成write-through cacheable 或 write-back cacheable,那么數據會被緩存cache中。write-through和write-back是緩存策略。

如果將block的內存屬性配置成 non-shareable, 那么core0訪問該內存時,數據緩存的到Core0的L1 D-cache / L2 cache (將L1/L2看做一個整體,直接說數據會緩存到core0的private cache更好),不會緩存到其它cache中。

如果將block的內存屬性配置成 inner-shareable, 那么core0訪問該內存時,數據只會緩存到core 0的L1 D-cache / L2 cache和 DSU L3 cache,不會緩存到System Cache中(當然如果有system cache的話 ) ,(注意這里MESI協議其作用了)此時core0的cache TAG中的MESI狀態是E, 接著如果這個時候core1也去讀該數據,那么數據也會被緩存core1的L1 D-cache / L2 cache, 此時core0和core1的MESI狀態都是S

如果將block的內存屬性配置成 outer-shareable, 那么core0訪問該內存時,數據會緩存到core 0的L1 D-cache / L2 cache 、cluster0的DSU L3 cache 、 System Cache中, core0的MESI狀態為E。如果core1再去讀的話,則也會緩存到core1的L1 D-cache / L2 cache,此時core0和core1的MESI都是S。這個時候,如果core7也去讀的話,數據還會被緩存到cluster1的DSU L3 cache. 至于DSU0和DSU1之間的一致性,非MESI維護,具體怎么維護的請看DSU手冊,本文不展開討論。

| Non-cacheable |

write-through cacheable |

write-back cacheable |

|

|---|---|---|---|

| non-shareable |

數據不會緩存到cache (對于觀察則而言,又相當于outer-shareable) |

core0訪問該內存時,數據緩存的到Core0的L1 D-cache / L2 cache (將L1/L2看做一個整體,直接說數據會緩存到core0的private cache更好),不會緩存到其它cache中 | 同左側 |

| inner-shareable |

數據不會緩存到cache (對于觀察則而言,又相當于outer-shareable) |

core0訪問該內存時,數據只會緩存到core 0的L1 D-cache / L2 cache和 DSU L3 cache,不會緩存到System Cache中(當然如果有system cache的話 ) , (注意這里MESI協議其作用了)此時core0的cache TAG中的MESI狀態是E, 接著如果這個時候core1也去讀該數據,那么數據也會被緩存core1的L1 D-cache / L2 cache, 此時core0和core1的MESI狀態都是S | 同左側 |

| outer-shareable |

數據不會緩存到cache (對于觀察則而言,又相當于outer-shareable) |

core0訪問該內存時,數據會緩存到core 0的L1 D-cache / L2 cache 、cluster0的DSU L3 cache 、 System Cache中, core0的MESI狀態為E。如果core1再去讀的話,則也會緩存到core1的L1 D-cache / L2 cache,此時core0和core1的MESI都是S 思考:那么此時core7去讀取會怎樣? |

同左側 |

審核編輯:劉清

-

數據緩存

+關注

關注

0文章

24瀏覽量

7327 -

MMU

+關注

關注

0文章

92瀏覽量

18673

原文標題:深度解讀DynamIQ架構cache的替換策略

文章出處:【微信號:LinuxDev,微信公眾號:Linux閱碼場】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

紫光展銳推出全球首款基于DYNAMIQ架構的4核LTE平臺--虎賁T310

ARM全新DynamIQ架構奠定未來10年發展基礎

淺析Cache多核之間的一致性MESI協議

DynamIQ世界中的big.LITTLE是什么樣的?

淺析ARM處理器的power架構

Arm DynamIQ共享單元技術參考手冊

ARM Dynamiq共享單元-120型技術參考手冊

ARM Dynamiq?共享單元-110型技術參考手冊

DynamIQ世界中的big.LITTLE

評論