面對快速發(fā)展的威脅,國防部可以尋求基于 COTS 的快速原型設(shè)計,實現(xiàn)經(jīng)濟(jì)高效的高性能數(shù)字信號處理系統(tǒng),以滿足情報、監(jiān)視和偵察 (ISR) 操作的嚴(yán)格尺寸、重量和功率 (SWaP) 限制和任務(wù)目標(biāo)。

現(xiàn)代戰(zhàn)爭迫使美國軍方迅速適應(yīng)快速演變的不對稱威脅,以保持美國軍方的戰(zhàn)術(shù)態(tài)勢感知能力。然而,傳統(tǒng)上對由專用集成電路 (ASIC) 和專用標(biāo)準(zhǔn)產(chǎn)品 (ASSP) 組成的定制煙囪式數(shù)字信號處理 (DSP) 系統(tǒng)實現(xiàn)的依賴限制了美國軍事情報、監(jiān)視和偵察 (ISR) 操作的敏捷性。

為了應(yīng)對這些限制和不穩(wěn)定的威脅,美國國防部正在越來越多地資助ISR快速反應(yīng)能力(QRC)。然而,這種新的采購模式要求戰(zhàn)術(shù)ISR系統(tǒng)開發(fā)人員快速制作具有成本效益的高性能DSP系統(tǒng)原型,同時滿足嚴(yán)格的尺寸、重量和功率(SWaP)計劃要求。為了滿足這些需求,一種新穎的快速原型設(shè)計方法利用COTS硬件/軟件信號處理技術(shù)和成本建模來縮小數(shù)據(jù)收集/分析差距,挫敗傳統(tǒng)ISR設(shè)計方法的局限性,減少開發(fā)時間和費用,同時滿足具有挑戰(zhàn)性的ISR任務(wù)要求。

縮小ISR任務(wù)情景中的收集-分析差距

在過去幾年中,對ISR能力的需求增加導(dǎo)致數(shù)據(jù)收集能力呈指數(shù)級增長,并將在可預(yù)見的將來繼續(xù)這樣做。然而,ISR 數(shù)據(jù)處理、利用和傳播 (PED) 流程在同一時期僅線性改進(jìn),在收集和分析能力之間留下了關(guān)鍵的差距。為了縮小收集與分析的差距,國防部需要基于DSP的高性能ISR系統(tǒng),該系統(tǒng)能夠自動、實時地處理大量數(shù)據(jù),并將可操作的情報直接傳播給戰(zhàn)場上的作戰(zhàn)人員。

實時、自動化 PED 等高端 ISR 應(yīng)用突破了最先進(jìn)的 COTS DSP 技術(shù)的極限。吞吐量要求可能超過數(shù)十 tera 操作/秒。新的眾核圖形處理單元(GPU)和通用處理器(GPP)架構(gòu)在理論上似乎能夠滿足這種高端性能要求。然而,開發(fā)并行軟件算法以充分利用多核架構(gòu)峰值性能的一小部分是一項極其艱巨的任務(wù)。

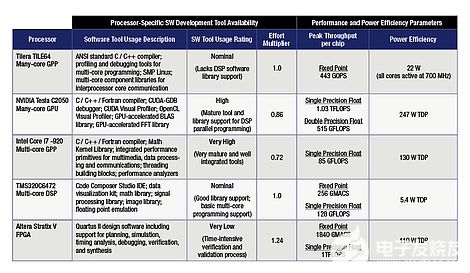

在嚴(yán)格的SWaP約束下滿足如此極端性能要求的具有成本效益的系統(tǒng)實現(xiàn)的快速原型設(shè)計是一項艱巨的任務(wù)。在前端設(shè)計過程中進(jìn)行詳細(xì)的權(quán)衡分析和廣泛的架構(gòu)探索對于實現(xiàn)這一目標(biāo)至關(guān)重要。表 1 顯示了眾核 GPU、多核/眾核 GPP、多核 DSP 和現(xiàn)場可編程門陣列 (FPGA) 技術(shù)在處理器專用軟件工具可用性、處理器峰值吞吐量和能效方面的比較。特定于處理器的軟件開發(fā)工具的成熟度對系統(tǒng)開發(fā)工作、成本和進(jìn)度有重大影響。系統(tǒng)開發(fā)人員必須在軟件工具支持的成熟度與硬件性能和能效之間做出最佳權(quán)衡,以滿足高端 ISR 應(yīng)用要求。

表 1:系統(tǒng)開發(fā)人員必須在軟件工具支持的成熟度與硬件性能和能效之間做出最佳權(quán)衡,以滿足高端 ISR 應(yīng)用要求。

傳統(tǒng) ISR 設(shè)計方法的局限性

當(dāng)今的大多數(shù)ISR系統(tǒng)都遵循“瀑布式”開發(fā)方法,該方法規(guī)定了順序過程。目前高性能ISR系統(tǒng)的瀑布式設(shè)計流程施加了許多限制,包括:

有限的建筑探索

漫長的原型制作時間

設(shè)計成本高

缺乏系統(tǒng)的硬件/軟件重用

循環(huán)硬件制造和測試

大多數(shù)設(shè)計自動化活動都專注于利用工具支持進(jìn)行詳細(xì)的系統(tǒng)行為設(shè)計,而不是早期架構(gòu)設(shè)計,其中大部分系統(tǒng)成本都已投入。目前的工業(yè)實踐主要依靠設(shè)計人員的經(jīng)驗來選擇系統(tǒng)架構(gòu)和分配算法功能。此外,對于完全定制的ISR系統(tǒng),硬件和軟件子系統(tǒng)直到硬件制造后才會集成,這使得設(shè)計錯誤的成本非常高昂。

接地氣的創(chuàng)新:基于 COTS 的快速原型設(shè)計

ISR 系統(tǒng)開發(fā)成本超支和進(jìn)度延遲頻率的增加迫使國防部采購社區(qū)推出許多計劃,鼓勵承包商社區(qū)更好地利用 COTS DSP 硬件板和系統(tǒng)組件。

然而,在基于COTS硬件的系統(tǒng)中,軟件開發(fā)的時間和成本可以主導(dǎo)進(jìn)度和預(yù)算。基于歷史項目數(shù)據(jù)的參數(shù)化研究表明,如果處理器和內(nèi)存資源的松弛幅度限制太大,設(shè)計和測試嵌入式軟件尤其困難。嚴(yán)重的資源限制可能會阻止嵌入式軟件開發(fā)人員利用高級編程工具,從而需要與硬件和/或操作系統(tǒng)直接交互以優(yōu)化代碼以滿足系統(tǒng)要求。

一個在業(yè)界引起關(guān)注的創(chuàng)新解決方案是快速原型設(shè)計方法,該方法利用 COTS 硬件/軟件信號處理技術(shù)和成本建模的使用,顯著降低 ISR 系統(tǒng)的總成本和開發(fā)時間。這種方法利用了基于 COTS 庫的優(yōu)化框架,該框架包括吞吐量、硬件/軟件開發(fā)成本以及進(jìn)度、采購成本和 SWaP 之間的權(quán)衡。這種快速原型設(shè)計方法可在前端設(shè)計過程中最大限度地探索系統(tǒng)架構(gòu)。由此產(chǎn)生的解決方案是經(jīng)濟(jì)高效的DSP嵌入式系統(tǒng),利用眾核GPU、多/眾核GPP、多核DSP和/或FPGA技術(shù)的靈活性,同時滿足任務(wù)目標(biāo)規(guī)定的嚴(yán)格SWaP約束。

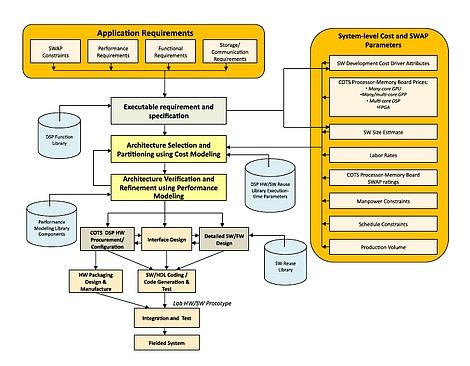

圖1所示為基于COTSP的快速DSP系統(tǒng)原型設(shè)計方法。該過程首先使用信號處理庫和集成的圖形用戶界面(GUI)工具包(如MATLAB中提供的工具包)將書面系統(tǒng)需求轉(zhuǎn)換為可執(zhí)行的需求和規(guī)范。可執(zhí)行的要求和規(guī)范為客戶提供了一個早期的原型,以驗證原始要求并消除歧義。這種反饋允許盡早收到任何需求變更,這對于最大限度地降低需求蔓延的高成本至關(guān)重要,這是軟件項目中最常見的風(fēng)險之一。

圖 1:基于COTS的快速原型設(shè)計方法優(yōu)先考慮應(yīng)用需求和成本建模,這對于最大限度地降低需求蔓延的高成本至關(guān)重要。

在驗證系統(tǒng)要求、系統(tǒng)級成本參數(shù)、應(yīng)用要求和性能統(tǒng)計信息后,這些組件為架構(gòu)選擇和分區(qū)優(yōu)化過程提供依據(jù)。系統(tǒng)開發(fā)人員可以使用參數(shù)化成本模型(如 COCOMO II)來驅(qū)動架構(gòu)權(quán)衡分析,從而生成硬件/軟件架構(gòu)候選方案,從而最大限度地降低總系統(tǒng)成本和開發(fā)時間。成本參數(shù)包括:軟件成本驅(qū)動因素屬性(大小、產(chǎn)品、平臺、人員和項目)、COTS 硬件采購成本、產(chǎn)品部署期限、進(jìn)度約束以及人工成本和約束。應(yīng)用程序要求包括 SWaP、環(huán)境、優(yōu)先級和實時約束,以及功能、內(nèi)存和通信要求。性能統(tǒng)計數(shù)據(jù)包括在重用庫中包含的 DSP 處理器板(例如,眾核 GPU、多核/眾核 GPP、多核 DSP、FPGA)上執(zhí)行的 DSP 基元(例如,快速傅里葉變換)的基準(zhǔn)時間測量值。

然后,系統(tǒng)開發(fā)人員可以使用動態(tài)性能建模工具(如 Simulink)模擬生成的架構(gòu)候選項,以驗證架構(gòu)是否滿足系統(tǒng)級要求。在性能建模之后,系統(tǒng)架構(gòu)師將通信開銷參數(shù)(如通信排隊延遲和瓶頸)反饋到體系結(jié)構(gòu)選擇階段進(jìn)行優(yōu)化。該方法使用更新的模型參數(shù)生成新的架構(gòu)候選項,并重復(fù)該過程,直到架構(gòu)滿足性能要求,并且在連續(xù)迭代之間不再發(fā)生變化。

經(jīng)過優(yōu)化的硬件/軟件架構(gòu)候選者將進(jìn)入詳細(xì)的架構(gòu)設(shè)計階段,以進(jìn)行詳細(xì)的軟件和/或固件設(shè)計,硬件/軟件接口設(shè)計和COTS采購。根據(jù)所選的 COTS DSP 硬件平臺和架構(gòu),DSP 軟件和/或固件設(shè)計過程在很大程度上利用了以前項目中開發(fā)的可重用庫。評估、選擇、同化和修改可重用組件的成本也必須降至最低,以顯著降低軟件開發(fā)費用和時間。系統(tǒng)設(shè)計人員可以改進(jìn)候選架構(gòu)的性能模型和可執(zhí)行信號處理算法規(guī)范,以允許自動將代碼生成為C編程語言或硬件描述語言。為了能夠使用自動代碼生成工具,目標(biāo)DSP板架構(gòu)必須有足夠的硬件資源松弛裕量和高級軟件工具支持。

系統(tǒng)的高級虛擬原型使系統(tǒng)設(shè)計人員能夠在設(shè)計過程的早期發(fā)現(xiàn)硬件/軟件集成錯誤。這種方法允許在昂貴的硬件封裝組裝和現(xiàn)場測試之前識別和糾正低級性能限制。

快速原型設(shè)計幫助 ISR 系統(tǒng)跟上步伐

ISR系統(tǒng)的傳統(tǒng)DSP實現(xiàn)已無法再跟上現(xiàn)代戰(zhàn)爭的步伐。系統(tǒng)開發(fā)人員需要一種快速原型設(shè)計方法,利用 COTS 硬件/軟件信號處理技術(shù)和成本建模的使用,從而顯著降低 ISR 系統(tǒng)的總成本和開發(fā)時間。艾維希斯科技的實時智能分析方法充分利用了這種基于 COTS 的快速原型設(shè)計方法。前端設(shè)計過程通過結(jié)合軟件成本和開發(fā)時間模型實現(xiàn)自動化。設(shè)計優(yōu)化過程將開發(fā)時間和成本減少了四倍。基于IvySys COTS的快速原型設(shè)計方法使國防部和情報界能夠快速適應(yīng)快速發(fā)展的不對稱威脅,從而保持美國的戰(zhàn)術(shù)態(tài)勢感知能力。

審核編輯:郭婷

-

dsp

+關(guān)注

關(guān)注

553文章

7987瀏覽量

348782 -

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603044 -

asic

+關(guān)注

關(guān)注

34文章

1199瀏覽量

120441

發(fā)布評論請先 登錄

相關(guān)推薦

實現(xiàn)具有多個TMS320C31 DSP的快速3D視覺傳感器

MES系統(tǒng)的最佳實踐案例

使用TMS320C31 DSP實現(xiàn)信號處理子系統(tǒng)以檢測激勵聲發(fā)射

快速部署原型驗證:從子卡到調(diào)試的全方位優(yōu)化

雙核dsp和單核dsp的區(qū)別

RL78/G24快速原型開發(fā)板資料包大全

FPB-R9A02G021 RISC-V MCU快速原型設(shè)計板介紹

使用AURIX studio開發(fā)帶有FreeRTOS的MCU TC387-QP TriCore,如何實現(xiàn)GPIO ISR功能?

FPB-RA2E3快速原型板的介紹和演示概述

軟件定時器回調(diào)里面調(diào)用的系統(tǒng)API是要用中斷級的還是任務(wù)級的?

快速控制原型RCP與硬件在環(huán)仿真HIL該如何區(qū)分呢?

分享DSP和ARM的激光粒度儀關(guān)鍵電路設(shè)計

詳解快速控制原型RCP與硬件在環(huán)仿真HIL

快速原型設(shè)計幫助實現(xiàn)ISR任務(wù)的最佳DSP系統(tǒng)

快速原型設(shè)計幫助實現(xiàn)ISR任務(wù)的最佳DSP系統(tǒng)

評論