鑒于對高級快速原型設計和在無人機平臺上部署ISR應用程序的需求不斷增加,系統工程師將明智地檢查與工作資格相匹配的可重構架構和靈活的軟件工具。

可重構計算系統是為無人機 (UAV) 上的情報、監視和偵察 (ISR) 應用提供異構數字信號處理 (DSP) 計算解決方案的絕佳且越來越受歡迎的選擇。與其他類型的系統相比,可以為ISR無人機身應用創建具有更小尺寸,重量和功率(SWaP)和更高計算密度的可重構系統。

此外,現在可以使用ANSI標準C或FORTRAN進行編程環境,并使程序員能夠從硬件中提取所有可能的計算性能。使用標準編程語言大大縮短了學習曲線,與使用專有非標準語言或純硬件語言的編程環境相比,可以更快地部署應用程序。因此,無人機ISR系統開發人員應該考慮在其設計中必須重新配置的計算架構和靈活的軟件工具。

無人機有效載荷的可重構計算

在考慮快速部署無人機有效載荷時,可重新配置的硬件是關鍵。可重構系統的核心是FPGA集成電路。該器件可以顯式編程以執行特定于應用的算法,并且相對于通用設備(如CPU或通用圖形處理器單元(GPGPU))產生非常高的計算效率。反過來,這種計算效率為在可重構系統上執行的應用程序產生高性能的每瓦特,從而能夠為基于無人機的ISR應用創建計算密集/低SWaP設計。

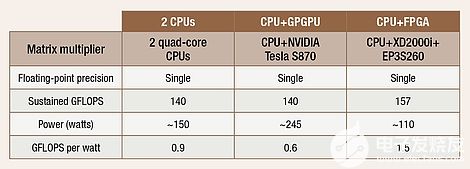

表 1 比較了在僅 CPU 系統、與 GPGPU 配對的 CPU 和與 FPGA 配對的 CPU 上執行單精度矩陣乘法基準測試的情況。可重構系統的每瓦性能比僅支持 CPU 的系統高出 1.7 倍,比 CPU/GPGPU 系統高出 2.5 倍。請注意,CPU/FPGA 組合的總功耗是最低的功耗。

表 1:矩陣乘法性能/功率比。資料來源:Altera公司,“FPGA協處理演進:持續性能接近峰值性能”,WP-01031-1.1,2009年6月版本1.1。

(單擊圖形可縮放 1.9 倍)

快速無人機有效載荷部署的一個主要因素是標準編程工具的可用性,這些工具與可重新配置的計算機硬件密切相關。集成來自不同供應商的編譯器、軟件工具、FPGA 板和 CPU 板的零碎方法會減慢部署速度。如果工具和硬件具有不同的供應商,則必須創建一個系統運行時環境來統一系統,然后才能開始有意義的應用程序工作。

一旦真正的應用程序開發最終開始,一個供應商的編譯器宏庫(假設它們確實有庫)將不會針對另一個供應商的FPGA板進行優化,因此應用程序開發必須經歷性能規格的降低或時間表擴展。無人機有效載荷開發的零碎方法中的這些和其他固有困難共同將“快速”一詞與“部署”分離,通常以意想不到的方式,并且總是在應用程序開發期間。因此,來自一個供應商的完整,集成良好的軟件和硬件包通常是快速部署無人機有效載荷的最佳途徑。

可擴展的系統和并行編程

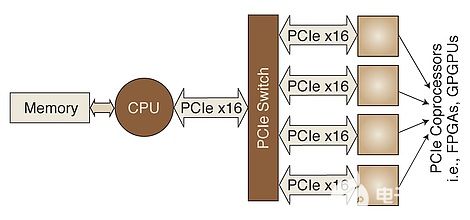

模塊化、可擴展的系統非常適合代碼重用,這也加速了無人機有效載荷的部署。軟件設計的模塊化允許經過驗證的代碼在多個ISR應用程序中重復使用,而硬件模塊化則支持根據任務參數和無人機機身的SWaP要求輕松擴展ISR應用程序。如今,大多數異構系統都使用一種或另一種形式的 PCIe,使協處理器能夠通過 CPU 訪問系統內存。但是,PCIe 的有效可擴展性受到其阻塞的“多對一”架構的限制(圖 1)。PCIe 協處理器僅通過 CPU 另一端的系統內存訪問數據并相互通信。雖然 PCIe 確實通過 PCIe 交換機提供點對點連接,但一個點始終是 CPU 內存,另一個點始終是 PCIe 設備。真正可用的擴展需要分布式內存和交換網絡,該網絡具有與交換機上任何模塊之間的無阻塞、“多對多”連接。

圖 1:典型的基于 PCIe 的協處理器架構,由于其阻塞“多對一”點對點架構,可擴展性有限

一個能夠很好地擴展的模塊化硬件系統只是一個良好的開端。軟件工具必須為程序員提供對可重構系統中密集計算效率的直觀或自動訪問。如果程序員必須深入到系統的體系結構中以查找和開發滿足應用程序性能要求的解決方案,則無人機有效載荷的開發和部署會受到影響。有標準的計算機語言可用于在可重構系統中對CPU和FPGA進行編程,但僅使用C或FORTRAN并不能實現ISR應用的性能要求。C 和 FORTRAN 是傳統上用于 CPU 的串行編程語言,其中指令按順序執行,一次一條指令。可重構系統的性能是通過并行編程實現的:多個程序指令流同時作用于多個數據流。

幸運的是,科學超級計算社區已經為C和FORTRAN開發了并行化技術,其中許多技術已被一些可重新配置的系統編譯器采用。以編程方式指定并行性的一種方法是 OpenMP 并行部分雜注語句。在傳統的大型微處理器集群上,并行部分雜注所包含的代碼塊可以在CPU上并行執行。在可重配置的系統上,OpenMP 樣式編譯指示指定的代碼塊在 FPGA 中實例化,以便這些“硬件代碼塊”并行執行。另一種方法是數據流,其中一系列計算在時間上重疊;例如,計算塊可以在收到前一個塊的第一個結果時開始執行,而不是在開始之前等待前一個計算塊的所有結果生成。

除了從科學超級計算中借用的并行化技術外,大多數可重新配置的系統編譯器還執行自動循環流水線以提高執行性能。此外,可重新配置的系統編譯器在FPGA硬件中自動創建程序循環中的所有算術運算,所有這些運算都是并行執行的。與此形成鮮明對比的是微處理器編譯器,微處理器編譯器受 CPU 設計中可用算術計算元素數量的限制。這里真正的問題是給定系統的特定軟件工具集的有效性。但是,軟件工具確實存在,可以為計算密集型ISR應用程序的程序員提供可重新配置硬件中的潛在性能。

可重配置性有助于快速部署、SWaP

如今,可重新配置的系統和工具可用于快速開發和部署 ISR 應用程序。可重構系統的密集計算特性使其成為尺寸、重量和功耗至關重要的解決方案的理想選擇。軟件工具與硬件緊密耦合,使軟件程序員能夠在低SWaP處理器有效載荷中快速實現高性能。

因此,SRC計算機提供模塊化,可擴展,可重新配置的低SWaP系統,帶有軟件工具和庫,使用ANSI標準語言快速部署無人機的計算密集型ISR應用程序。SRC Computers開發了一種高帶寬,低延遲的網絡交換機,除了用于模塊間通信的數據流構造,用于代碼塊并行化的OpenMP樣式編譯指示以及用于指令級并行化的自動循環流水線外,還提供了必要的非阻塞“多對多”模塊。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19259瀏覽量

229652 -

dsp

+關注

關注

553文章

7987瀏覽量

348745 -

無人機

+關注

關注

229文章

10420瀏覽量

180134

發布評論請先 登錄

相關推薦

為無人機快速部署可擴展、密集的ISR有效負載

為無人機快速部署可擴展、密集的ISR有效負載

評論