Efabless這是一家芯片設計服務公司,這家公司比較有意思的是在google的贊助下發(fā)起了一個叫Open MPW Shuttle Program的項目,這個項目是為一些完全開源的芯片設計提供流片的機會。這對一些想學習芯片設計驗證知識相關的人來講吸引力還是蠻大的,有點像我們國內(nèi)的一生一芯計劃。

當然也不是任何人都能參加這個項目,要想搭上流片的便車還需要滿足一些條件,比如必須采用SkyWater 的Open PDK(130nm),項目必須在GitHub上公開等。對于其他的一些條件感興趣的朋友可以在他們網(wǎng)站搜索。

我們今天主要看看他的一些開源項目。

前面我有篇文章提到的Raven項目就是他們的作品之一。

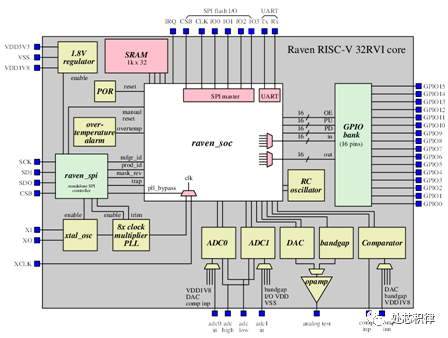

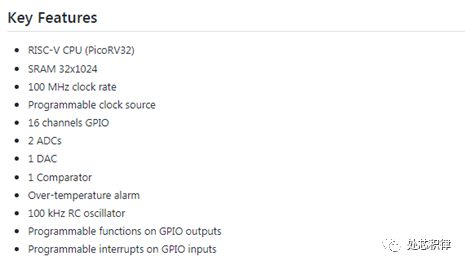

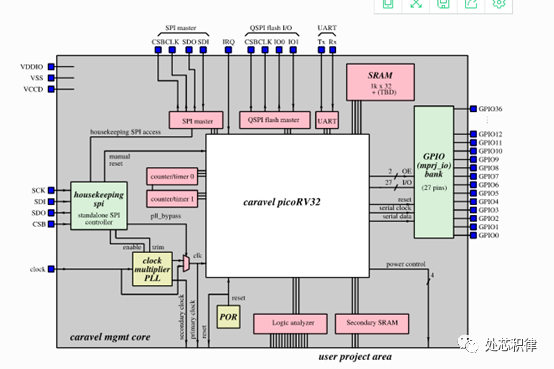

Raven這是一款開源的SOC芯片,這款芯片的主要功能見下圖。

這個開源半導體項目使用基于開源工具的Efabless設計流程,在不到三個月的時間里就實現(xiàn)了從設計開始到完成。

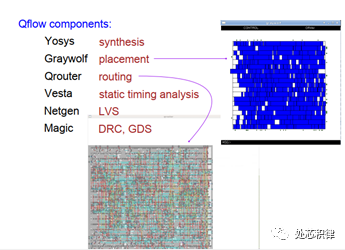

Raven完全由開源EDA進行開發(fā)然后實行流片。這里的仿真,綜合,布局布線,靜態(tài)時序分析等等都是由開源軟件完成。

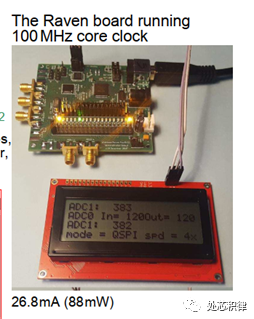

Efabless已經(jīng)成功地在100MHz下對Raven進行了測試,該設計理論上應該能夠在高達150MHz的頻率下運行。

如果作為學習的話,Raven這是一款非常好的項目。

除了這個項目,我也稍微看了下efabless上其他的項目,數(shù)了數(shù)居然有100多個,項目涉及RISCV,F(xiàn)PU,AES,以及諸多的模擬項目。

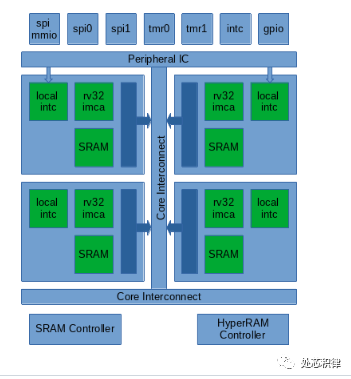

如果你對多核感興趣,那么下面這個clusterv-soc一定適合你。不過我看了一下他的git庫,只有verilog源代碼,對于仿真環(huán)境目前還沒加進去。

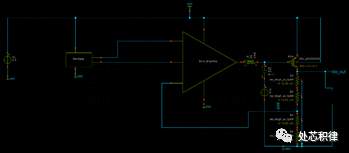

如果你對模擬芯片項目感興趣,那么LDO應該能滿足你的要求。這個項目的資料比較全。

如果你嫌棄raven還不夠復雜的話,那么caravel一定能滿足你對復雜性的要求。caravel相較于Raven外設更多,核也替換掉了。

審核編輯:劉清

-

EDA工具

+關注

關注

4文章

268瀏覽量

31844 -

SoC芯片

+關注

關注

1文章

615瀏覽量

34955

原文標題:Efabless 開源項目介紹

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

設計的一款搭載TPA3116的擴音器,有非常小聲的POP怎么解決?

如果設計一款桌面款的機器玩具,最吸引人的外觀與功能要有哪些?

化工防爆平板款式推薦!防爆平板電腦哪款好

一款實現(xiàn)PLC擴展CANFD的好工具 — PXB-6020D協(xié)議轉換器

合科泰NMOS管HKTD20N06的應用場景

項目分享 | 小熊派DIY一款指紋門鎖

TPA2012D2做一款藍牙耳機,底噪很大是怎么回事?

設計一款基于opa847的高通濾波器,仿真達不到效果怎么解決?

【ZH7463】分享一款國產(chǎn)的DCDC降壓芯片最大60V耐壓1A輸出

開源項目!設計一款智能手語翻譯眼鏡

如何挑選一款性價比高的家用路由器

如何設計一款四輪智能小車

分享一款非常好的項目Raven

分享一款非常好的項目Raven

評論