為了將ZYNQ的PS測的兩個核運行頻率提升到1GHZ,同時正確的配置我的時鐘定時器以及時間戳,需要了解ZYNQ的時鐘管理系統(tǒng)和配置方法。

1.ZYNQ PS側(cè)的時鐘子系統(tǒng)及默認(rèn)配置

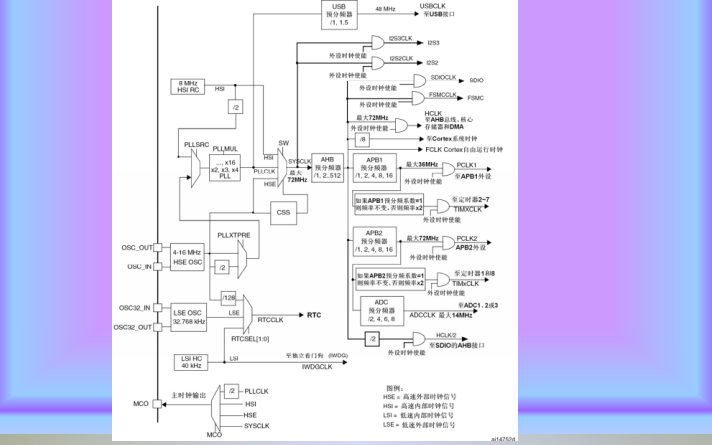

PS_CLK:系統(tǒng)晶振的時鐘,這個是PS端的的時鐘來源,經(jīng)過一個叫PLL的鎖相環(huán)功能部件,輸出到ARM PLL和I/O PLL以及DDR PLL,后續(xù)的子部件均由這三個時鐘源輸出。

這里對于cpu的時鐘源選擇,由寄存器ARM_CLK_CTRL(0XF8000120)控制,該寄存器時鐘源選擇的描述如下:

這里cpu的時鐘源可以選擇是IO還是DDR還是ARM的PLL,關(guān)于CPU后續(xù)時鐘的配置,cpu6x4x3x2x1x這些時鐘的配置,有一張更清晰的圖,如下:

這里經(jīng)過選擇以后,可以控制輸出到arm端的分頻系數(shù),這個分頻系數(shù)在13:8位,然后通過24~27位,選擇是否使能cpu各個分頻的時鐘。

這里各個部件的時鐘源都是可以選擇的,比如QSPI,可以選擇是IO還是DDR還是ARM的PLL,然后再去配置自己的時鐘,在節(jié)能模式下,可以優(yōu)化時鐘的配置,達(dá)到降低功耗的目的,這里不去深究,我的目的就是正確的配置時鐘。

比如我的PS_CLK是33.3MHZ,經(jīng)過PLL的倍頻,到了1333MHZ,然后經(jīng)過6bit的可編程分頻系數(shù),也就是ARM_CLK_CTRL的13:8位,這里假設(shè)是2,這個系數(shù)只能是2,4或者更大的數(shù),不能寫1或者3.

這之后假如各個cpux的時鐘都使能了,得到的結(jié)果就是cpu6x4x = 1333MHZ/2 = 667MHZ,這也是默認(rèn)的CPU主頻,其于依照倍數(shù)關(guān)系自然可以確認(rèn)。

這里還要注意的就是有一個CLK_621_TRUE,這個是控制cpu測的各個時鐘的倍頻關(guān)系,如果設(shè)置為1,則倍頻關(guān)系為61,否則為421關(guān)系,即41,這個默認(rèn)我們都是配置621模式。

2.設(shè)置ZYNQ CPU工作在1GHZ

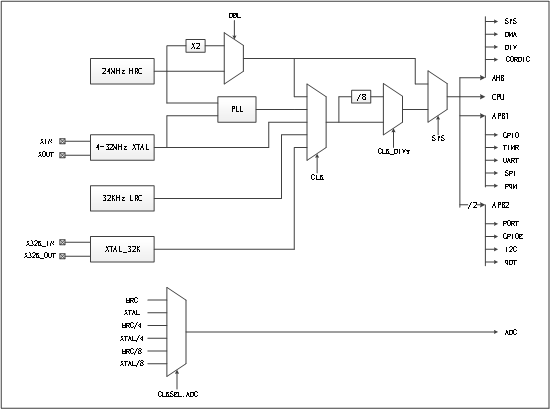

由上面的配置信息可知,要提高CPU的工作頻率,有兩個方法,第一是降低分頻系數(shù),及上圖中的6bit programmable divider,這是由ARM_CLK_CTRL控制的寄存器,第二是提高前面三個的PLL輸出頻率,由于分頻系數(shù),一般都設(shè)置為最低的2,所以要提高cpu的頻率,只有想辦法提高前面PLL的輸出頻率,默認(rèn)是輸出1333MHZ,I/O是1G,DDR是1066MHZ;如下圖中的配置:

這里對應(yīng)的fdiv是40,有沒有辦法可以設(shè)置更高的fdiv,辦法肯定是有的,zynq對時鐘部分提供了可編程的特性,在手冊中有program model的介紹,這里對fdiv有一個配置表:

各個時鐘源,無論arm pll還是io pll還是ddr pll,都需要遵照這個表中的數(shù)據(jù)去配置,加入我要將arm cpu的運行頻率提高為1GHZ,由于前面提到的divider是2,那么pll輸出過來的頻率需要為2GHZ。

由于PS_CLK為33.3,那就需要fdiv的倍頻系數(shù)為60,這樣可以達(dá)到,這個數(shù)值,芯片是支持的,只需要配置pll cp為2,pll res為4,lock cnt為250,那么配置這些只需要如下兩個寄存器:

ARM_PLL_CTRL----0xF8000100

ARM_PLL_CFG ---- 0xF8000110

其中ARM_PLL_CTRL:

其中18:12位,就是設(shè)置fdiv的值,這個值理論上最小為1最大為66,設(shè)置60已經(jīng)接近極限了,下面的幾個位是用來配置的時候重啟以及設(shè)置旁路模式,也需要關(guān)注一下;

ARM_PLL_CFG

這個寄存器就是需要按照上面的表,當(dāng)fdiv為60的時候,pll_cp和pll_res以及l(fā)ock_cnt的值填寫進去。

整體配置思路如下:

設(shè)置

ARM_CLK_CTRL----0xF8000120

設(shè)置分頻為2,選擇arm PLL,使能各個倍頻輸出

ARM_PLL_CTRL----0xF8000100

設(shè)置FDIV為60

ARM_PLL_CFG ---- 0xF8000110

設(shè)置LOCK PLL_CP PLL_RES分別為250,2,4

具體過程:

step1:確認(rèn)該寄存器可以解鎖鎖定

step2:設(shè)置以上三個寄存器

step3:將PLL設(shè)置為旁路模式

step4:重啟PLL,reset置位

step5:重啟PLL,reset清零

step6:設(shè)置為非旁路模式,使得pll輸出工作

經(jīng)過測試,我校準(zhǔn)了udelay,測試了時間戳和sleep等接口,均準(zhǔn)確:

CPU Freq Get Test!

cpu freq = 1000.00 Mhz

Sleep[tick] 5S:[5000.000000]ms

Sleep[timestamp] 1S:[994.901318]ms

udelay[100ms]:[100.012590]ms

udelay[100us]:[100.224000]us

CPU頻率的計算公式:

cpu frequency = PS_CLK*FDIV/DIVIDER*1.0

3.定時器的時鐘來源

在cortex a9的官方手冊,以及zynq7000 ug585手冊中,時鐘定時器的來源為cpu3x2x,所以當(dāng)主頻改變?yōu)?GHZ的時候,cpu2x3x的頻率也需要修改為499MHZ,這樣系統(tǒng)的定時器功能才正常。

審核編輯:劉清

-

ARM

+關(guān)注

關(guān)注

134文章

9084瀏覽量

367387 -

DDR

+關(guān)注

關(guān)注

11文章

712瀏覽量

65318 -

定時器

+關(guān)注

關(guān)注

23文章

3246瀏覽量

114720

原文標(biāo)題:ZYNQ7000 時鐘配置方法

文章出處:【微信號:ZYNQ,微信公眾號:ZYNQ】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

玩轉(zhuǎn)Zynq連載28——[ex50] 第一個Zynq系統(tǒng)工程“Hello Zynq”

使用Zynq PL結(jié)構(gòu)時鐘驅(qū)動代碼沒有反應(yīng)是為什么?

配置STM32F407系統(tǒng)時鐘的方法

如何使用HSE配置系統(tǒng)時鐘

在Vivado中配置ZYNQ的Clock Configuration時,發(fā)現(xiàn)時鐘頻率不能修改

4.3.2的ZYNQ的時鐘驅(qū)動架構(gòu)和原理解析

STM32時鐘系統(tǒng)時鐘樹和時鐘配置函數(shù)介紹及系統(tǒng)時鐘設(shè)置步驟資料

【Zynq UltraScale+ MPSoC解密學(xué)習(xí)2】Zynq UltraScale+的電源系統(tǒng)

32單片機 時鐘 HSE配置系統(tǒng)時鐘(五)

STM32入坑(七)使用HSI配置系統(tǒng)時鐘

CKS32F107xx系列時鐘系統(tǒng)具體配置方法講解

ZYNQ的時鐘管理系統(tǒng)和配置方法

ZYNQ的時鐘管理系統(tǒng)和配置方法

評論