半橋是由兩個功率器件(如MOSFET)以圖騰柱的形式連接,以中間點作為輸出,提供方波信號。這種結構在 PWM 電機控制、DC-AC逆變、電子鎮流器等場合有著廣泛的應用。而從應用領域的角度來說,其應用也十分廣泛,分布于AC-DC商用電源-服務器和工作站、消費類電子、工業電機、醫療電子、家用設備等。

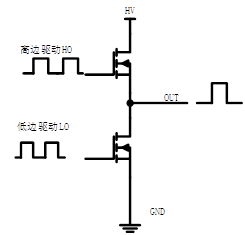

圖1:以MOSFET構成的兩種半橋結構

圖1顯示了兩種以MOSFET構成的半橋結構。左邊結構上端是P溝道MOSFET,和下端N溝道MOSFET相連,公共端漏極作為輸出;右邊結構上端是N溝道MOSFET,和下端N溝道MOSFET相連。當然,如今很多場合,特別是大功率領域,NMOS由于其更低的導通電阻RDS(ON),幾乎完全替換掉了上端的PMOS。

工作原理簡介

以圖1右邊的結構為例,高邊MOS導通時,低邊MOS不通。同樣地,低邊MOS導通時,高邊MOS不通。

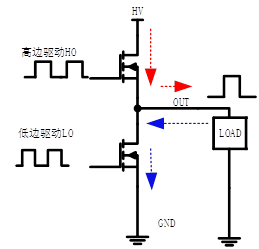

高邊MOS和低邊MOS由驅動器驅動,當驅動器的輸出HO為高時,高邊MOS導通,OUT電壓幾乎等于HV。其電流路徑為,從HV流經高邊MOS,最后流向外部負載,如圖2中紅色箭頭;

當驅動器的輸出LO為高時,低邊MOS導通,OUT電壓幾乎等于零。其電流路徑為,從負載流向低邊MOS,如圖2中藍色箭頭。

圖2:半橋結構中不同功率管導通時的電流路徑

死區時間

前面提到了半橋結構中的高低邊MOS的工作情況,高邊MOS和低邊MOS是分時導通的,輸出才能相應產生一個方波,驅動后級負載。思考一個問題,假設在高邊MOS導通的時候,低邊驅動信號LO因為某些原因,如干擾或驅動器內部其他問題等異常拉高了,此時低邊MOS也會導通,由于低邊MOS對地提供了一個更低阻抗的回路,電流直接從高邊MOS流向低邊MOS。這顯然會對輸出造成影響,嚴重的情況下,甚至可能造成MOS管失效,整個系統被徹底損壞。

因此,考慮到MOS的關斷時間和高低邊驅動器內部反向器的延時以及失配等問題,實際的驅動器都會設置死區時間。所謂的死區時間,就是上下管不允許同時導通的時間,分別位于上管關斷到下管導通,下管關斷到上管導通。當高邊MOS關斷后,死區功能被觸發,只有經過死區時間DT之后,低邊MOS才允許導通。同樣,低邊MOS關斷后,同樣要經過死區時間DT之后,高邊MOS才允許導通。

系統效率和EMI的考慮

半橋結構無論是應用于什么場景,半橋拓撲也好,還是普通的DC-DC拓撲,或者是其他的電機應用,本質上都是對能量進行變換。這就涉及到一個轉換效率的問題。就半橋結構而言,絕大部分的損耗,都集中在高低邊MOS的開關損耗。一般而言,開關管損耗包括兩個部分:

01

導通損耗

MOS管導通之后本身的導通電阻產生的損耗,其正比于MOS管的導通電阻RDS(ON),降低導通電阻就能直接降低這一部分損耗。

02

交越損耗

MOS管導通過程的損耗。

實際的MOS管由于其物理結構的原因,存在極間電容,Cgs、Cds、Cgd。這幾個電容的存在,導致整個MOS管的導通過程不能瞬間完成,實際上MOS管的導通過程也比較復雜,詳細的導通過程這里也不做介紹。如果基于簡單的模型的話,MOS管的導通過程其實就是Cgs充電的過程,Vgs緩慢上升直到超過閾值電壓Vgs(th),源漏開始導通。

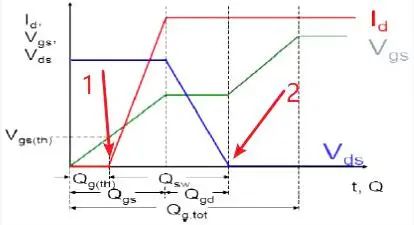

圖3:開關管導通過程的簡單模型

如圖3,源漏電流Id的上升和源漏電壓Vds的下降均有一個過程,這部分就是交越損耗。意味著,Vgs上升越慢,VDS下降就約滿,交越損耗就越大。因此,簡單來說,Vgs電壓上升速率越快,交越損耗就越低。另外,交越損耗還直接受頻率的影響,頻率越高,損耗越大。

實際上,還有一部分損耗,即驅動損耗,一般而言驅動損耗相對約導通損耗和交越損耗而言可以忽略不計,這里也不作介紹。當MOS管選定之后,其導通電阻也已經固定,導通損耗這一部分已經無法改變,要想提高效率,必須要從交越損耗這部分入手。提高驅動電壓的斜率,就是最直接的辦法。

EMC/EMI

所有的開關系統,幾乎都面臨著電磁干擾的問題。功率開關管工作在On-Off 快速循環轉換的狀態,dv/dt和di/dt都在急劇變換,因此,功率開關管既是電場耦合的主要干擾源,也是磁場耦合的主要干擾源。

在電路中的電感及寄生電感中快速的電流變化產生磁場從而產生較高的電壓尖峰:UL=L*di/dt;在電路中的電容及寄生電容中快速的電壓變化產生電場從而產生較高的電流尖峰:ic=C*du/dt。磁場和電場的噪聲與變化的電壓和電流及耦合通道如寄生的電感和電容直接相關。直觀的理解,減小電壓變化率du/dt和電流變化率di/dt及減小相應的雜散電感和電容值可以減小由于上述磁場和電場產生的噪聲,從而減小EMI干擾。

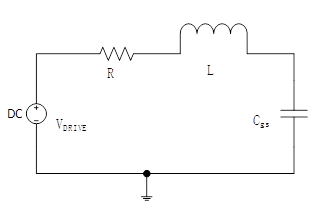

圖4:驅動到柵極的等效電路

實際的PCB由于走線等因素,必然會引入寄生電感,這些寄生電感的引入導致原本的RC一階電路直接變為RLC二階電路。如果為了盡可能的降低損耗而將激勵的斜率設置很高,則響應很有可能會出現振鈴現象,甚至于出現諧振現象,無論是上述兩種情況中的哪一種,都會帶來頭疼的EMI問題,甚至于系統不工作。因此,必須要在降低損耗和減小EMI二者之間做折衷處理。處理的方式就如圖4,增加驅動電阻R,以增加阻尼系數。一般考慮設置阻尼系數為0.707,剛好處于臨界阻尼狀態。

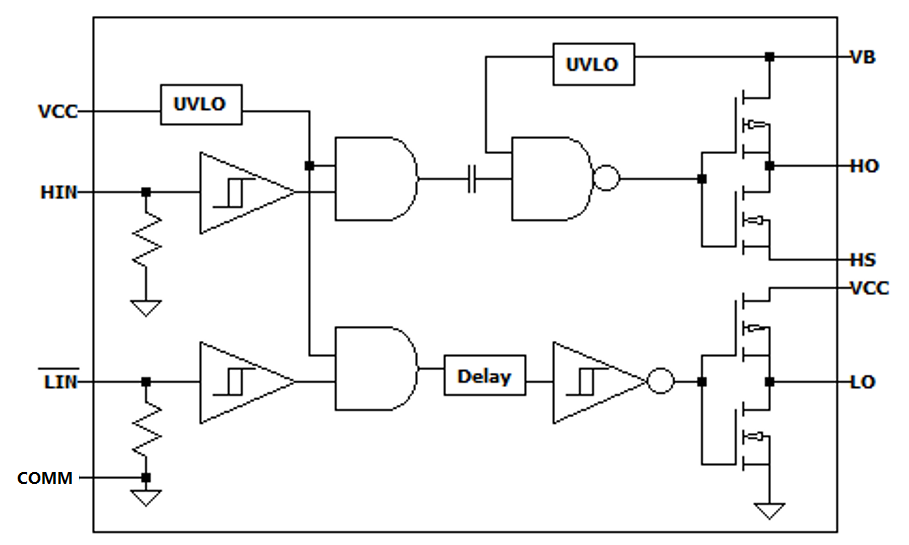

榮湃推出基于獨創的iDivider技術的半橋驅動芯片——Pai8131,很好的滿足了這些問題。為了防止高低邊MOS共通,一方面,Pai8131半橋驅動芯片提供520ns的典型死區時間,屏蔽了上下驅動電路的反向器失配帶來的影響;另外一方面,Pai8131提供最大100V/ns的共模瞬態耐受能力。當HS端對COMM端存在100V/ns的共模干擾時,驅動信號依然不會出錯,保證系統正常工作。

另外,Pai8131提供0.29A/0.6A的source/sink能力,在驅動高低邊MOS時,能夠更快的讓驅動電壓達到開啟閾值Vgs(th),讓MOS能夠更快的導通,盡可能的降低交越損耗,提高系統轉換效率。

圖5:Pai8131系統框圖

Pai8131還創新性地將容隔技術應用于高邊驅動,使用電容隔離來替代常規的level shift。在實現電平轉換的同時,還提供了極高的高低邊驅動信號之間的耐壓能力,標稱耐壓可達-700~+700V。

其他性能參數如下:

耐受負向瞬態電壓

100 dV/dt 耐受能力

柵極驅動器電源范圍10~20V

內置UVLO功能

3.3V、5V、15V邏輯電平兼容

互通預防功能

兩個通道傳播延時匹配

內部設置死區時間

Pai8131提供了常規的高性價比的NB SOIC8的小封裝,還提供一個低至400uA的靜態電流,在驅動器不工作時,保證了極低的靜態功耗。在能源問題越來越嚴重的當下,憑借其優異的性能和極低的成本,成為各相關應用領域的優先選擇。

審核編輯 :李倩

-

MOSFET

+關注

關注

147文章

7201瀏覽量

213623 -

emi

+關注

關注

53文章

3593瀏覽量

127818 -

MOS

+關注

關注

32文章

1278瀏覽量

93922

原文標題:技術課堂之十九 | 低損耗高效率高耐壓,榮湃Pai8131性能解析

文章出處:【微信號:gh_fb935efbb3e1,微信公眾號:榮湃半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用DM365的DC/DC轉換器的高Vin、高效率電源解決方案

使用帶有DVFS的DC/DC轉換器的高Vin、高效率電源解決方案

使用DM365的DCDC轉換器的高集成度、高效率電源解決方案

電機的能效等級及節能計算何為高效率電機?

AH7691D低功耗、高效率、低紋波52V轉12V 1.5A安防POE電源芯片

電機降低損耗提高效率的途徑

榮湃半導體發布全新Pai8265xx系列柵極驅動器

提高效率的DC電源模塊設計技巧

低損耗高效率高耐壓,榮湃Pai8131性能解析

低損耗高效率高耐壓,榮湃Pai8131性能解析

![[應用筆記]如何<b class='flag-5'>高效率</b>選出高能效的電感](https://file1.elecfans.com/web2/M00/07/12/wKgZombtEfCAedwkAABETvHhtXo957.png)

評論