verilog定位手段:關(guān)鍵信號(hào)統(tǒng)計(jì)

1、Verilog定位手段-關(guān)鍵信號(hào):高電平計(jì)數(shù)還是低電平計(jì)數(shù)?

在IC設(shè)計(jì)中,進(jìn)行需要對(duì)關(guān)鍵信號(hào)的特定狀態(tài)進(jìn)行計(jì)數(shù),方便debug時(shí)進(jìn)行狀態(tài)判斷。如對(duì)流控、反壓等信號(hào)進(jìn)行計(jì)數(shù)。有時(shí)候需要進(jìn)行判斷,是高電平計(jì)數(shù)還是低電平計(jì)數(shù)。

判斷標(biāo)準(zhǔn)是:選擇高電平或者低電平計(jì)數(shù),要保證能夠觀察到異常情況

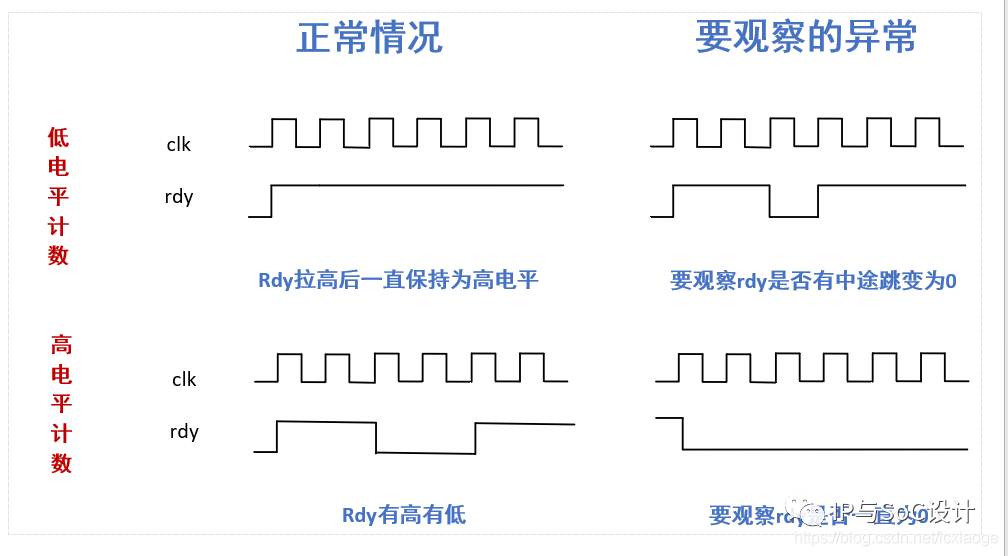

如下圖所示:

情況1:正常情況下rdy拉高后一直保持為1,不應(yīng)該會(huì)出現(xiàn)右側(cè)異常,偶爾為0,因此采用低電平計(jì)數(shù),如果出現(xiàn)異常,則計(jì)數(shù)器cnt不為0。如果采用高電平計(jì)數(shù),則很難發(fā)現(xiàn)右側(cè)異常

情況2:正常情況下rdy有高電平也有低電平,異常情況是一直為低電平,因此采用高電平計(jì)數(shù),如果計(jì)數(shù)器cnt一直保持不變,則說明rdy一直處于低電平的異常狀態(tài)。

verilog定位手段:速率計(jì)算

1、Verilog定位手段:速率統(tǒng)計(jì)?

在IC設(shè)計(jì)中,有些模塊的應(yīng)用有速率的要求,因此在FPGA階段以及樣片測試階段,需要針對(duì)應(yīng)用場景對(duì)速率進(jìn)行計(jì)算,如果在RTL設(shè)計(jì)階段能夠添加相關(guān)的統(tǒng)計(jì)寄存器,能夠高效準(zhǔn)確的計(jì)算出傳輸速率。如MAC,itlkn,DMA,都需要添加相應(yīng)的統(tǒng)計(jì)計(jì)算器計(jì)算當(dāng)前狀態(tài)的速率的相關(guān)信息,方便計(jì)算速率。

2、如何添加速率統(tǒng)計(jì)?

常見方法是:

添加寄存器,記錄一段時(shí)間內(nèi)輸入數(shù)據(jù)的個(gè)數(shù),如itlkn、MAC

添加寄存器,記錄傳輸一定數(shù)據(jù)量所需要的時(shí)鐘周期數(shù)量,如DMA

以DMA為例,簡單介紹DMA是如何添加速率統(tǒng)計(jì)寄存器的:

案例1:CPU主動(dòng)發(fā)起請(qǐng)求:

添加寄存器cycle_num_cnt,統(tǒng)計(jì)時(shí)鐘周期,從CPU發(fā)起請(qǐng)求開始、cycle_num_cnt開始每個(gè)周期加1,直到DMA模塊將數(shù)據(jù)搬運(yùn)完成,此時(shí)停止計(jì)數(shù),此時(shí)記錄的時(shí)機(jī)包含,DMA響應(yīng)請(qǐng)求信號(hào)的時(shí)間、以及DMA模塊搬運(yùn)數(shù)據(jù)的時(shí)間。

案例解析:

DMA模塊時(shí)鐘為125MHz,每個(gè)周期為8ns,CPU發(fā)起DMA請(qǐng)求,數(shù)據(jù)量為1024*128bit,DMA搬運(yùn)完成后,cycle_num_cnt保持為4812,此時(shí)平均傳輸速率為

1024*128 bit/4812*8ns=3.4Gbps

案例2:DMA主動(dòng)發(fā)起請(qǐng)求

DMA主動(dòng)發(fā)起請(qǐng)求傳輸數(shù)據(jù),可以記錄從發(fā)出第一個(gè)數(shù)據(jù)到最后一個(gè)數(shù)據(jù)所需要的時(shí)鐘周期,一次搬運(yùn)大量的數(shù)據(jù),減少測量誤差,也能獲得準(zhǔn)確的速率。

verilog定位手段:link狀態(tài)統(tǒng)計(jì)

1、Verilog定位手段:link狀態(tài)監(jiān)控

依據(jù)IEEE802.3協(xié)議設(shè)計(jì)的MAC、PCS具有l(wèi)ink_up狀態(tài)信號(hào)。PCIE接口具有鏈路訓(xùn)練成功信號(hào),此處也稱之為link_up信號(hào)。

針對(duì)link狀態(tài)、可以做如下監(jiān)控:

1.link_up狀態(tài)實(shí)時(shí)可讀

2.Link_up有效狀態(tài)計(jì)數(shù)統(tǒng)計(jì)

3.Link_up從有效跳轉(zhuǎn)到無效狀態(tài)的次數(shù)統(tǒng)計(jì)--即link_down次數(shù)統(tǒng)計(jì)

實(shí)時(shí)狀態(tài)可讀,可以獲得當(dāng)前狀態(tài)

有效狀態(tài)統(tǒng)計(jì),可以知道鏈路建立成功多次時(shí)間了

link_down次數(shù)統(tǒng)計(jì),可以知道在實(shí)際使用過程中,發(fā)生多少次link-down。

審核編輯:湯梓紅

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110143 -

定位

+關(guān)注

關(guān)注

5文章

1332瀏覽量

35407 -

dma

+關(guān)注

關(guān)注

3文章

563瀏覽量

100642

原文標(biāo)題:Verilog 定位手段

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

分享一些優(yōu)秀的verilog代碼 高質(zhì)量verilog代碼的六要素

白話科普芯片漏電定位手段

基于Verilog的車牌精確定位

PLD/FPGA硬件語言設(shè)計(jì)verilog HDL

verilog是什么_verilog的用途和特征是什么

Verilog教程之Verilog的命令格式資料說明

Verilog語法基礎(chǔ)

高質(zhì)量Verilog代碼有什么特點(diǎn)

淺談Verilog-95、Verilog-2001與System Verilog之間的區(qū)別

IC設(shè)計(jì)知識(shí)點(diǎn):verilog定位手段之關(guān)鍵信號(hào)統(tǒng)計(jì)

電廠人員定位-安全管控技術(shù)手段

養(yǎng)老院人員定位管理技術(shù)手段、作用及發(fā)展趨勢

Verilog 測試平臺(tái)設(shè)計(jì)方法 Verilog FPGA開發(fā)指南

室內(nèi)定位精確導(dǎo)航技術(shù)支持的技術(shù)手段有哪些

Verilog定位手段

Verilog定位手段

評(píng)論