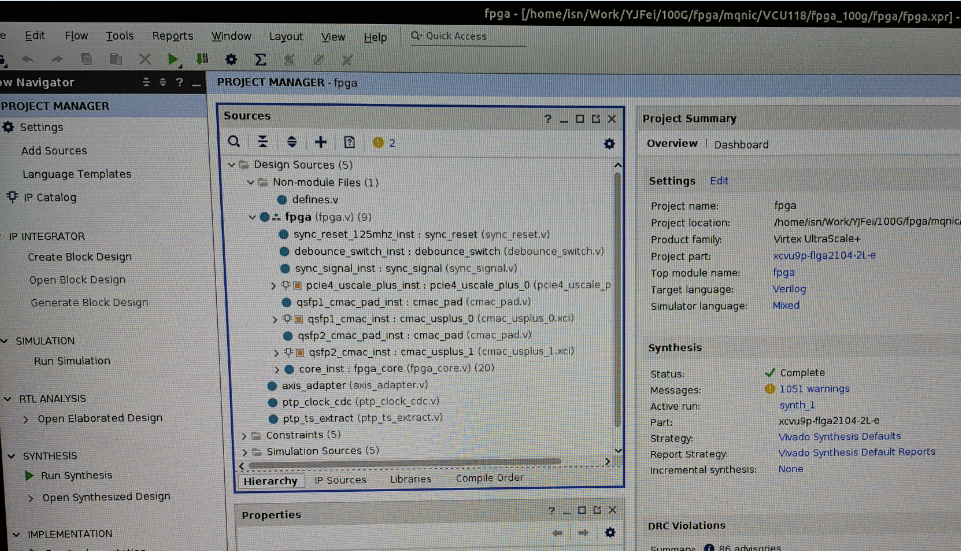

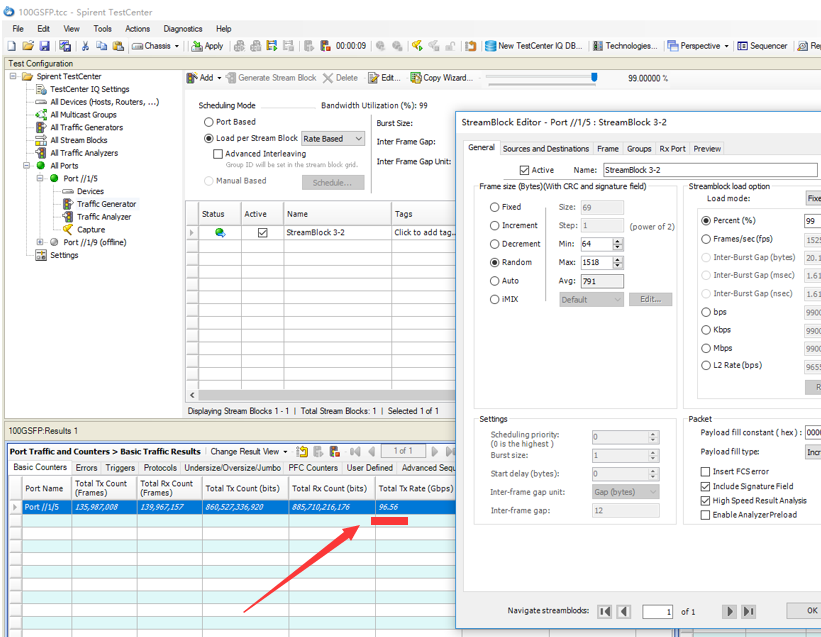

我們?cè)?a target="_blank">Linux下Vivado 2019.1版本下恢復(fù)出了Corundum基于VCU118的工程,并在VCU118板子上進(jìn)行了上板重現(xiàn)。如下圖。

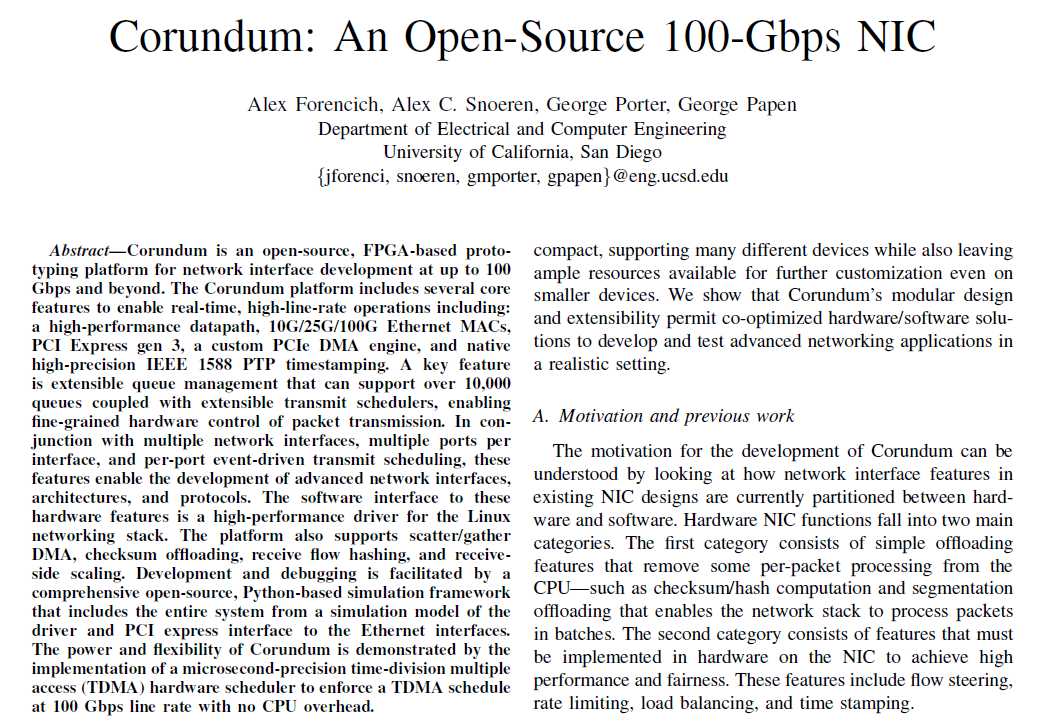

摘要

Corundum是一個(gè)基于FPGA的開源原型平臺(tái),用于高達(dá)100Gbps及更高的網(wǎng)絡(luò)接口開發(fā)。Corundum平臺(tái)包括一些用于實(shí)現(xiàn)實(shí)時(shí),高線速操作的核心功能,包括:高性能數(shù)據(jù)路徑,10G/ 25G / 100G以太網(wǎng)MAC,PCIExpress第3代,自定義PCIeDMA引擎以及本機(jī)高精確的IEEE 1588 PTP時(shí)間戳。一個(gè)關(guān)鍵功能是可擴(kuò)展隊(duì)列管理,它可以支持超過(guò)10,000個(gè)隊(duì)列以及可擴(kuò)展的傳輸調(diào)度程序,從而可以對(duì)包傳輸進(jìn)行細(xì)粒度的硬件控制。結(jié)合多個(gè)網(wǎng)絡(luò)接口,每個(gè)接口多個(gè)端口以及每個(gè)端口事件驅(qū)動(dòng)的傳輸調(diào)度,這些功能可實(shí)現(xiàn)高級(jí)網(wǎng)絡(luò)接口,體系結(jié)構(gòu)和協(xié)議的開發(fā)。這些硬件功能的軟件接口是Linux網(wǎng)絡(luò)協(xié)議棧的高性能驅(qū)動(dòng)程序。該平臺(tái)還支持分散/聚集DMA,校驗(yàn)和卸載,接收流散列和接收端縮放。一個(gè)全面的,基于Python的開放源代碼仿真框架促進(jìn)了開發(fā)和調(diào)試,該框架包括整個(gè)系統(tǒng),從驅(qū)動(dòng)程序和PCIExpress接口的仿真模型到以太網(wǎng)接口。通過(guò)實(shí)現(xiàn)微秒級(jí)時(shí)分多址(TDMA)硬件調(diào)度程序,以100Gbps的線速執(zhí)行TDMA調(diào)度,而沒有CPU開銷,證明了Corundum的強(qiáng)大功能和靈活性。

一、引言與背景

網(wǎng)絡(luò)接口控制器(NIC)是計(jì)算機(jī)與網(wǎng)絡(luò)進(jìn)行交互的網(wǎng)關(guān)。NIC構(gòu)成了軟件協(xié)議棧和網(wǎng)絡(luò)之間的橋梁,該橋梁的功能定義了網(wǎng)絡(luò)接口。網(wǎng)絡(luò)接口的功能以及這些功能的實(shí)現(xiàn)都在迅速發(fā)展。這些變化是由提高線速和支持高性能分布式計(jì)算和虛擬化的NIC功能的雙重要求所驅(qū)動(dòng)的。不斷提高的線速導(dǎo)致許多NIC功能必須在硬件而非軟件中實(shí)現(xiàn)。同時(shí),需要新的網(wǎng)絡(luò)功能,例如對(duì)多個(gè)隊(duì)列的精確傳輸控制,以實(shí)現(xiàn)高級(jí)協(xié)議和網(wǎng)絡(luò)體系結(jié)構(gòu)。

為了以實(shí)際的線速滿足對(duì)新的網(wǎng)絡(luò)協(xié)議和體系結(jié)構(gòu)的開放式開發(fā)平臺(tái)的需求,我們正在開發(fā)一種基于FPGA的開源高性能NIC原型平臺(tái)。這個(gè)稱為Corundum的平臺(tái)能夠以至少94Gbps的速度運(yùn)行,是完全開源的,并且連同其驅(qū)動(dòng)程序一起,可以在整個(gè)網(wǎng)絡(luò)協(xié)議棧中使用。該設(shè)計(jì)既便攜式又緊湊,支持許多不同的設(shè)備,同時(shí)即使在較小的設(shè)備上也留有足夠的資源用于進(jìn)一步的自定義。Corundum的模塊化設(shè)計(jì)和可擴(kuò)展性允許共同優(yōu)化的硬件/軟件解決方案在現(xiàn)實(shí)的環(huán)境中開發(fā)和測(cè)試高級(jí)網(wǎng)絡(luò)應(yīng)用程序。

A.動(dòng)機(jī)和以前的工作

通過(guò)介紹當(dāng)前如何在硬件和軟件之間劃分現(xiàn)有NIC設(shè)計(jì)中的網(wǎng)絡(luò)接口功能,可以了解開發(fā)Corundum的動(dòng)機(jī)。硬件NIC功能分為兩個(gè)主要類別。第一類包括簡(jiǎn)單的卸載功能,這些功能可以從CPU中刪除某些按數(shù)據(jù)包進(jìn)行的處理,例如校驗(yàn)和/哈希計(jì)算和分段卸載,這些功能使網(wǎng)絡(luò)協(xié)議棧可以批量處理數(shù)據(jù)包。第二類包括必須在NIC上的硬件中實(shí)現(xiàn)才能實(shí)現(xiàn)高性能和公平性的功能。這些功能包括流量控制,速率限制,負(fù)載平衡和時(shí)間戳。

一般來(lái)說(shuō),NIC的硬件功能內(nèi)置于專有的專用集成電路(ASIC)中。結(jié)合規(guī)模經(jīng)濟(jì),可以低成本實(shí)現(xiàn)高性能。但是,這些ASIC的可擴(kuò)展性受到限制,添加新硬件功能的開發(fā)周期可能既昂貴又耗時(shí)[1]。為了克服這些限制,已經(jīng)開發(fā)了各種智能NIC和軟件NIC。智能NIC通常通過(guò)提供許多可編程處理核心和硬件原語(yǔ),在NIC上提供強(qiáng)大的可編程性。這些資源可用于從主機(jī)上卸載各種應(yīng)用程序,網(wǎng)絡(luò)和虛擬化操作。但是,智能NIC不一定能夠很好地適應(yīng)高線路速率,并且硬件功能可能會(huì)受到限制[1]。

軟件NIC通過(guò)繞過(guò)大多數(shù)硬件卸載功能,在軟件中實(shí)現(xiàn)網(wǎng)絡(luò)功能來(lái)提供最大的靈活性。因此,可以快速開發(fā)和測(cè)試新功能,但是要進(jìn)行各種折衷,包括消耗主機(jī)CPU周期,并不一定要支持全線速運(yùn)行。另外,由于軟件固有的隨機(jī)中斷驅(qū)動(dòng)特性,要求精確傳輸控制的網(wǎng)絡(luò)應(yīng)用程序的開發(fā)是不可行的[2]。盡管如此,許多研究項(xiàng)目[3]–[6]通過(guò)修改網(wǎng)絡(luò)協(xié)議棧或使用諸如Data Plane Development Kit(DPDK)[7]之類的內(nèi)核繞過(guò)框架,在軟件中實(shí)現(xiàn)了新穎的NIC功能。

基于FPGA的NIC結(jié)合了基于ASIC的NIC和軟件NIC的功能:它們能夠以線速運(yùn)行并提供低延遲和精確定時(shí),同時(shí)新功能的開發(fā)周期相對(duì)較短。還開發(fā)了高性能,基于FPGA的專有NIC。例如,阿里巴巴開發(fā)了一個(gè)完全定制的基于FPGA的RDMA-onlyNIC,他們用它來(lái)運(yùn)行精密擁塞控制協(xié)議(HPCC)的硬件實(shí)現(xiàn)[8]。商業(yè)產(chǎn)品也存在,包括Exablaze [9]和Netcope [10]提供的產(chǎn)品。

不幸的是,類似于基于ASIC的NIC,可商用的基于FPGA的NIC往往具有無(wú)法修改的基本“黑匣子”功能。基本NIC功能的封閉性嚴(yán)重限制了它們?cè)陂_發(fā)新的網(wǎng)絡(luò)應(yīng)用程序時(shí)的效用和靈活性。

商業(yè)上可用的高性能DMA組件,例如Xilinx XDMA內(nèi)核和QDMA內(nèi)核,以及Atomic Rules ArkvilleDPDK加速內(nèi)核[11]都沒有提供完全可配置的硬件來(lái)控制傳輸數(shù)據(jù)流。Xilinx XDMA內(nèi)核是為計(jì)算卸載應(yīng)用程序而設(shè)計(jì)的,因此提供了非常有限的排隊(duì)功能,并且沒有簡(jiǎn)單的方法來(lái)控制傳輸調(diào)度。Xilinx QDMA內(nèi)核和Atomic Rules ArkvilleDPDK加速內(nèi)核通過(guò)支持少量隊(duì)列并提供DPDK驅(qū)動(dòng)程序而面向網(wǎng)絡(luò)應(yīng)用程序。但是,支持的隊(duì)列數(shù)量很少(XDMA內(nèi)核為2K隊(duì)列,而Arkville內(nèi)核為128個(gè)隊(duì)列)而且兩個(gè)內(nèi)核都不提供用于精確控制數(shù)據(jù)包傳輸?shù)暮?jiǎn)單方法。

另外,還有諸如NetFPGA [12]之類的開源項(xiàng)目,但是NetFPGA項(xiàng)目?jī)H提供用于基于FPGA的常規(guī)數(shù)據(jù)包處理的工具箱,而并非專門為NIC開發(fā)而設(shè)計(jì)的[P1]。此外,NetFPGA NIC參考設(shè)計(jì)利用了Xilinx XDMA內(nèi)核,該內(nèi)核并非為網(wǎng)絡(luò)應(yīng)用而設(shè)計(jì)。用Corundum替換NetFPGA板的參考NIC設(shè)計(jì)中的Xilinx XDMA內(nèi)核,將提供一個(gè)功能更強(qiáng)大,更靈活的原型開發(fā)平臺(tái)。

基于FPGA的分組處理解決方案包括實(shí)現(xiàn)網(wǎng)絡(luò)應(yīng)用程序卸載的Catapult [13]和實(shí)現(xiàn)FPGA上可重構(gòu)匹配引擎的FlowBlaze [14]。但是,這些平臺(tái)將標(biāo)準(zhǔn)的NIC功能留給了單獨(dú)的基于ASIC的NIC,并且完全作為“線下突擊”進(jìn)行操作,沒有提供對(duì)NIC調(diào)度程序或隊(duì)列的明確控制。

其他項(xiàng)目使用軟件實(shí)現(xiàn)或部分硬件實(shí)現(xiàn)。Shoal [15]描述了一種網(wǎng)絡(luò)架構(gòu),該網(wǎng)絡(luò)架構(gòu)使用自定義NIC和快速的第1層電交叉點(diǎn)交換機(jī)執(zhí)行小規(guī)模路由。Shoal是用硬件構(gòu)建的,但僅在沒有主機(jī)連接的情況下通過(guò)綜合流量進(jìn)行評(píng)估。SENIC [3]描述了基于NIC的可擴(kuò)展速率限制。單獨(dú)評(píng)估了調(diào)度程序的硬件實(shí)現(xiàn),但是系統(tǒng)級(jí)評(píng)估是在具有自定義排隊(duì)規(guī)則(qdisc)模塊的軟件中進(jìn)行的。PIEO [16]描述了一種靈活的NIC調(diào)度程序,它是在硬件中單獨(dú)進(jìn)行評(píng)估的。NDP [5]是用于數(shù)據(jù)中心應(yīng)用程序的拉模式傳輸協(xié)議。NDP已通過(guò)DPDK軟件NIC和基于FPGA的交換機(jī)進(jìn)行了評(píng)估。Loom [6]描述了一種有效的NIC設(shè)計(jì),可以使用BESS在軟件中對(duì)其進(jìn)行評(píng)估。

Corundum的開發(fā)與所有這些項(xiàng)目都不同,因?yàn)樗峭耆_源的,并且可以以實(shí)際的線速與標(biāo)準(zhǔn)主機(jī)網(wǎng)絡(luò)協(xié)議棧一起運(yùn)行。它提供了數(shù)千個(gè)傳輸隊(duì)列,并帶有可擴(kuò)展的傳輸調(diào)度程序,以實(shí)現(xiàn)對(duì)流的細(xì)粒度控制。最后我們建立了一個(gè)強(qiáng)大而靈活的開源平臺(tái),用于開發(fā)結(jié)合了硬件和軟件功能的網(wǎng)絡(luò)應(yīng)用程序。

二、實(shí)施方式

Corundum具有幾種獨(dú)特的體系結(jié)構(gòu)特點(diǎn)。首先,將硬件隊(duì)列狀態(tài)有效地存儲(chǔ)在FPGA塊RAM中,從而支持?jǐn)?shù)千個(gè)可單獨(dú)控制的隊(duì)列。這些隊(duì)列與接口相關(guān)聯(lián),每個(gè)接口可以具有多個(gè)端口,每個(gè)端口都有自己的獨(dú)立傳輸調(diào)度程序。這樣就可以對(duì)數(shù)據(jù)包傳輸進(jìn)行極其精細(xì)的控制。調(diào)度器模塊的設(shè)計(jì)是為了修改或交換的。完全可以實(shí)現(xiàn)不同的傳輸調(diào)度方案,包括實(shí)驗(yàn)調(diào)度器。再加上PTP時(shí)間同步,這樣可以實(shí)現(xiàn)基于時(shí)間的調(diào)度,包括高精度的TDMA。

Corundum的設(shè)計(jì)是模塊化且高度參數(shù)化的。可以在綜合時(shí)通過(guò)Verilog參數(shù)設(shè)置許多配置和結(jié)構(gòu)選項(xiàng),包括接口和端口計(jì)數(shù),隊(duì)列計(jì)數(shù),內(nèi)存大小,調(diào)度程序類型等。這些設(shè)計(jì)參數(shù)公開在驅(qū)動(dòng)程序讀取以確定NIC配置的配置寄存器中,使同一驅(qū)動(dòng)程序無(wú)需修改即可支持許多不同的板卡和配置。

當(dāng)前的設(shè)計(jì)支持Xilinx Ultrascale PCIe硬IP內(nèi)核接口的PCIe DMA組件。目前尚未實(shí)現(xiàn)對(duì)其他FPGA中常用的PCIe TLP接口的支持,這是未來(lái)的工作。這種支持應(yīng)該可以在更多的FPGA上進(jìn)行操作。

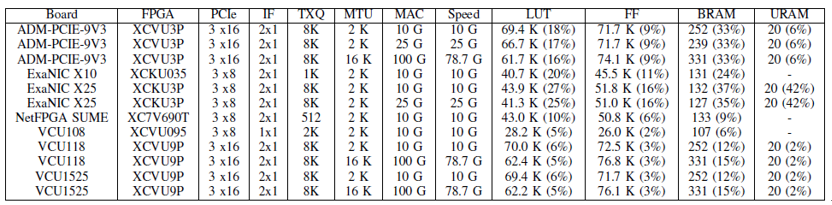

Corundum的占用空間相當(dāng)小,即使在相對(duì)較小的FPGA上,也有足夠的空間用于附加邏輯。例如,ExaNIC X10[9]的Corundum設(shè)計(jì),是一個(gè)雙端口10G設(shè)計(jì),具有PCIe gen 3 x8接口和512位內(nèi)部數(shù)據(jù)路徑,其消耗的邏輯資源不到第二小的Kintex Ultrascale FPGA(KU035)上可用邏輯資源的四分之一。表一列舉了幾個(gè)目標(biāo)平臺(tái)的資源,放在本文的最后。

本節(jié)的其余部分描述了FPGA上Corundum的實(shí)現(xiàn)。首先,給出了主要功能塊的高層概述。然后,討論了幾個(gè)獨(dú)特的體系結(jié)構(gòu)特征和功能塊的細(xì)節(jié)。

A.高層概述

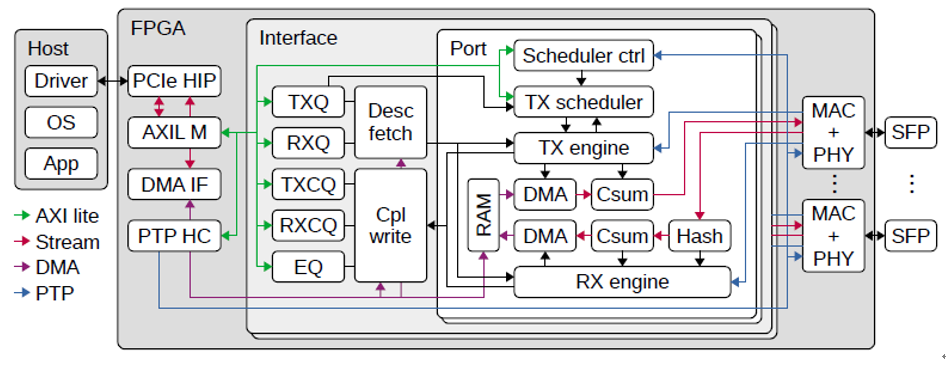

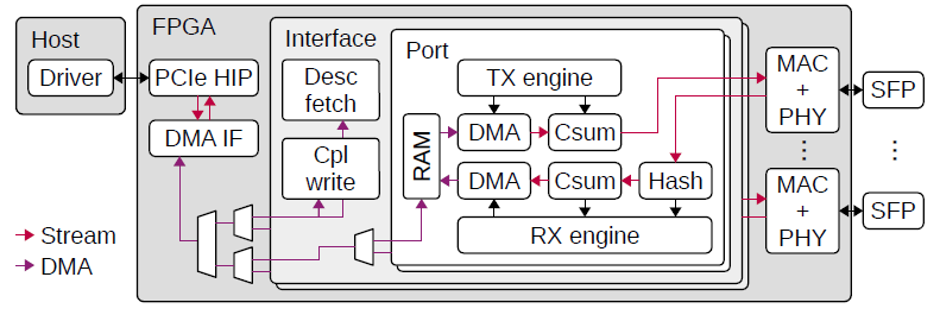

CorundumNIC的框圖如圖1所示。從較高的層次來(lái)看,NIC由3個(gè)主要的嵌套模塊組成。頂層模塊主要包含支持和接口組件。這些組件包括PCI Express硬IP內(nèi)核和DMA接口,PTP硬件時(shí)鐘以及包括MAC,PHY和相關(guān)串行器的以太網(wǎng)接口組件。頂層模塊還包括一個(gè)或多個(gè)接口模塊實(shí)例。每個(gè)接口模塊都對(duì)應(yīng)于操作系統(tǒng)級(jí)別的網(wǎng)絡(luò)接口(例如eth0)。每個(gè)接口模塊都包含隊(duì)列管理邏輯以及描述符和完成處理邏輯。隊(duì)列管理邏輯維護(hù)所有NIC隊(duì)列的隊(duì)列狀態(tài)-傳輸,傳輸完成,接收,接收完成和事件隊(duì)列。每個(gè)接口模塊還包含一個(gè)或多個(gè)端口模塊實(shí)例。每個(gè)端口模塊都提供一個(gè)到MAC的AXI流接口,并包含一個(gè)傳輸調(diào)度程序,傳輸和接收引擎,傳輸和接收數(shù)據(jù)路徑以及一個(gè)暫存RAM,用于在DMA操作期間臨時(shí)存儲(chǔ)傳入和傳出的數(shù)據(jù)包。

對(duì)于每個(gè)端口,端口模塊中的傳輸調(diào)度程序決定將哪些隊(duì)列指定用于傳輸。傳輸調(diào)度程序?yàn)榘l(fā)送引擎生成命令,這些命令協(xié)調(diào)傳輸數(shù)據(jù)路徑上的操作。調(diào)度程序模塊是一個(gè)靈活的功能塊,可以對(duì)其進(jìn)行修改或替換,以支持任意調(diào)度,這些調(diào)度可以是事件驅(qū)動(dòng)的。調(diào)度程序的默認(rèn)實(shí)現(xiàn)是簡(jiǎn)單循環(huán)。與同一接口模塊關(guān)聯(lián)的所有端口共享同一組傳輸隊(duì)列,并顯示為操作系統(tǒng)的單個(gè)統(tǒng)一接口。通過(guò)僅更改傳輸調(diào)度程序設(shè)置,而不會(huì)影響網(wǎng)絡(luò)協(xié)議棧的其余部分,這可以使流在端口之間遷移或在多個(gè)端口之間實(shí)現(xiàn)負(fù)載平衡。這種動(dòng)態(tài)的,調(diào)度程序定義的隊(duì)列到端口的映射是Corundum的獨(dú)特功能,可以使人們能夠研究新的協(xié)議和網(wǎng)絡(luò)體系結(jié)構(gòu),包括并行網(wǎng)絡(luò)(例如P-FatTree [17]和光交換網(wǎng)絡(luò),例如RotorNet [18])。和Opera [19]。

圖1.CorundumNIC的框圖。PCIe HIP:PCIe硬IP內(nèi)核; AXIL M:AXI lite Master; DMA IF:DMA接口; PTP HC:PTP硬件時(shí)鐘;TXQ:傳輸隊(duì)列管理器; TXCQ:傳輸完成隊(duì)列管理器; RXQ:接收隊(duì)列管理器; RXCQ:接收完成隊(duì)列管理器;EQ:事件隊(duì)列管理器; MAC + PHY:以太網(wǎng)媒體訪問控制器(MAC)和物理接口層(PHY)。

在接收方向,傳入的數(shù)據(jù)包通過(guò)流哈希模塊確定目標(biāo)接收隊(duì)列,并為接收引擎生成命令,這些命令協(xié)調(diào)對(duì)接收數(shù)據(jù)路徑的操作。由于同一接口模塊中的所有端口共享同一組接收隊(duì)列,因此不同端口上的傳入流將合并到同一組隊(duì)列中。還可以向NIC添加自定義模塊,以在傳入數(shù)據(jù)包通過(guò)PCIe總線之前對(duì)其進(jìn)行預(yù)處理和過(guò)濾。

NIC上的組件與多個(gè)不同的接口互連,包括AXI lite,AXI流和用于DMA操作的自定義分段存儲(chǔ)器接口,這將在后面討論。AXI lite用于從驅(qū)動(dòng)程序到NIC的控制路徑。它用于初始化和配置NIC組件,并在發(fā)送和接收操作期間控制隊(duì)列指針。AXI stream接口用于在NIC內(nèi)傳輸打包數(shù)據(jù),包括PCIe傳輸層數(shù)據(jù)包(TLP)和以太網(wǎng)幀。分段存儲(chǔ)器接口用于將PCIe DMA接口連接到NIC數(shù)據(jù)路徑以及描述符和完成處理邏輯。

大部分NIC邏輯都運(yùn)行在PCIe用戶時(shí)鐘域中,對(duì)于所有當(dāng)前的設(shè)計(jì)變體,名義上為250 MHz。異步FIFO用于與MAC接口,這些MAC在串行器中運(yùn)行,以適當(dāng)?shù)匕l(fā)送和接收時(shí)鐘域-10G為156.25 MHz,25G為390.625 MHz,100G為322.266 MHz。

以下各節(jié)描述了NIC中的幾個(gè)關(guān)鍵功能塊。

B.流水線隊(duì)列管理

Corundum NIC和驅(qū)動(dòng)程序之間的數(shù)據(jù)包數(shù)據(jù)通信通過(guò)描述符和完成隊(duì)列進(jìn)行調(diào)解。描述符隊(duì)列形成主機(jī)到NIC的通信通道,承載有關(guān)各個(gè)數(shù)據(jù)包在系統(tǒng)內(nèi)存中存儲(chǔ)位置的信息。完成隊(duì)列構(gòu)成了NIC到主機(jī)的通信通道,其中包含有關(guān)已完成的操作和關(guān)聯(lián)的元數(shù)據(jù)的信息。描述符和完成隊(duì)列被實(shí)現(xiàn)為駐留在DMA可訪問的系統(tǒng)內(nèi)存中的環(huán)形緩沖區(qū),而NIC硬件則維護(hù)必要的隊(duì)列狀態(tài)信息。此狀態(tài)信息包括指向環(huán)形緩沖區(qū)DMA地址的指針,環(huán)形緩沖區(qū)的大小,生產(chǎn)者和使用者指針以及對(duì)關(guān)聯(lián)的完成隊(duì)列的引用。每個(gè)隊(duì)列所需的描述符狀態(tài)適合128位。

Corundum NIC的隊(duì)列管理邏輯必須能夠有效地存儲(chǔ)和管理數(shù)千個(gè)隊(duì)列的狀態(tài)。這意味著隊(duì)列狀態(tài)必須完全存儲(chǔ)在FPGA的Block RAM(BRAM)或Ultra RAM(URAM)中。由于需要128位RAM,并且URAM塊為72x4096,因此存儲(chǔ)4096個(gè)隊(duì)列的狀態(tài)僅需要2個(gè)URAM實(shí)例。利用 URAM 實(shí)例可以將隊(duì)列管理邏輯擴(kuò)展到每個(gè)接口至少處理 32,768 個(gè)隊(duì)列。

為了支持高吞吐量,NIC必須能夠并行處理多個(gè)描述符。因此,隊(duì)列管理邏輯必須跟蹤多個(gè)正在進(jìn)行的操作,并在操作完成時(shí)向驅(qū)動(dòng)程序報(bào)告更新的隊(duì)列指針。跟蹤進(jìn)程中操作所需的狀態(tài)比描述符狀態(tài)小得多,因此可以將其存儲(chǔ)在觸發(fā)器和分布式RAM中。

NIC設(shè)計(jì)使用兩個(gè)隊(duì)列管理器模塊:queue_manager用于管理主機(jī)到NIC的描述符隊(duì)列,而cpl_queue_manager用于管理NIC到主機(jī)的完成隊(duì)列。除了指針處理,填充處理和門鈴/事件生成方面的一些細(xì)微差別外,這些模塊相似。由于相似之處,本節(jié)將僅討論queue_manager模塊的操作。

用于存儲(chǔ)隊(duì)列狀態(tài)信息的BRAM或URAM陣列對(duì)于每個(gè)讀取操作都需要幾個(gè)延遲周期,因此queue_manager是使用流水線結(jié)構(gòu)構(gòu)建的,以促進(jìn)多個(gè)并發(fā)操作。流水線支持四種不同的操作:寄存器讀取,寄存器寫入,出隊(duì)/入隊(duì)請(qǐng)求和出隊(duì)/入隊(duì)提交。通過(guò)AXI lite接口進(jìn)行的寄存器訪問操作使驅(qū)動(dòng)程序可以初始化隊(duì)列狀態(tài),并提供指向已分配的主機(jī)內(nèi)存的指針,以及在正常操作期間訪問生產(chǎn)者和使用者指針。

C.發(fā)送調(diào)度程序

Corundum NIC中使用的默認(rèn)傳輸調(diào)度程序是在tx_scheduler_rr模塊中實(shí)現(xiàn)的簡(jiǎn)單循環(huán)調(diào)度程序。調(diào)度器向發(fā)送引擎發(fā)送命令,從NIC傳輸隊(duì)列中啟動(dòng)傳輸操作。循環(huán)調(diào)度器包含所有隊(duì)列的基本隊(duì)列狀態(tài),一個(gè)FIFO用于存儲(chǔ)當(dāng)前活動(dòng)隊(duì)列并執(zhí)行循環(huán)調(diào)度,一個(gè)操作表用于跟蹤進(jìn)程中的傳輸操作。

與隊(duì)列管理邏輯類似,循環(huán)傳輸調(diào)度程序還將隊(duì)列狀態(tài)信息存儲(chǔ)在FPGA上的BRAM或URAM中,以便可以擴(kuò)展以支持大量隊(duì)列。傳輸調(diào)度程序還使用處理流水線來(lái)隱藏內(nèi)存訪問延遲。

傳輸調(diào)度器模塊具有四個(gè)主要接口:AXI lite寄存器接口和三個(gè)stream接口。AXI lite接口允許驅(qū)動(dòng)程序更改調(diào)度程序參數(shù)并啟用/禁用隊(duì)列。當(dāng)驅(qū)動(dòng)程序?qū)?shù)據(jù)包排隊(duì)發(fā)送時(shí),第一個(gè)流接口從隊(duì)列管理邏輯提供門鈴事件。第二個(gè)流接口將由調(diào)度器生成的傳輸命令攜帶到發(fā)送引擎。每個(gè)命令都包含要發(fā)送的隊(duì)列索引以及用于跟蹤進(jìn)程中操作的標(biāo)簽。最終的流接口將傳輸操作狀態(tài)信息返回給調(diào)度程序。狀態(tài)信息會(huì)通知調(diào)度程序已傳輸數(shù)據(jù)包的長(zhǎng)度,或者是否由于隊(duì)列為空或禁用而導(dǎo)致傳輸操作失敗。

傳輸調(diào)度程序模塊可以擴(kuò)展或替換以實(shí)現(xiàn)任意調(diào)度算法。這使Corundum可用作評(píng)估實(shí)驗(yàn)調(diào)度算法的平臺(tái),包括SENIC [3],Carousel [4],PIEO [16]和Loom [6]中提出的算法。還可能向發(fā)射調(diào)度器模塊提供其他輸入,包括來(lái)自接收路徑的反饋,這些輸入可用于實(shí)現(xiàn)新協(xié)議和擁塞控制技術(shù),例如NDP [5]和HPCC [8]。將調(diào)度程序連接到PTP硬件時(shí)鐘可用于支持TDMA,TDMA可用于實(shí)現(xiàn)RotorNet [18],Opera [19]和其他電路交換體系結(jié)構(gòu)。

D.端口和接口

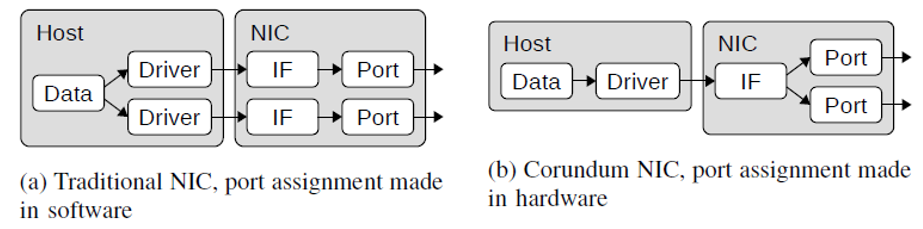

Corundum的獨(dú)特體系結(jié)構(gòu)特征是端口和網(wǎng)絡(luò)接口之間的分隔,因此多個(gè)端口可以與同一接口關(guān)聯(lián)。當(dāng)前的大多數(shù)NIC每個(gè)接口支持一個(gè)端口,如圖2a所示。當(dāng)網(wǎng)絡(luò)協(xié)議棧將數(shù)據(jù)包排隊(duì)以便在網(wǎng)絡(luò)接口上傳輸時(shí),數(shù)據(jù)包將通過(guò)與該接口關(guān)聯(lián)的網(wǎng)絡(luò)端口注入網(wǎng)絡(luò)。但是,在Corundum中,每個(gè)接口都可以關(guān)聯(lián)多個(gè)端口,因此可以在出隊(duì)時(shí)由硬件決定將數(shù)據(jù)包注入到網(wǎng)絡(luò)中的哪個(gè)端口,如圖2b所示。

圖2. NIC端口和接口架構(gòu)比較

與同一網(wǎng)絡(luò)接口模塊關(guān)聯(lián)的所有端口共享同一組傳輸隊(duì)列,并顯示為操作系統(tǒng)的單個(gè)統(tǒng)一接口。這樣,通過(guò)僅更改傳輸調(diào)度程序設(shè)置,就可以在端口之間遷移流或在多個(gè)端口之間實(shí)現(xiàn)負(fù)載平衡,而不會(huì)影響其余的網(wǎng)絡(luò)協(xié)議棧。動(dòng)態(tài)的,由調(diào)度程序定義的隊(duì)列到端口的映射使人們能夠研究新的協(xié)議和網(wǎng)絡(luò)體系結(jié)構(gòu),包括諸如P-FatTree [17]的并行網(wǎng)絡(luò)以及諸如RotorNet [18]和Opera [19]的光交換網(wǎng)絡(luò)。

E.數(shù)據(jù)路徑以及發(fā)送和接收引擎

Corundum在數(shù)據(jù)路徑中同時(shí)使用了內(nèi)存映射接口和流接口。AXI stream用于在端口DMA模塊,以太網(wǎng)MAC,校驗(yàn)和與哈希計(jì)算模塊之間傳輸以太網(wǎng)數(shù)據(jù)包數(shù)據(jù)。AXI stream還用于將PCIe硬IP內(nèi)核連接到PCIe AXI lite主模塊和PCIe DMA接口模塊。定制的分段存儲(chǔ)器接口用于將PCIe DMA接口模塊,端口DMA模塊以及描述符和完成處理邏輯連接到內(nèi)部暫存器RAM。

AXI stream接口的寬度由所需帶寬確定。除以太網(wǎng)MAC外,核心數(shù)據(jù)路徑邏輯完全在250 MHz PCIe用戶時(shí)鐘域中運(yùn)行。因此,到PCIe硬IP內(nèi)核的AXI流接口必須與硬核接口寬度匹配-PCIe Gen 3 x8為256位,PCIe Gen 3 x16為512位。在以太網(wǎng)端,接口寬度與MAC接口寬度匹配,除非250 MHz時(shí)鐘太慢而無(wú)法提供足夠的帶寬。對(duì)于10G以太網(wǎng),MAC接口是156.25 MHz的64位,可以以相同的寬度連接到250 MHz的時(shí)鐘域。對(duì)于25G以太網(wǎng),MAC接口在390.625 MHz時(shí)為64位,因此必須轉(zhuǎn)換為128位才能在250 MHz時(shí)提供足夠的帶寬。對(duì)于100G以太網(wǎng),Corundum在Ultrascale Plus FPGA上使用Xilinx 100G硬CMAC內(nèi)核。MAC接口在322.266 MHz時(shí)為512位,它以512位在250 MHz時(shí)鐘域上連接,因?yàn)樗枰源蠹s195 MHz的頻率運(yùn)行才能提供100 Gbps。

圖3. 圖1的簡(jiǎn)化版本,顯示了NIC數(shù)據(jù)路徑。

NIC數(shù)據(jù)路徑的框圖如圖3所示,它是圖1的簡(jiǎn)化版本。PCIe硬IP內(nèi)核(PCIe HIP)將NIC連接到主機(jī)。兩個(gè)AXI stream接口將PCIe DMA接口模塊連接到PCIe硬IP內(nèi)核。一個(gè)接口用于讀寫請(qǐng)求,一個(gè)接口用于讀取數(shù)據(jù)。然后,PCIe DMA接口模塊通過(guò)一組DMA接口多路復(fù)用器連接到描述符獲取模塊,完成寫入模塊,端口暫存RAM模塊以及RX和TX引擎。在朝向DMA接口的方向上,多路復(fù)用器組合了來(lái)自多個(gè)源的DMA傳輸命令。在相反的方向上,它們路由傳輸狀態(tài)響應(yīng)。它們還管理分段存儲(chǔ)器接口以進(jìn)行讀取和寫入。頂層多路復(fù)用器將描述符流量與分組數(shù)據(jù)流量結(jié)合在一起,為描述符流量提供更高的優(yōu)先級(jí)。接下來(lái),一對(duì)多路復(fù)用器組合來(lái)自多個(gè)接口模塊的流量。最后,每個(gè)接口模塊內(nèi)的一個(gè)附加多路復(fù)用器將來(lái)自多個(gè)端口實(shí)例的分組數(shù)據(jù)流量組合在一起。

發(fā)送引擎和接收引擎負(fù)責(zé)協(xié)調(diào)傳輸和接收數(shù)據(jù)包所需的操作。發(fā)送和接收引擎可以處理多個(gè)正在進(jìn)行的數(shù)據(jù)包,以實(shí)現(xiàn)高吞吐量。如圖1所示,發(fā)送和接收引擎連接到發(fā)送和接收數(shù)據(jù)路徑中的幾個(gè)模塊,包括端口DMA模塊以及哈希和校驗(yàn)和卸載模塊,以及描述符和完成處理邏輯以及時(shí)間戳接口模塊、以太網(wǎng)MAC模塊。

發(fā)送引擎負(fù)責(zé)協(xié)調(diào)數(shù)據(jù)包的傳輸操作。發(fā)送引擎處理來(lái)自傳輸調(diào)度程序的特定隊(duì)列的傳輸請(qǐng)求。使用PCIe DMA引擎進(jìn)行低級(jí)處理后,數(shù)據(jù)包將通過(guò)傳輸校驗(yàn)和模塊,MAC和PHY。一旦發(fā)送了數(shù)據(jù)包,發(fā)送引擎將從MAC接收PTP時(shí)間戳,建立完成記錄,并將其傳遞給完成寫入模塊。

與發(fā)送引擎類似,接收引擎負(fù)責(zé)協(xié)調(diào)數(shù)據(jù)包的接收操作。傳入的數(shù)據(jù)包通過(guò)PHY和MAC。在包括哈希和時(shí)間戳的底層處理之后,接收引擎將向PCIe DMA引擎發(fā)出一個(gè)或多個(gè)寫請(qǐng)求,以將數(shù)據(jù)包數(shù)據(jù)寫出到主機(jī)內(nèi)存中。寫操作完成后,接收引擎將構(gòu)建一個(gè)完成記錄,并將其傳遞給完成寫模塊。

描述符讀取和完成寫入模塊的操作類似于發(fā)送和接收引擎。這些模塊處理來(lái)自發(fā)送和接收引擎的描述符/完成讀/寫請(qǐng)求,向隊(duì)列管理器發(fā)出入隊(duì)/出隊(duì)請(qǐng)求,以獲取主機(jī)內(nèi)存中的隊(duì)列元素地址,然后向PCIe DMA接口發(fā)出請(qǐng)求以傳輸數(shù)據(jù)。完成寫入模塊還負(fù)責(zé)通過(guò)將發(fā)送和接收完成隊(duì)列排隊(duì)在適當(dāng)?shù)氖录?duì)列中并寫出事件記錄來(lái)處理事件。

F.分段內(nèi)存接口

對(duì)于PCIe上的高性能DMA,Corundum使用自定義分段存儲(chǔ)器接口。該接口被分成最大128位的段,并且整體寬度是PCIe硬IP內(nèi)核的AXI流接口寬度的兩倍。例如,將PCIe Gen 3 x16與PCIe硬核中的512位AXI流接口一起使用的設(shè)計(jì)將使用1024位分段接口,該接口分成8個(gè)段,每個(gè)段128位。與使用單個(gè)AXI接口相比,該接口提供了改進(jìn)的“阻抗匹配”,從而消除了DMA引擎中的對(duì)齊和互連邏輯中的仲裁,從而消除了背壓,從而提高了PCIe鏈路利用率。具體地說(shuō),該接口保證DMA接口可以在每個(gè)時(shí)鐘周期執(zhí)行全寬度,未對(duì)齊的讀取或?qū)懭搿4送猓褂煤?jiǎn)單的雙端口RAM(專用于在單個(gè)方向上移動(dòng)的流量)消除了讀寫路徑之間的爭(zhēng)用。

除了使用三個(gè)接口(而不是五個(gè))之外,每個(gè)網(wǎng)段的運(yùn)行方式均與AXI lite類似。一個(gè)通道提供寫地址和數(shù)據(jù),一個(gè)通道提供讀地址,一個(gè)通道提供讀數(shù)據(jù)。與AXI不同,不支持突發(fā)和重新排序,從而簡(jiǎn)化了接口邏輯。互連組件(多路復(fù)用器)負(fù)責(zé)維護(hù)操作的順序,即使在訪問多個(gè)RAM時(shí)也是如此。這些段通過(guò)單獨(dú)的流控制連接和互連排序邏輯的單獨(dú)實(shí)例彼此完全獨(dú)立地運(yùn)行。另外,操作是基于單獨(dú)的選擇信號(hào)而不是通過(guò)地址解碼進(jìn)行路由的。此功能消除了分配地址的需要,并允許使用可參數(shù)化的互連組件,這些組件以最少的配置適當(dāng)?shù)芈酚刹僮鳌?/p>

字節(jié)地址被映射到分段的接口地址上,最低的地址位確定段中的字節(jié)通道,接下來(lái)的位選擇段,最高的位確定該段的字地址。例如,在一個(gè)1024位分段接口中,分成8個(gè)128位段,最低的4個(gè)地址位將確定段中的字節(jié)通道,接下來(lái)的3位將確定該段。其余位確定該段的地址總線。

G.設(shè)備驅(qū)動(dòng)程序

Corundum NIC通過(guò)內(nèi)核模塊連接到Linux內(nèi)核網(wǎng)絡(luò)協(xié)議棧。該模塊負(fù)責(zé)初始化NIC,注冊(cè)內(nèi)核接口,為描述符和完成隊(duì)列分配DMA可訪問的緩沖區(qū),處理設(shè)備中斷以及在內(nèi)核和NIC之間傳遞網(wǎng)絡(luò)流量。

NIC使用寄存器空間公開參數(shù),包括接口數(shù)量,端口數(shù)量,隊(duì)列數(shù)量,調(diào)度程序數(shù)量,最大傳輸單元(MTU)大小以及PTP時(shí)間戳和卸載支持。驅(qū)動(dòng)程序在初始化期間讀取這些寄存器,因此它可以配置自身并注冊(cè)內(nèi)核接口以匹配NIC設(shè)計(jì)配置。這種自動(dòng)檢測(cè)功能意味著驅(qū)動(dòng)程序和NIC松耦合。當(dāng)在不同的FPGA板,不同的Corundum設(shè)計(jì)變體和不同的參數(shù)設(shè)置中使用驅(qū)動(dòng)程序時(shí),通常不需要針對(duì)核心數(shù)據(jù)路徑進(jìn)行修改。

H.仿真框架

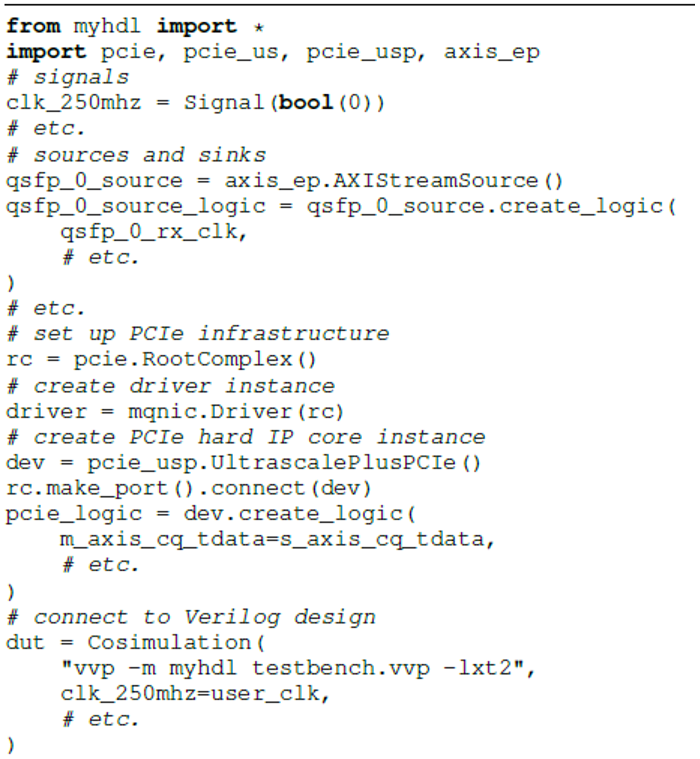

包含了一個(gè)廣泛的基于Python的開源仿真框架,以評(píng)估完整設(shè)計(jì)。該框架使用Python庫(kù)MyHDL構(gòu)建,并包括PCI Express系統(tǒng)基礎(chǔ)架構(gòu),PCI Express硬IP內(nèi)核,NIC驅(qū)動(dòng)程序和以太網(wǎng)接口的仿真模型。該仿真框架通過(guò)提供整個(gè)系統(tǒng)狀態(tài)的可視性,有助于調(diào)試完整的NIC設(shè)計(jì)。

PCIe仿真框架的核心由大約4,500行Python組成,并包括PCIe基礎(chǔ)結(jié)構(gòu)組件的事務(wù)層模型,其中包括根聯(lián)合體,功能,端點(diǎn)和交換機(jī)以及高級(jí)功能,包括配置空間,功能,總線枚舉,根聯(lián)合體內(nèi)存分配,中斷和其他功能。其他模塊由另外4,000行Python組成,提供FPGA PCIe硬IP核的模型,與模擬的PCIe基礎(chǔ)設(shè)施交換事務(wù)層流量,并驅(qū)動(dòng)可連接至共同仿真的Verilog設(shè)計(jì)的信號(hào)。

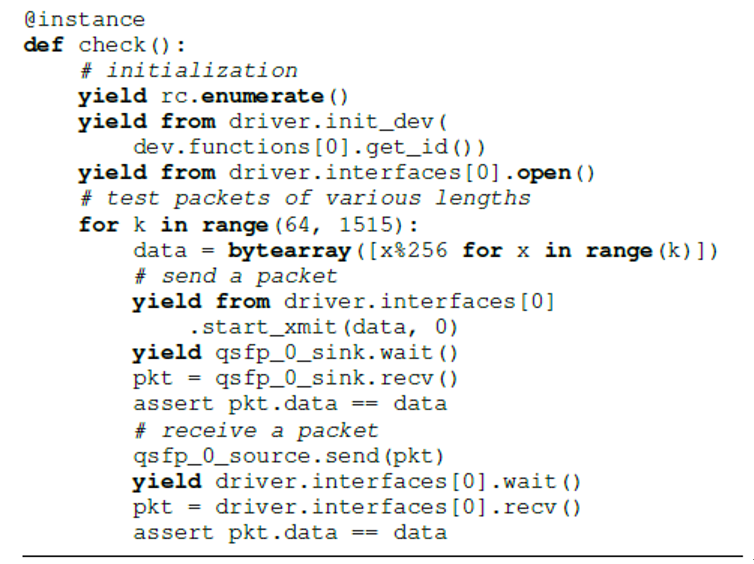

模擬Corundum需要幾行代碼來(lái)實(shí)例化和連接所有組件。清單1顯示了使用模擬框架發(fā)送和接收各種大小的數(shù)據(jù)包的簡(jiǎn)化測(cè)試臺(tái),在Icarus Verilog中共同模擬了Verilog設(shè)計(jì)。該測(cè)試平臺(tái)實(shí)例化了以太網(wǎng)接口端點(diǎn),PCIe根聯(lián)合體和驅(qū)動(dòng)程序的仿真模型,并將它們連接到協(xié)同仿真的設(shè)計(jì)。然后,它初始化PCIe基礎(chǔ)結(jié)構(gòu),初始化驅(qū)動(dòng)程序模型,并發(fā)送,接收和驗(yàn)證幾個(gè)不同長(zhǎng)度的測(cè)試數(shù)據(jù)包。

三、結(jié)果

在安裝在Dell R540服務(wù)器(雙Xeon 6138)中的Alpha Data ADM-PCIE-9V3板上評(píng)估了CorundumNIC的100G變體,該主板連接到同一服務(wù)器上的最新商業(yè)級(jí)NIC(Mellanox ConnectX-5)用QSFP28直接連接銅纜。還對(duì)在同一臺(tái)計(jì)算機(jī)上安裝的另外兩個(gè)Mellanox ConnectX-5 NIC進(jìn)行了評(píng)估,以進(jìn)行比較。最多使用八個(gè)iperf3實(shí)例來(lái)飽和鏈接。

清單1. NIC測(cè)試臺(tái)的縮寫。包括設(shè)置PCIe,以太網(wǎng)接口和驅(qū)動(dòng)程序模型,初始化模擬的PCIe總線和驅(qū)動(dòng)程序以及發(fā)送和接收測(cè)試數(shù)據(jù)包。為簡(jiǎn)潔起見,大多數(shù)信號(hào)已刪除。

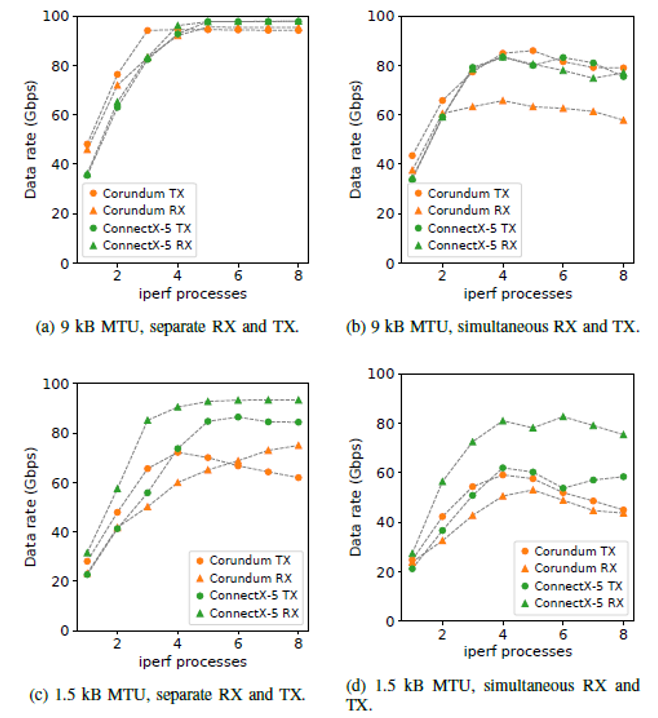

圖4.Corundum和MellanoxConnectX-5的TCP吞吐量比較。

為了將Corundum與Mellanox ConnectX-5的性能進(jìn)行比較,最初將兩個(gè)NIC的最大傳輸單位(MTU)配置為9000字節(jié)。對(duì)于此配置,Corundum可以分別實(shí)現(xiàn)95.5 Gbps RX和94.4 Gbps TX(圖4a)。在相同條件下,Mellanox ConnectX-5 NIC的RX和TX均達(dá)到97.8 Gbps。當(dāng)運(yùn)行iperf的其他實(shí)例同時(shí)在兩個(gè)方向上使鏈接飽和時(shí),Corundum的性能將下降到65.7 Gpbs RX和85.9 Gbps TX(圖4b)。對(duì)于現(xiàn)有的測(cè)試臺(tái),對(duì)于RX和TX,Mellanox NIC的性能也下降到83.4 Gbps。在全雙工模式下,Corundum和ConnectX-5的性能下降都表明軟件驅(qū)動(dòng)程序可能是導(dǎo)致性能下降的重要原因。具體來(lái)說(shuō),當(dāng)前版本的驅(qū)動(dòng)程序僅支持Linux內(nèi)核網(wǎng)絡(luò)協(xié)議棧。支持諸如DPDK之類的內(nèi)核繞過(guò)框架的參考設(shè)計(jì)是未來(lái)工作的目標(biāo)。此設(shè)計(jì)應(yīng)提高全雙工模式的性能,并可針對(duì)特定應(yīng)用進(jìn)行定制。

圖4c和4d比較了1500字節(jié)MTU的性能。對(duì)于這種情況,Corundum可以分別實(shí)現(xiàn)75.0 Gbps RX和72.2 Gbps TX(圖4c),同時(shí)實(shí)現(xiàn)53.0 Gbps RX和57.6 Gbps TX(圖4d)。隨著iperf實(shí)例數(shù)量的增加,圖4c中TX和RX之間Corundum的性能差異是由進(jìn)程內(nèi)傳輸數(shù)據(jù)包數(shù)量的限制以及PCIe往返延遲引起的。通過(guò)將進(jìn)程內(nèi)傳輸操作的數(shù)量從8個(gè)增加到16個(gè),可以驗(yàn)證這一點(diǎn)。這將速率從65.6 Gbps RX和45.7 Gbps TX提高到了圖4c中所示的75.0 Gbps RX和72.2 Gbps TX速率。為了進(jìn)行比較,在相同條件下,Mellanox ConnectX-5 NIC可以分別實(shí)現(xiàn)93.4 Gbps的RX和86.5 Gbps的TX,同時(shí)實(shí)現(xiàn)82.7 Gbps的RX和62.0 Gbps的TX。

為了測(cè)試PTP時(shí)間戳的性能,將兩個(gè)10G模式的CorundumNIC連接到用作PTP邊界時(shí)鐘的Arista 40G數(shù)據(jù)包交換機(jī)。NIC配置為輸出源自PTP時(shí)間的固定頻率信號(hào),該信號(hào)由示波器捕獲。在啟用PTP時(shí)間戳的情況下實(shí)施Corundum時(shí),可以將硬件時(shí)鐘與linux ptp同步到50 ns以上。鏈路飽和時(shí),時(shí)間同步性能不變。

四、案例研究:時(shí)分多址(TDMA)

精確的網(wǎng)絡(luò)準(zhǔn)入控制是高線路速率下的關(guān)鍵網(wǎng)絡(luò)功能。Corundum提供了數(shù)千個(gè)傳輸隊(duì)列,可用于在多個(gè)終端主機(jī)之間同步的精細(xì)時(shí)間范圍內(nèi)分離和控制傳輸數(shù)據(jù)。此功能提供了一個(gè)獨(dú)特的工具箱,可用于開發(fā)新的強(qiáng)大的NIC功能。確定要實(shí)現(xiàn)的網(wǎng)絡(luò)功能以及這些功能對(duì)網(wǎng)絡(luò)性能的影響是一個(gè)活躍的研究領(lǐng)域[3]–[5],[16]。

為了演示如何將Corundum用于精確的傳輸控制,我們?yōu)門DMA實(shí)現(xiàn)了具有固定時(shí)間表的簡(jiǎn)單參考設(shè)計(jì)。從此基本設(shè)計(jì)和Corundum的模塊化結(jié)構(gòu)開始,可以實(shí)現(xiàn)針對(duì)新型網(wǎng)絡(luò)協(xié)議的自定義調(diào)度程序,這些調(diào)度程序?qū)φ麄€(gè)體系結(jié)構(gòu)的影響最小。

固定的TDMA時(shí)間表可以通過(guò)IEEE 1588 PTP在多個(gè)主機(jī)之間同步。在TDMA調(diào)度程序控制模塊的控制下,通過(guò)根據(jù)PTP時(shí)間啟用和禁用傳輸調(diào)度程序中的隊(duì)列來(lái)實(shí)現(xiàn)TDMA。隊(duì)列啟用和禁用命令在TDMA調(diào)度程序控制模塊中生成,并在TDMA調(diào)度的每個(gè)時(shí)隙的開始和結(jié)束時(shí)發(fā)送到發(fā)送調(diào)度器。TDMA調(diào)度器在時(shí)隙足夠長(zhǎng)的假設(shè)下操作,使得TDMA調(diào)度器控制模塊可以在當(dāng)前時(shí)隙期間為下一個(gè)時(shí)隙做準(zhǔn)備。另外,在每個(gè)時(shí)隙中必須有相對(duì)少量的隊(duì)列處于活動(dòng)狀態(tài),因此啟用或禁用的第一個(gè)和最后一個(gè)隊(duì)列之間的時(shí)滯較小。

TDMA調(diào)度程序控制模塊在250 MHz PCIe用戶時(shí)鐘域中運(yùn)行。結(jié)果,每個(gè)隊(duì)列花費(fèi)4 ns遍歷每個(gè)傳輸隊(duì)列以準(zhǔn)備下一個(gè)時(shí)隙(8,192個(gè)傳輸隊(duì)列總計(jì)約32.8 us)。類似地,它需要4 ns的時(shí)間來(lái)生成每個(gè)啟用或禁用命令,以發(fā)送到傳輸調(diào)度程序模塊。

A. TDMA性能

在Alpha DataADM-PCIE-9V3板上評(píng)估了具有256個(gè)傳輸隊(duì)列的100G TDMA變體的Corundum NIC,該板安裝在Dell R540服務(wù)器(雙Xeon 6138)上,連接到Mellanox ConnectX-5 NIC。使用了八個(gè)實(shí)例的iperf3來(lái)飽和鏈路,兩個(gè)網(wǎng)卡的MTU配置為9 kB。在禁用TDMA的情況下,網(wǎng)卡以94.0 Gbps的速度運(yùn)行。TDMA調(diào)度器被配置為運(yùn)行一個(gè)周期為200 μs的調(diào)度,包含兩個(gè)100 μs的時(shí)隙,在第一個(gè)時(shí)隙中啟用所有傳輸隊(duì)列,在第二個(gè)時(shí)隙中禁用。在100 Gbps的傳輸數(shù)據(jù)路徑中,11個(gè)數(shù)據(jù)包的間隔為8 μs(每個(gè)數(shù)據(jù)包11個(gè)0.72 μs),再加上1 μs來(lái)禁用所有256個(gè)隊(duì)列,Corundum可以以兩個(gè)數(shù)據(jù)包長(zhǎng)度或1.4 μs的精度控制離開網(wǎng)卡的數(shù)據(jù)。

表I 資源利用

使用200us的時(shí)間表,以10 Gbps的線速和1500字節(jié)的MTU運(yùn)行附加測(cè)試。該時(shí)間段被劃分為兩個(gè)100 us的時(shí)隙。考慮到10 Gbps的傳輸數(shù)據(jù)路徑中的32個(gè)數(shù)據(jù)包的間隔為38 us(每個(gè)數(shù)據(jù)包32 1.2 us)加上1 us以禁用所有256個(gè)隊(duì)列,Corundum可以以兩個(gè)數(shù)據(jù)包長(zhǎng)度或兩個(gè)數(shù)據(jù)包的精度控制離開NIC的數(shù)據(jù) 2.4us。

五、結(jié)論

在本文中,我們介紹了Corundum,這是一種基于FPGA的開源高性能NIC。初始設(shè)計(jì)的測(cè)量性能提供了現(xiàn)實(shí)的線速,足以開發(fā)和測(cè)試新的網(wǎng)絡(luò)應(yīng)用程序。現(xiàn)有的和計(jì)劃中的開源參考設(shè)計(jì)可實(shí)現(xiàn)自定義和進(jìn)一步的性能改進(jìn)。這些功能為網(wǎng)絡(luò)研究和開發(fā)提供了強(qiáng)大的原型平臺(tái),包括基于NIC的調(diào)度程序,例如SENIC [3],Carousel [4],PIEO [16]和Loom [6],新協(xié)議和擁塞控制技術(shù),例如 NDP [5]和HPCC [8]。Corundum還啟用了新的并行網(wǎng)絡(luò)體系結(jié)構(gòu),例如P-FatTree [17],RotorNet [18]和Opera [19]。優(yōu)化設(shè)計(jì)以提高較小數(shù)據(jù)包大小的性能,以及基于精確數(shù)據(jù)包傳輸為新的網(wǎng)絡(luò)協(xié)議定制設(shè)計(jì)是當(dāng)前工作的目標(biāo)。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1636文章

21841瀏覽量

608495 -

模塊

+關(guān)注

關(guān)注

7文章

2750瀏覽量

48184 -

NIC

+關(guān)注

關(guān)注

0文章

23瀏覽量

12507

原文標(biāo)題:業(yè)界第一個(gè)真正意義上開源100 Gbps NIC Corundum介紹

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

開源項(xiàng)目!教你如何制作一個(gè)開源教育機(jī)械臂

開源mlops平臺(tái)好用嗎

AMD技術(shù)賦能西門子FPGA原型設(shè)計(jì)解決方案

黃鶴開源社區(qū)正式發(fā)布

高校開源開發(fā)者培養(yǎng)分論壇亮點(diǎn)前瞻

Verilog 測(cè)試平臺(tái)設(shè)計(jì)方法 Verilog FPGA開發(fā)指南

Nordic推出最新物聯(lián)網(wǎng)原型驗(yàn)證平臺(tái)Thingy:91 X

HAL庫(kù)在Arduino平臺(tái)上的使用

多平臺(tái)FPGA工程快速移植與構(gòu)建

使用FPGA構(gòu)建ADAS系統(tǒng)簡(jiǎn)易過(guò)程

快速部署原型驗(yàn)證:從子卡到調(diào)試的全方位優(yōu)化

FPGA算法工程師、邏輯工程師、原型驗(yàn)證工程師有什么區(qū)別?

基于FPGA的網(wǎng)絡(luò)加速設(shè)計(jì)實(shí)現(xiàn)

一個(gè)基于FPGA的開源原型平臺(tái)

一個(gè)基于FPGA的開源原型平臺(tái)

評(píng)論