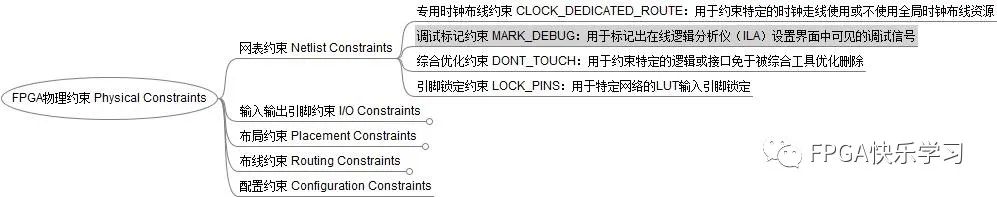

概述

網表約束MARK_DEBUG可應用在源碼中的任意一個網絡信號上,被施加該約束的網絡信號在調試界面中可見,從而方便在線調試時快速定位該信號,提升調試效率。話不多說,下面以FPGA中的在線邏輯分析儀(ILA)的調試實踐為例,讓大家感受一下網表約束MARK_DEBUG的妙用。

工程實踐

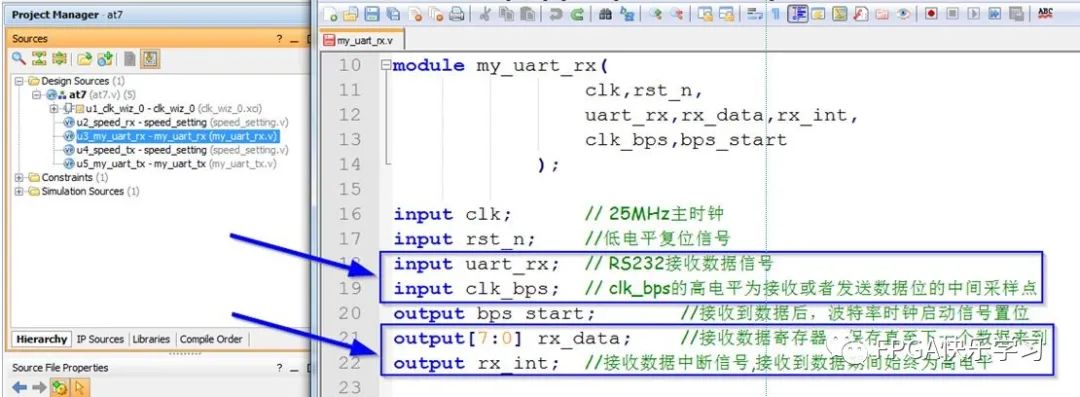

以STAR FPGA開發板中的at7_ex10工程為例,這個工程實現UART傳輸的loopback功能。該實例中使用在線邏輯分析儀希望探測到FPGA端接收并進行串并轉換過程中所設計的一些主要信號。

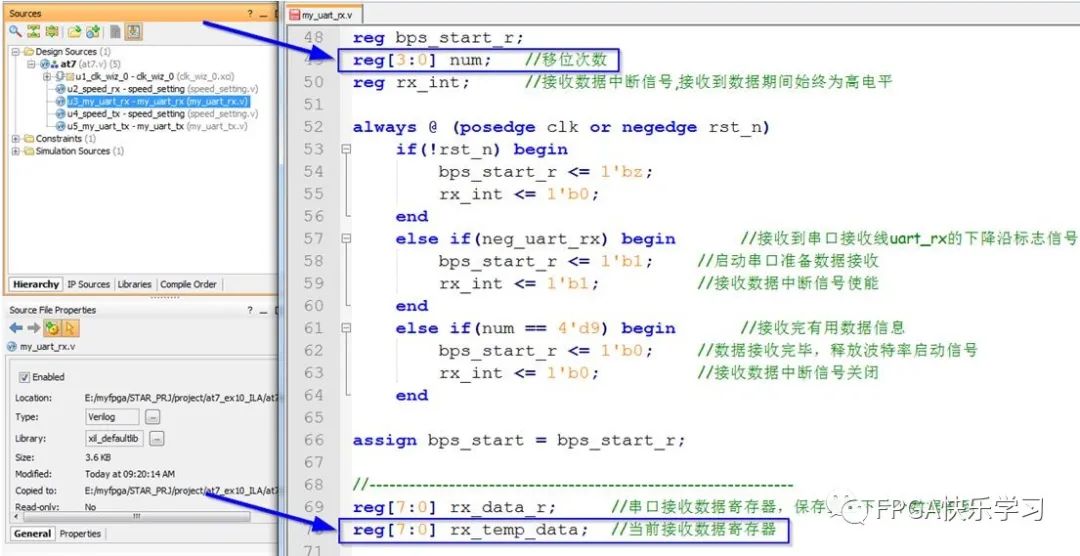

首先需要找出待探測的信號。如圖1和圖2所示,在my_uart_rx.v模塊中,uart_rx、clk_bps、rx_data、rx_int、num、rx_temp_data是需要探測監控的信號。

圖1 識別需要進行探測的信號1

圖2識別需要進行探測的信號2

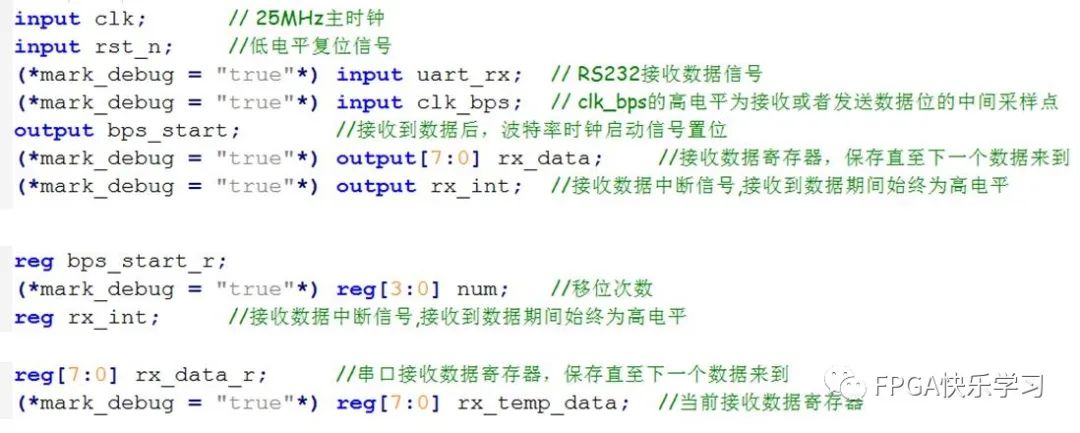

如圖3所示,在待探測信號定義申明前面增加語句:(*mark_debug= "true"*)。當然了,如果后續不探測這個信號了,直接修改“true”為“false”就可以。

圖3 標注需要探測的信號

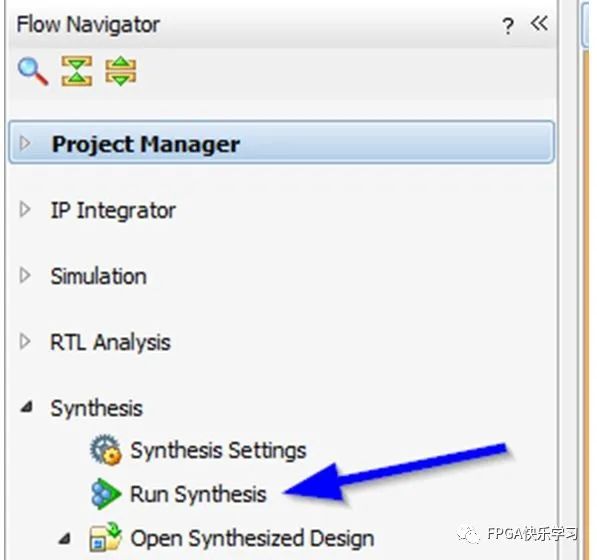

完成對探測信號的mark_debug標記后,如圖4所示,點擊“Synthesis à Run Synthesis”對工程進行綜合編譯。

圖4 工程的綜合編譯

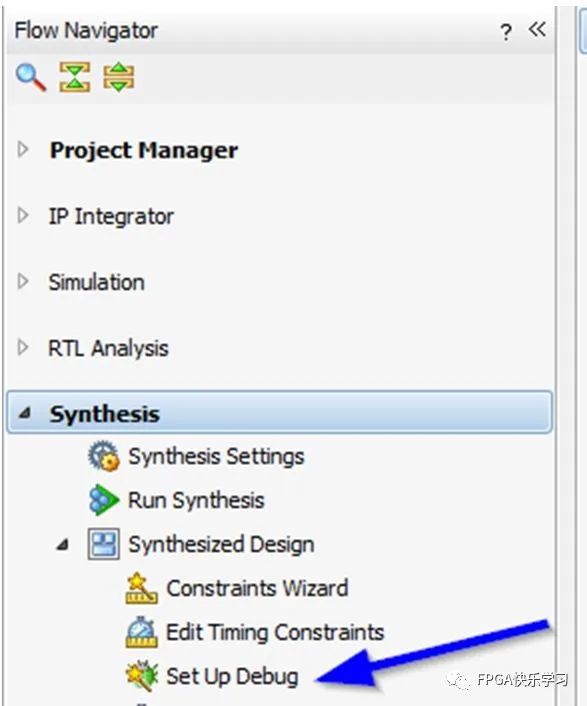

綜合編輯完成后,如圖5所示,接著點擊“Synthesis à Synthesized Design à Set Up Debug”。

圖5 Set Up Debug菜單

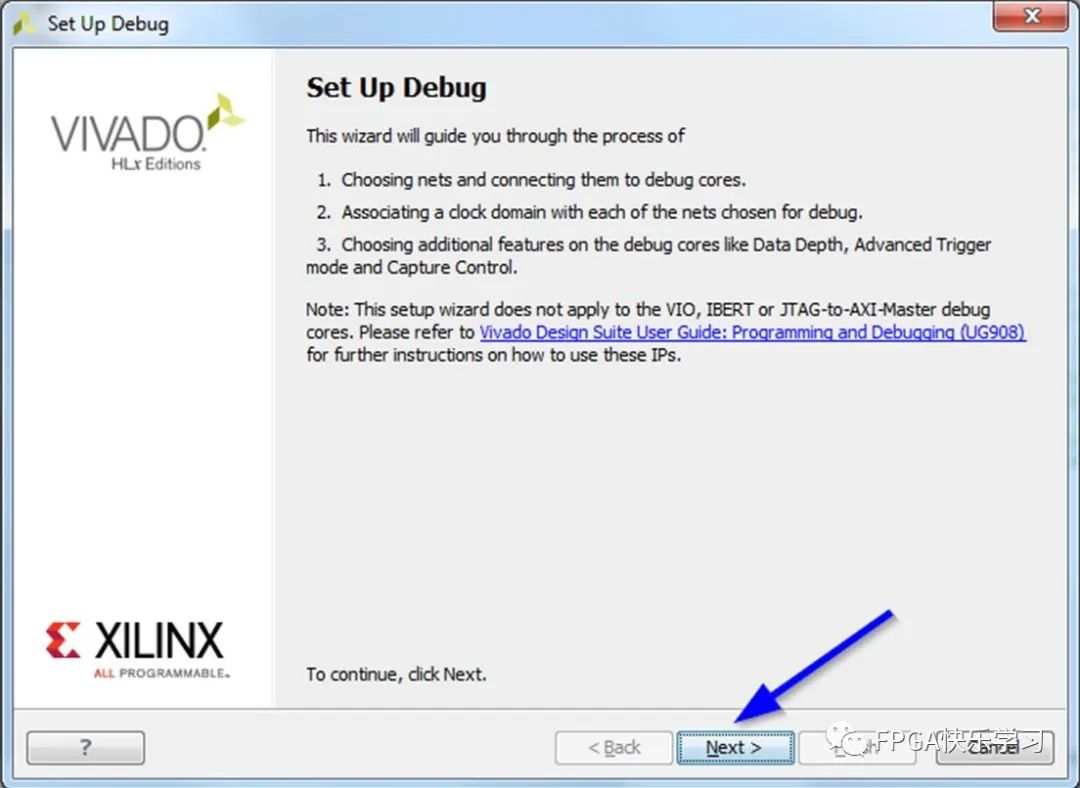

如圖6所示,點擊Next進入下一步。

圖6 Set Up Debug Wizard頁面

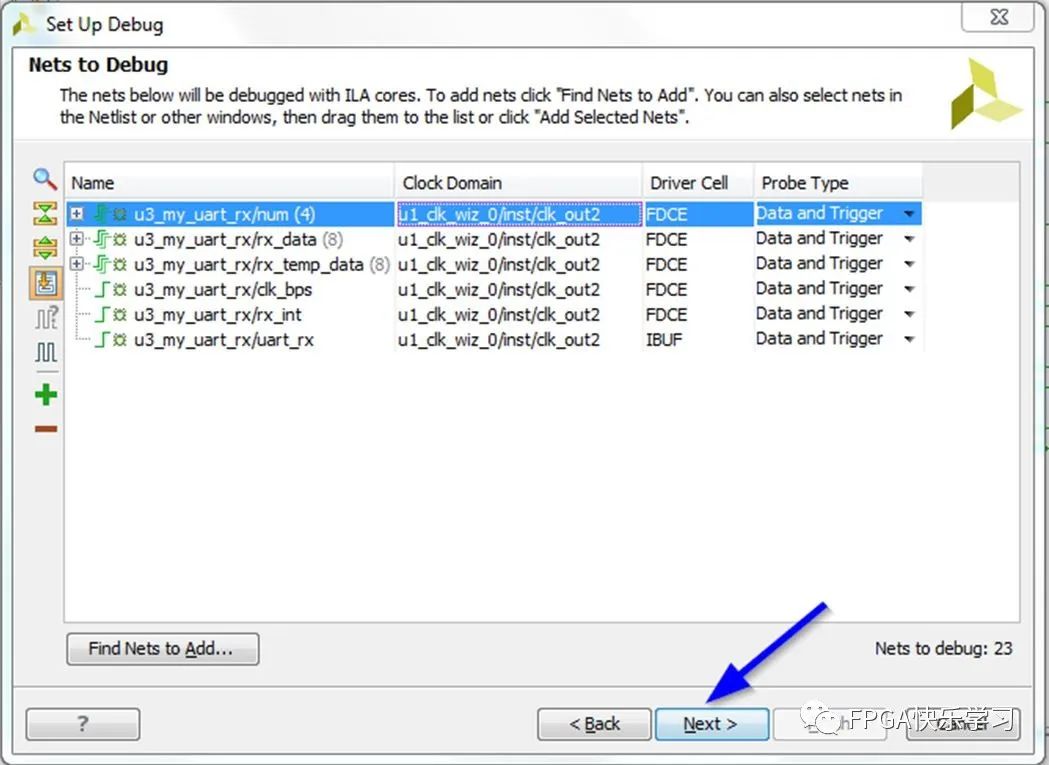

如圖7所示,Nets to Debug界面顯示的信號正是我們在前面的工程源碼中標記了(*mark_debug = "true"*)的信號。如果沒有被標記過的信號,我們希望添加到Nets to Debug界面中,就要點擊Find Netsto Add…按鈕逐個查找并添加了,效率要明顯低于直接在工程源碼中事先標記。對這些調試信號做采樣和觸發屬性設置后,點擊Next進入下一頁面。

圖7 Nets to Debug頁面

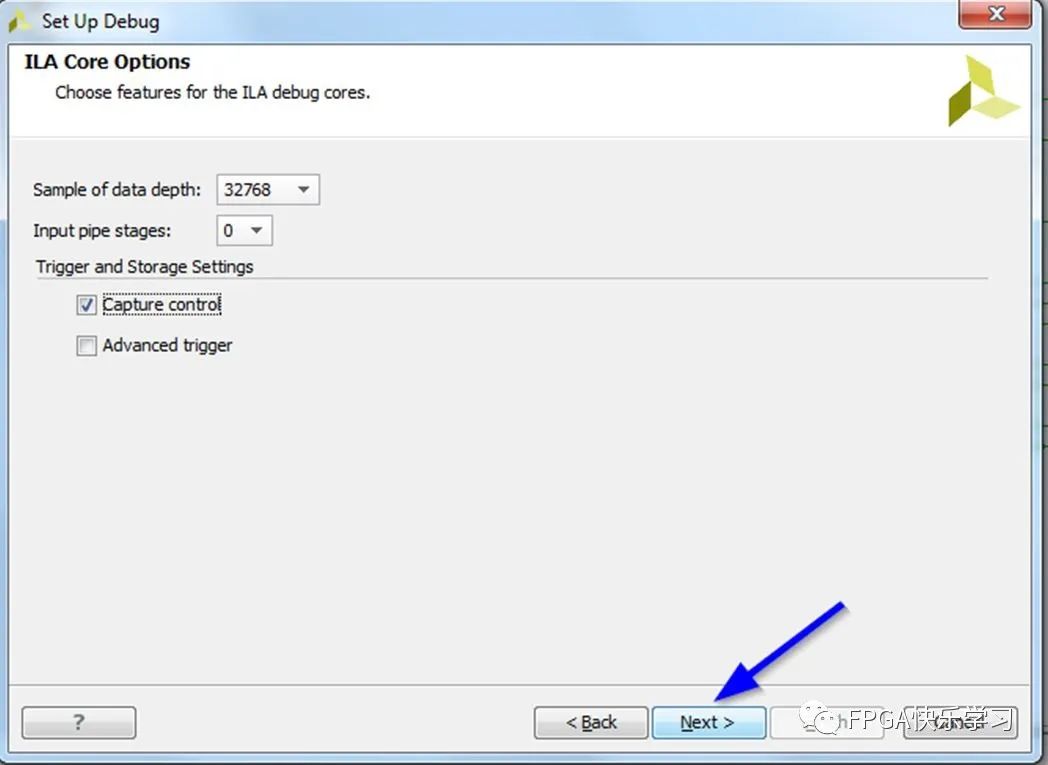

如圖8所示,ILA Core Options頁面中,可以設定探測信號的采樣深度、緩存寄存器等級和信號采集觸發相關控制選項。完成設置后,點擊Next進入下一頁面。

圖8 ILA CoreOptions頁面

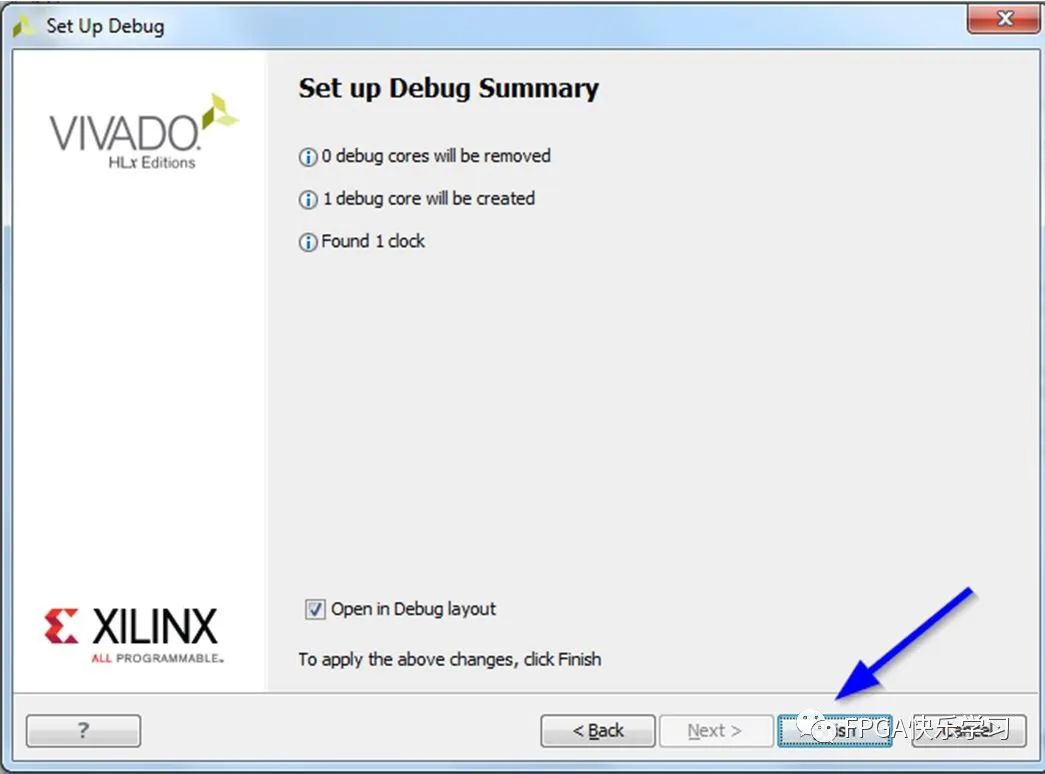

如圖9所示,Set up Debug Summary中點擊Finish完成設置。

圖9 Set upDebug Summary頁面

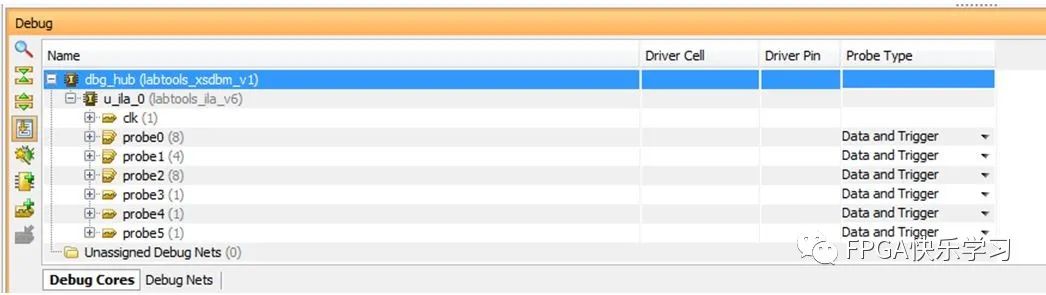

此時,如圖10所示,所有的探測信號出現在了Debug窗口中。

圖10 Debug窗口

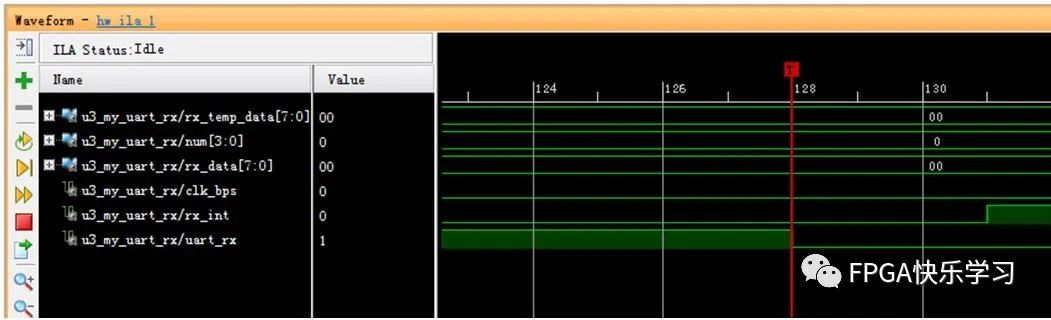

接著,重新對工程進行編譯,將產生的比特流燒錄到FPGA器件中,最終便能捕捉到如圖11所示的實際的信號波形。

圖11 觸發位置的波形

審核編輯 :李倩

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603013 -

源碼

+關注

關注

8文章

639瀏覽量

29185 -

約束

+關注

關注

0文章

82瀏覽量

12728

原文標題:物理約束實踐:網表約束MARK_DEBUG

文章出處:【微信號:FPGA快樂學習,微信公眾號:FPGA快樂學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時序約束一主時鐘與生成時鐘

常用時序約束使用說明-v1

與非門構成的基本RS觸發器的約束條件是什么

SR鎖存器有約束項的原因

兩種SR鎖存器的約束條件

加法進位鏈的手動約束

Xilinx FPGA編程技巧之常用時序約束詳解

時序約束實操

Xilinx FPGA的約束設置基礎

Xilinx FPGA編程技巧之常用時序約束詳解

機器人運動學中的非完整約束與運動模型推導

FPGA物理約束之布局約束

物理約束實踐:網表約束MARK_DEBUG

物理約束實踐:網表約束MARK_DEBUG

評論