前言

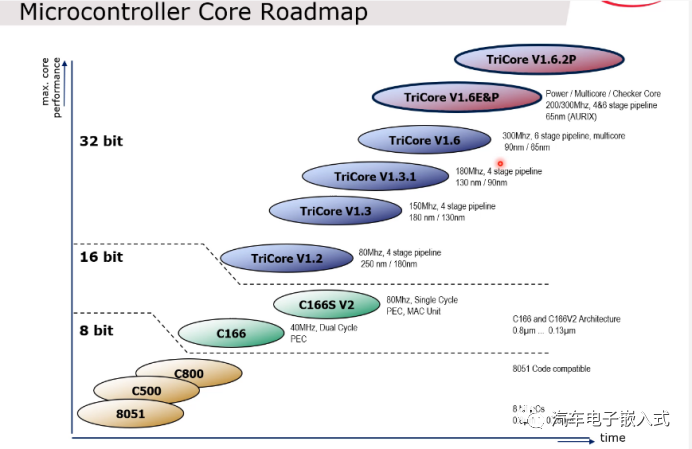

TriCore是英飛凌自主開發(fā)的私有內核。早在2000年,英飛凌發(fā)布了第一代TriCore單片機產(chǎn)品。英飛凌為TriCore申請了注冊商標,在一個內核架構里集成了RISC精簡指令集單片機,MCU微控制器,DSP數(shù)字信號處理的功能,是一款計算能力強大的32位實時單片機內核架構。TC3xx系列MCU是基于TC1.6P作為其內核的。本系列文章將記錄Infineon芯片的學習筆記。本文首先介紹TC3xx的內部模塊框圖和各種內部總線以及存儲器訪問方式,接著介紹TC1.6.2的內核架構,這其中主要介紹了尋址方式,通用寄存器,上下文管理,中斷機制,Trap機制,MPU機制等內容。

1.Architectural Overview

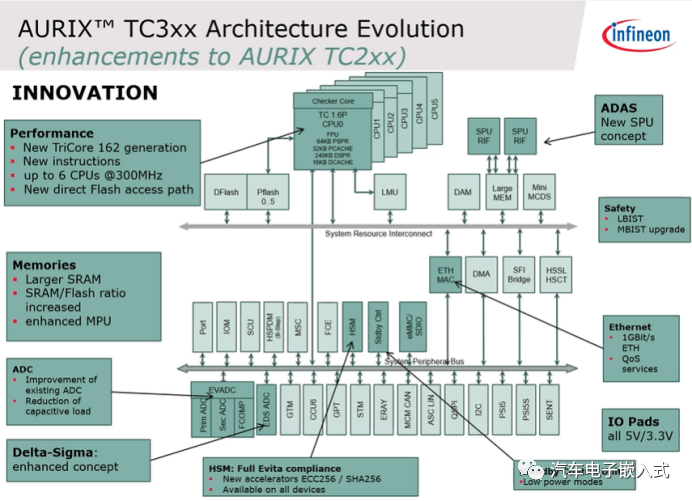

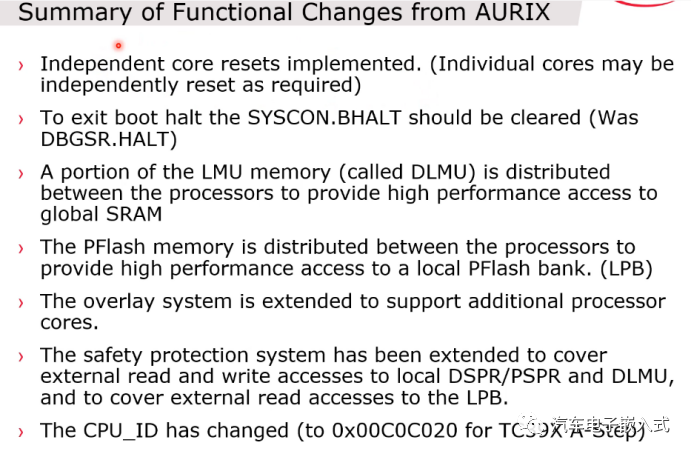

圖1:TC3xx相比于TC2xx改進部分

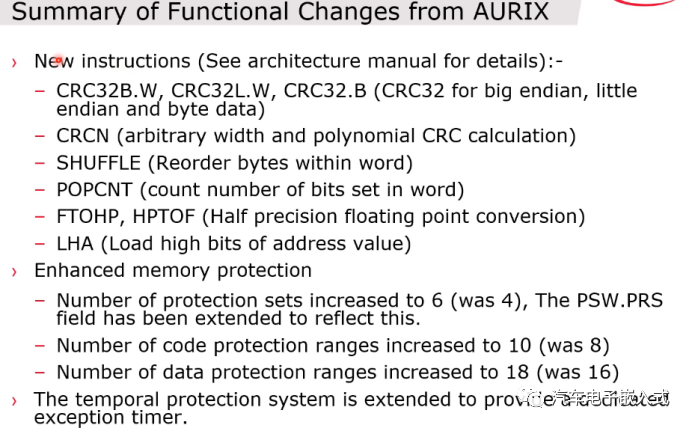

如圖一所示,TC3xx內部最多支持6個核,這些核間使用SRI總線進行通信,每個核都有自己的Memory。TC3xx在核架構上相比于TC2xx做了如下改進:

1.1 Performanc

1)支持Tricore 1.6.2的內核

2)增加了新的指令

3)最多支持6個核,最大主頻達到300MHz

4)每個CPU有自Local的Flash bank,也就是說有自己的Local的總線可以訪問自己Local的Flash bank,速度更快

5)

1.2 Memories

1)更大的SRAM

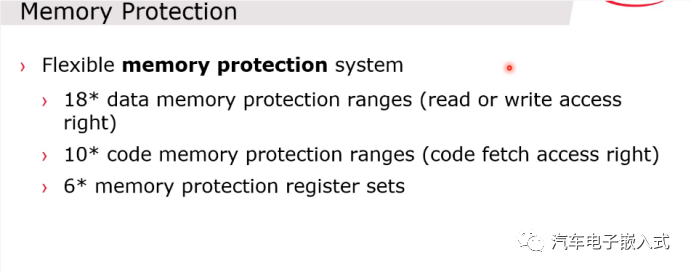

2)更強大的內存保護單元MPU。數(shù)據(jù)和代碼保護的Register的設置更多。

1.3 ADC

1)TC2xx有隊列模式,自動掃描模式,背景掃描模式,TC3xx只有隊列掃描模式,更加的靈活。

1.4 Delta-Sigma

1.5 HSM

1)支持非對稱加密算法

1.6 Standby control unit

專門的低功耗管理單元

1.7 IO Pads

支持5/3.3v兩種硬件系統(tǒng)

1.8 Ethernet

1)支持千M以太網(wǎng),支持一部分TSN/AVB的功能

1.9 Safety

1.10 ADAS

增強的SPU

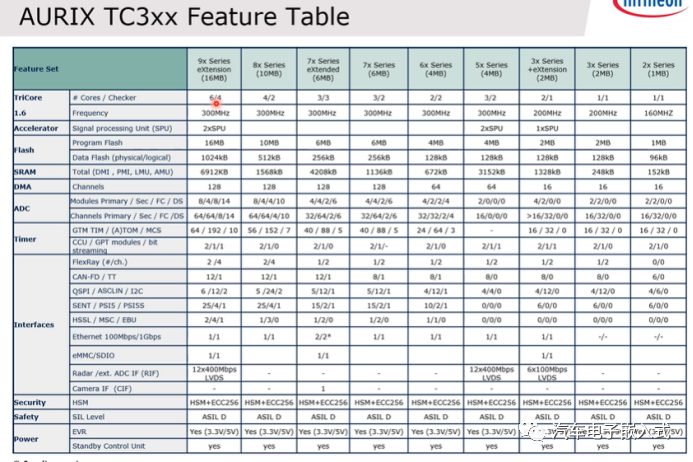

圖2:TC3xx系列資源概況

2.Memory Concept

2.1 Memory architecture

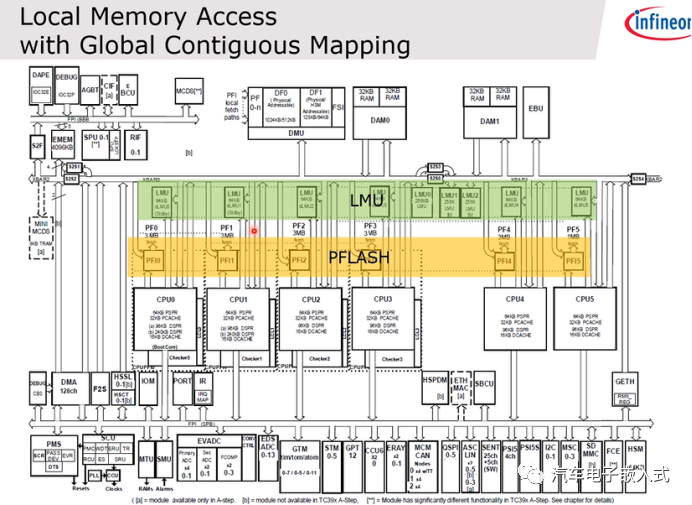

圖3:TC3xx內存架構

主要關注PFlash和LMU部分。

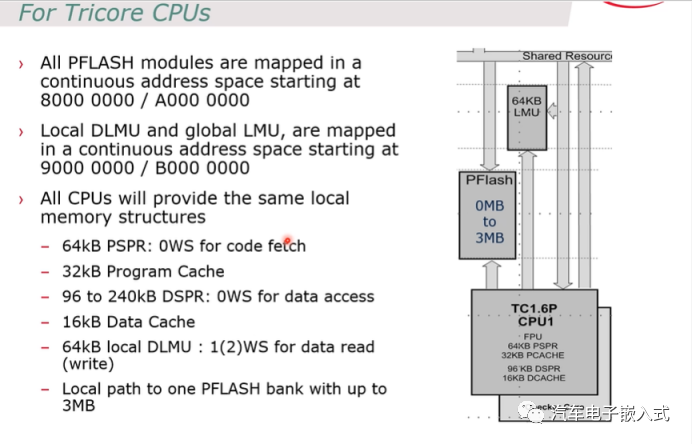

每個CPU都可以通過一個私有的LPB總線訪問各自3M的PFlash的bank,訪問速度比較快。外部有個LMU的Ram,分為兩種,一種叫dLMU,另一種叫LMU。每個cpu可以通過私有的總線訪問dLMU,對于LMU,CPU只能通過SRI總線來訪問,速度相對dLMU的訪問較慢。

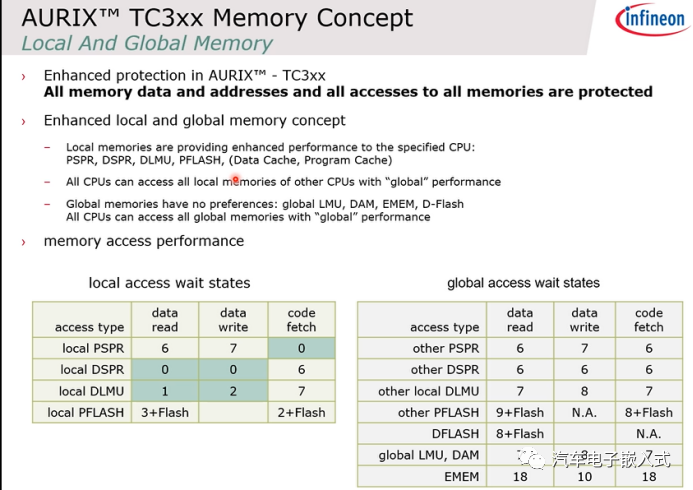

圖4:TC3xx內存訪問速度

PSPR,DSPR,DLMU都是Local的SRAM,CPU訪問自己的Local Ram的熟讀非常的快,例如CPU讀寫local DSPR都是0等待時間的。CPU也能范圍其他核的Local Ram,但是讀/寫/取指的速度就會變慢。

圖5:內存范圍起始地址

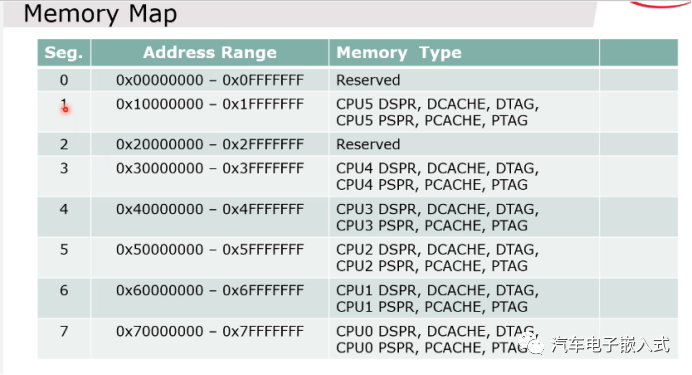

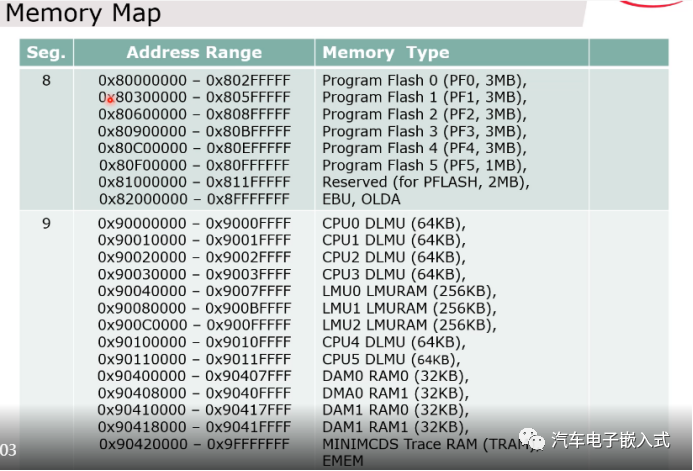

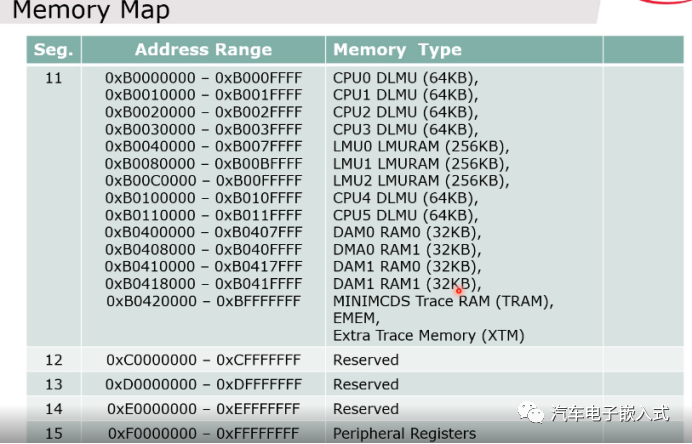

對于同一款內存可以使用cache的訪問方式或者非cache的訪問方式。例如對于PFLASH的訪問如果使用cache則起始地址是0x80000000,非cache的訪問方式的起始地址是0xA0000000。同樣,LMU也存在0x90000000/0xB00000000兩個起始地址。

對于每個CPU內部的PSPR和DSPR都不需要使用cache,CPU等待時間是0ws。

每個CPU都有3M的local PFLASH的bank,CPU通過LPB總線訪問PFLASH。這個LPB總線在使能了AB SWAP之后就會被disable掉,這么做的原因是為了讓code運行在A Bank還是B Bank的performence都是一樣的(是能ab swap和disable lpb總線的操作在UCB的一塊區(qū)域操作)。

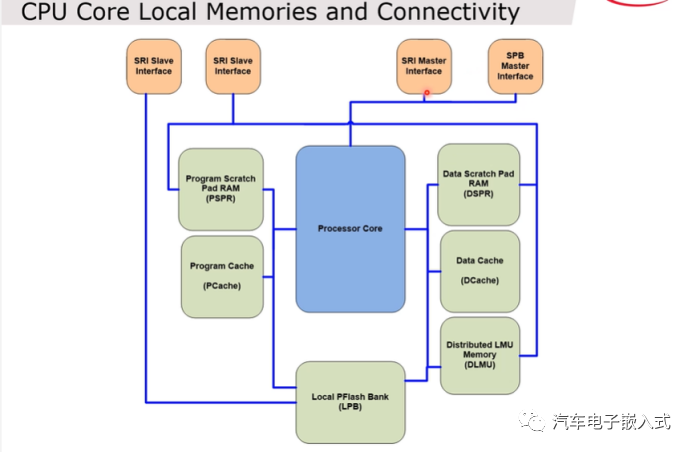

2.2 Memory and connectivity

圖6:CPU內部總線連接圖

CPU通過SRI Master Interface連接到其他core的SRI Slave Interface來范圍其他核的memory。

2.3 Memory map

圖7:內存映射圖

3.On-chip Bus Connectivity

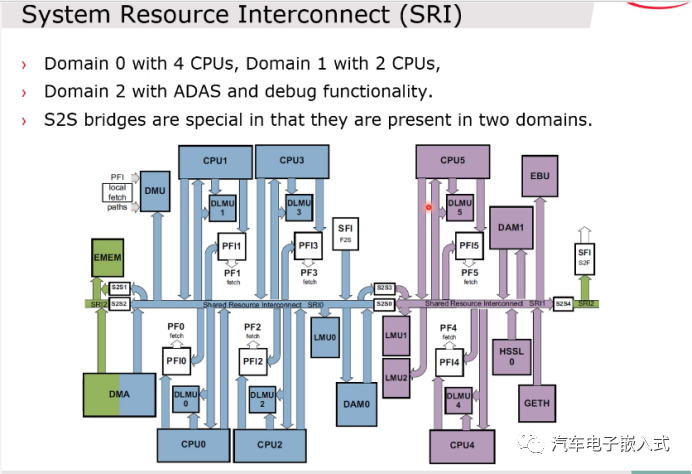

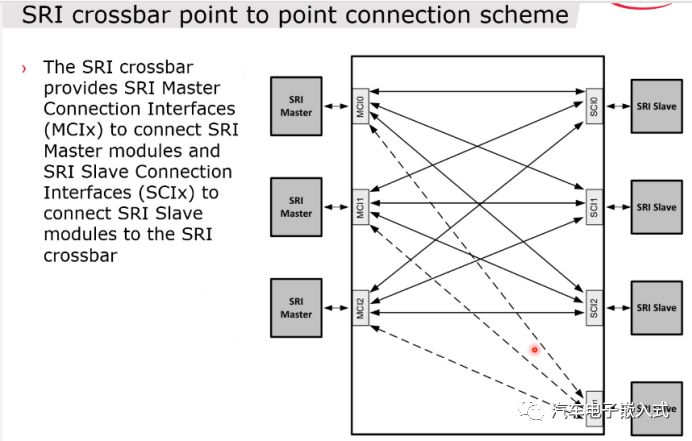

圖8:SRI總線

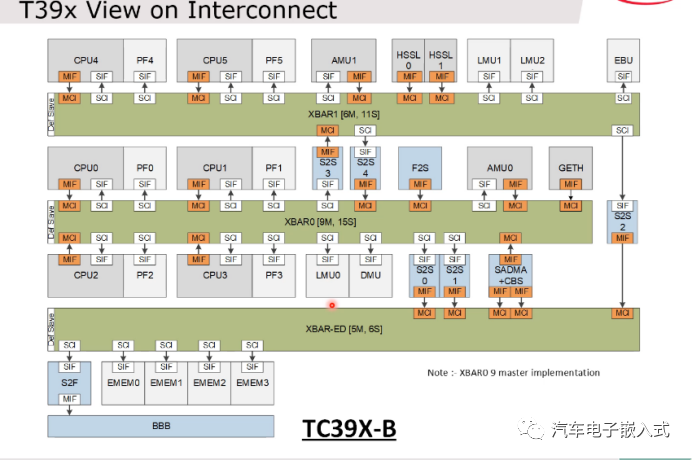

Tricore里面,內核之間的相互訪問和通信都是通過SRI總線進行的。Tricore 1.6.2里面SRI總線有3個Domain,Domain 1包括CPU0-3,通過SRI0進行相互訪問。其他類似。SRI直接通過S2S Bridge連接。

圖9:SRI總線連接圖

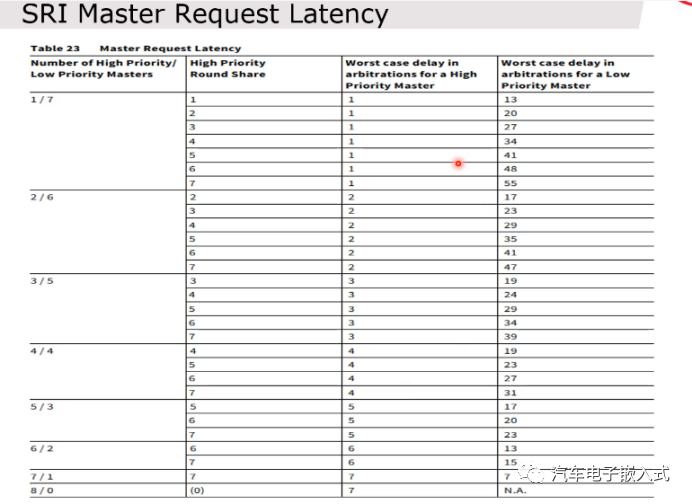

圖10:SRI總線間最差延遲時間

圖11:TC39x內部SRI總線連接圖

每個SRI總線都有一個SRI Master Interface和一個SRI Slave Interface,對于一個SRI總線的SRI Slave Interface就存在同一時間多個SRI Master Interface訪問的問題,那么就需要SRI具有仲裁的功能。

4.TC1.6.2 Architecture

4.1 TriCore concept

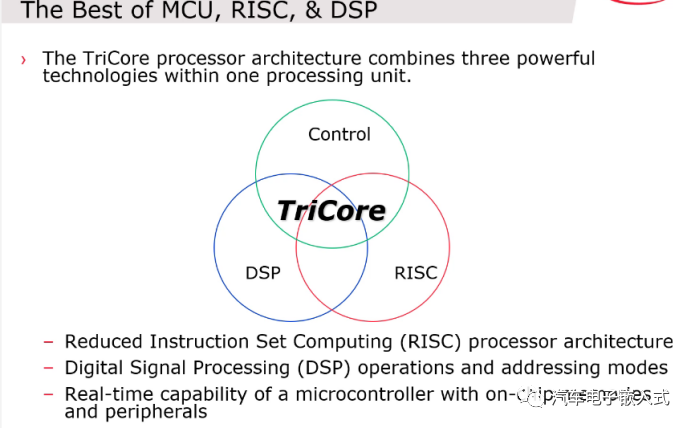

圖12:TriCore定義

TriCore的含義:既有RISC精簡指令集的特性,也集成了DSP數(shù)字信號處理器的性能,同時也可以實現(xiàn)實時控制。

圖13:英飛凌TriCore的發(fā)展圖

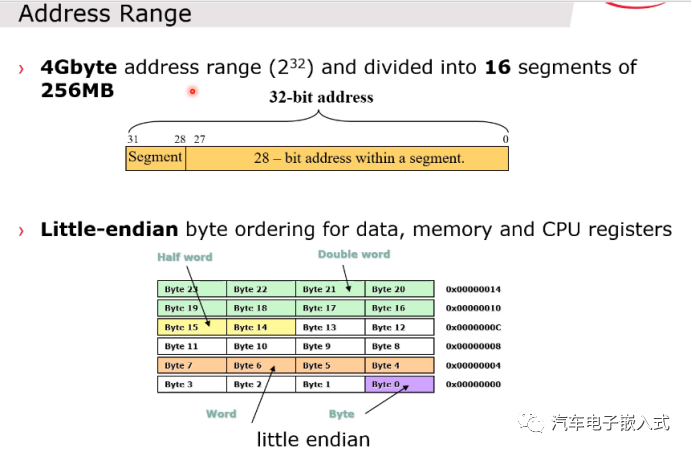

4.2 Address range

圖14:TriCore的尋址空間

4G的尋址空間,16個Segment,小端系統(tǒng)。

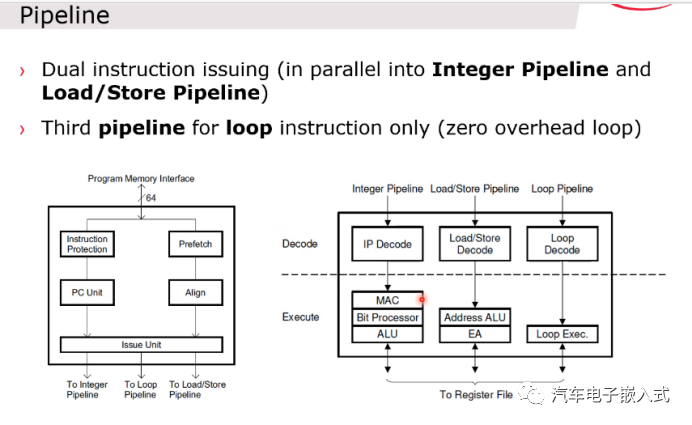

4.3 Pipeline

圖15:Pipline

整型的Pipline主要組數(shù)據(jù)的運算,類似數(shù)據(jù)的加減乘除。Load/Store Pipline主要用來做數(shù)據(jù)的讀取和存儲,Loop Pipline主要做數(shù)據(jù)的循環(huán)處理。三個Pipline可以并行處理。

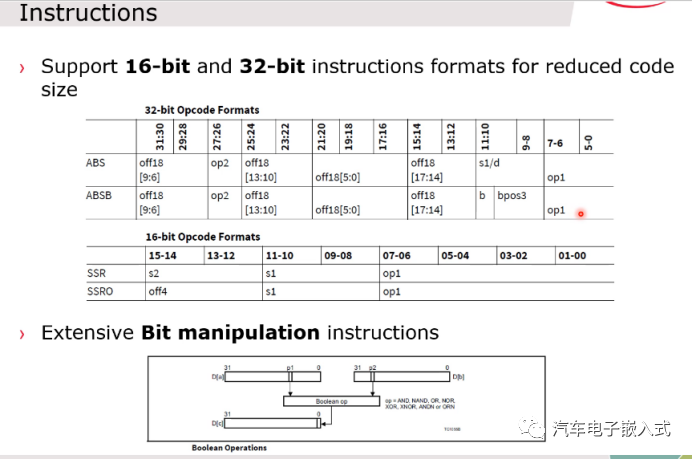

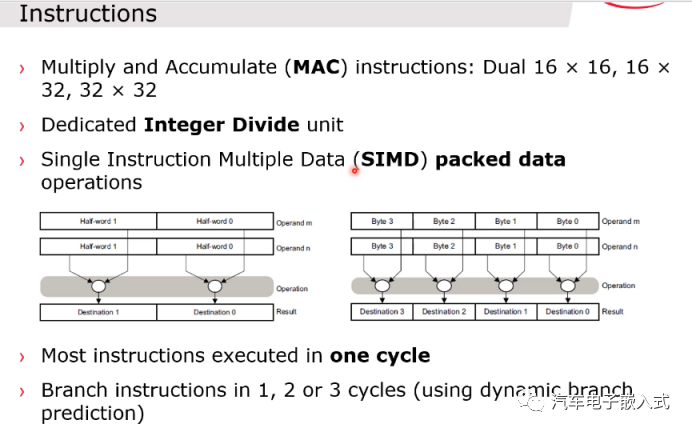

4.4 Instructions

圖16:指令

支持16位和32位指令格式,op1的bit 0為1則是32位指令,op1的bit 0為0則是16位指令。

支持位操作

支持MAC乘加指令,除法指令,單周期多數(shù)據(jù)處理指令SIMD。

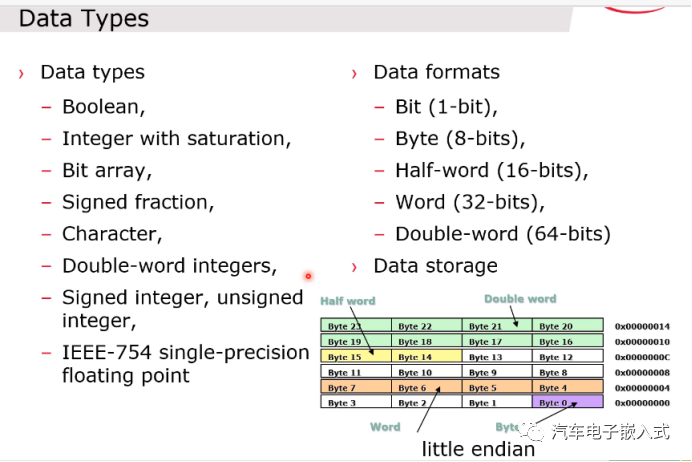

4.5 Data Types

圖17:支持的數(shù)據(jù)類型

支持大部分數(shù)據(jù)類型。

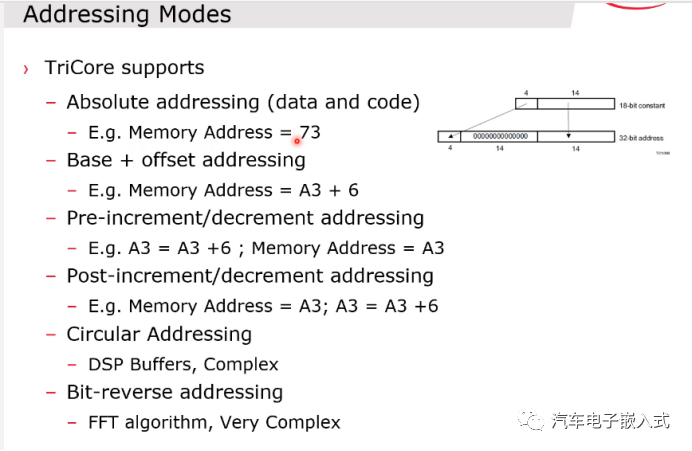

4.6 Addressing Modes

圖18:尋址方式

支持絕對地址尋址,相對地址尋址,先加減后運算尋址,先運算后加減尋址。

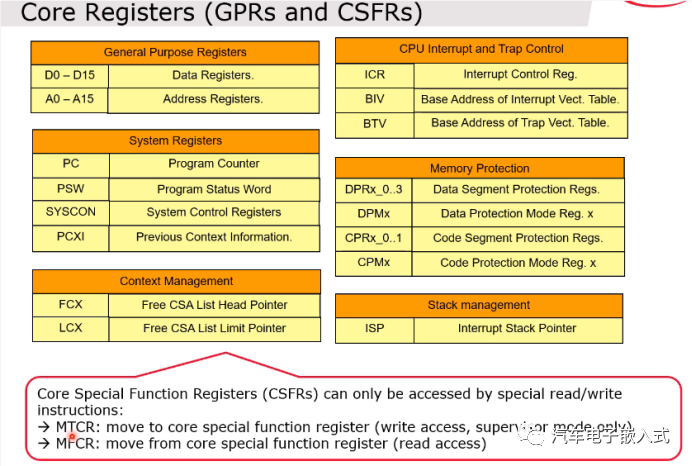

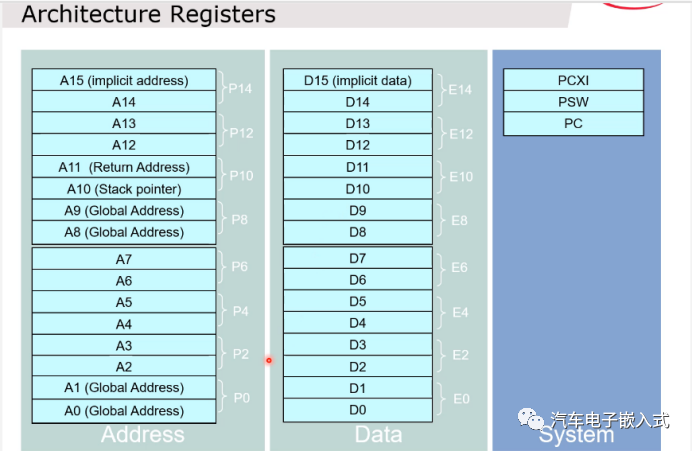

4.7 Core Registers

圖19:核寄存器

通用寄存器:和ARM核(r0 - r15)不一樣,數(shù)據(jù)寄存器和地址寄存器分開。數(shù)據(jù)運算和地址運算不沖突,這樣可以提高尋址和數(shù)據(jù)處理的效率。

系統(tǒng)寄存器:PC指針,程序狀態(tài)字寄存器,系統(tǒng)控制寄存器(比如設置系統(tǒng)在Run/Halt/Sleep狀態(tài))

上下文寄存器:

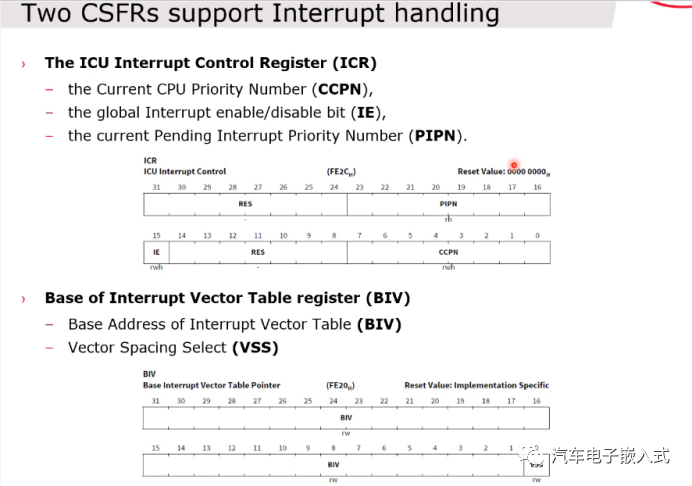

中斷和陷阱控制寄存器:ICR寄存器可以控制全局中斷的開關。BIV是中斷向量表的起始地址,BTV是陷阱向量表的起始地址。

內存保護寄存器:

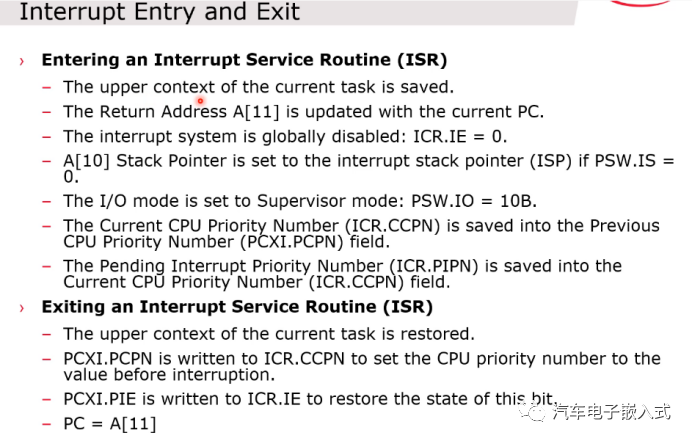

棧中斷寄存器:通用寄存器里面的A10是user stack pointer,而ISP是interrupt stack pointer,通過PSW寄存器可以設置是否使用ISP,如果使用了ISP的話,通常情況下系統(tǒng)使用A10作為棧指針,一旦產(chǎn)生中斷后系統(tǒng)把ISP指向的地址賦值給A10,也就是中斷使用另一塊內存作為棧空間。

訪問核寄存器只能只用專用的MTCR,MFCR指令。

A11類似ARM核里面的LR寄存器。

所謂Global Address也就是進入中斷或者進行函數(shù)調用的時候是不存這些內容的。

數(shù)據(jù)和地址寄存器可以兩個合起來作為一個64位的寄存器(P0/D0)。

4.8 Context Management

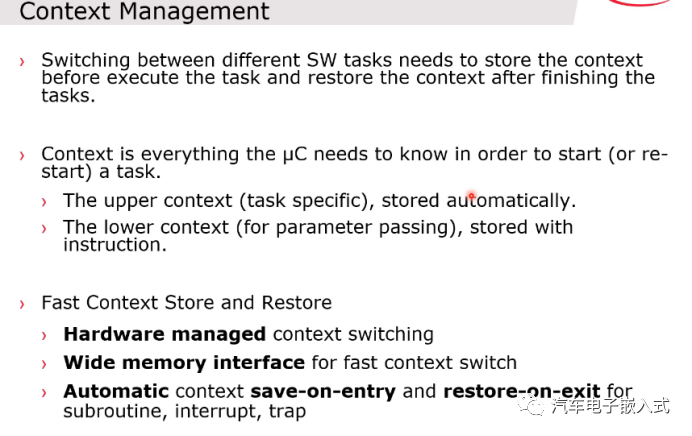

圖20:上下文管理

圖21:上下文存儲區(qū)域

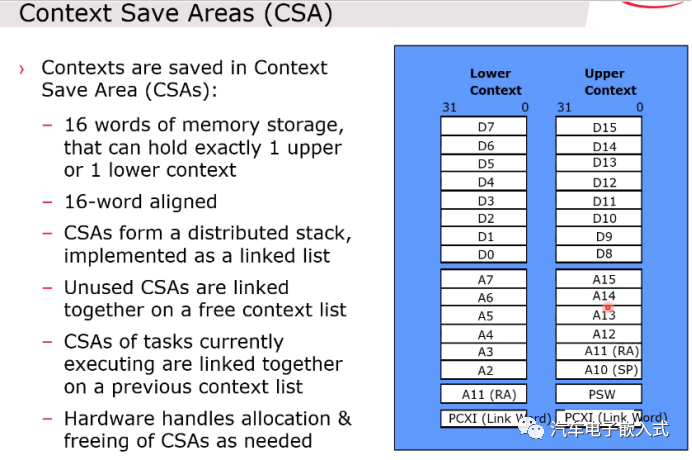

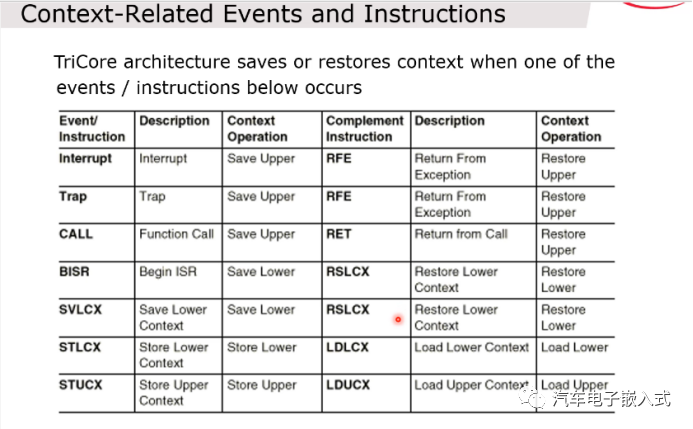

TriCore的上下文處理比較特殊。對于通用MCU(ARM 核)在進入中斷或者函數(shù)調用時候的上下文內容一般存放在棧里面的,但是TriCore的上下文存放在一個叫CSA的區(qū)域的。Upper Context 的內容由硬件自動處理,而Lower Context的內容需要一些特殊的指令操作。

圖21:上下文事件和指令

對于絕大部分簡單的ISR, Trap, 函數(shù)調用都比較簡單的話只要保存Upper context就足夠了,也就不會產(chǎn)生后面的BISR,SVLCX,STLCX,STUCX指令。

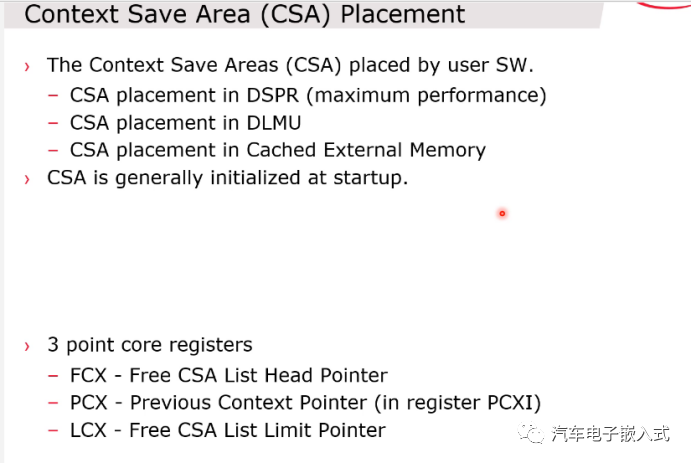

圖22:CSA存放地址

CSA可以存放在DSPR(一般存放在這里),DLMU,External Memory里面,通過修改連接ld文件來配置。

FCX: 指向空閑的CSA的起始地址。

PCX: 指向已經(jīng)使用的CSA的地址。

LCX: 指向空閑CSA的結束地址。

4.8 Interrupt System

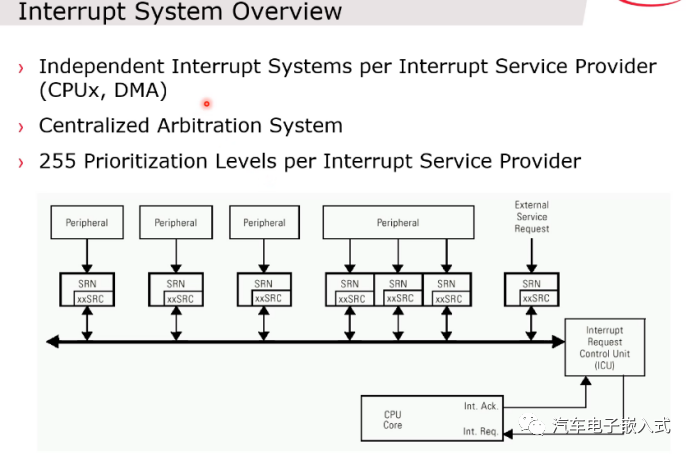

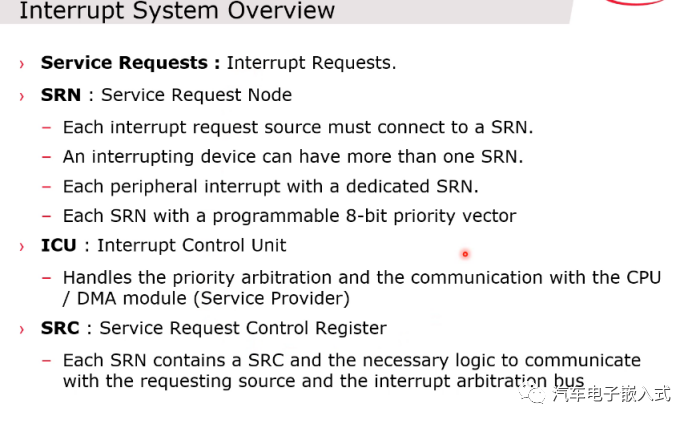

圖23:中斷系統(tǒng)

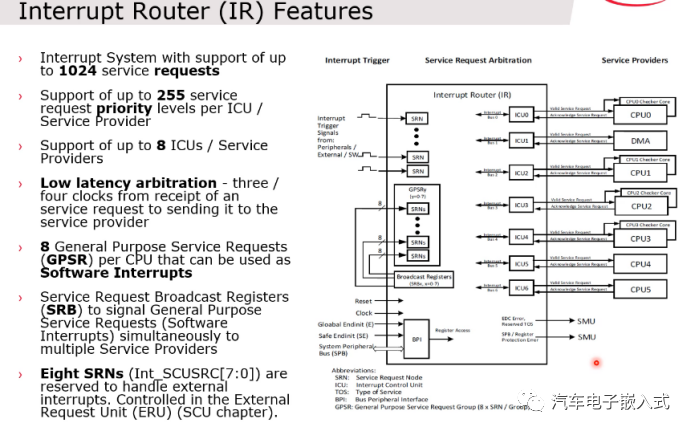

TriCore 1.6.2中最多有7個中斷服務提供對象,分別是CPU0-5以及DMA。每一個Service Provider對應一個中斷控制單元ICU,中斷服務請求節(jié)點SRN最多有1024個,8個GPSR可以用作軟中斷做來核間通信。

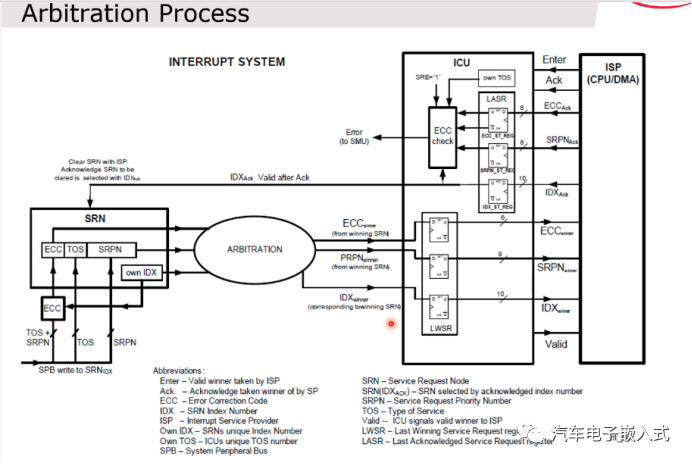

圖24:中斷仲裁

ICU能夠仲裁處理多個SRN同時的請求。

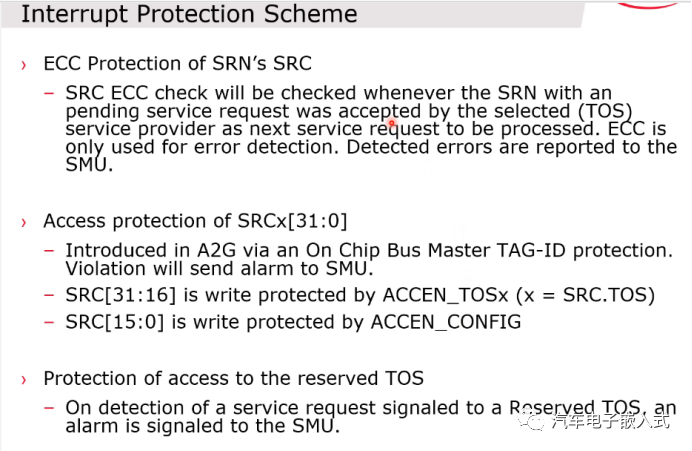

圖25:中斷保護

中斷寄存器也有保護機制,SRC有ECC的保護措施,在寫完SRC寄存器后會自動生產(chǎn)一個ECC的Code,然后這個SRC的內容在被讀取的時候就會做ECC的check。

SRC寄存器的權限也可以設置。比如,每個Bus Master總線都會有一個TAG-ID,我們可以設置SRC寄存器可以被哪些TAG-ID表示的總線訪問。

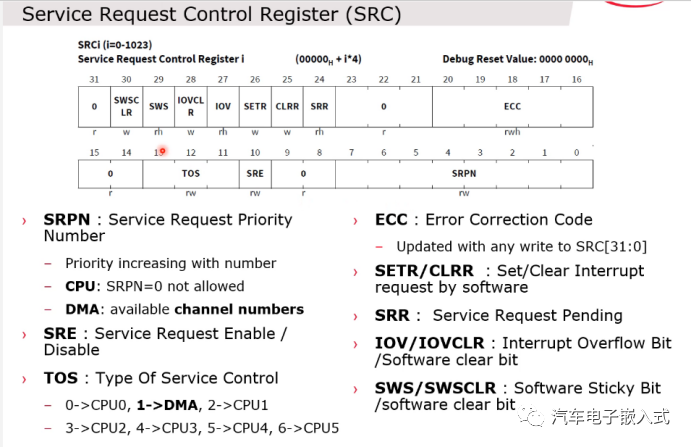

圖26:服務請求控制寄存器SRC

圖27:中斷控制寄存器ICR和中斷向量表地址寄存器BIV

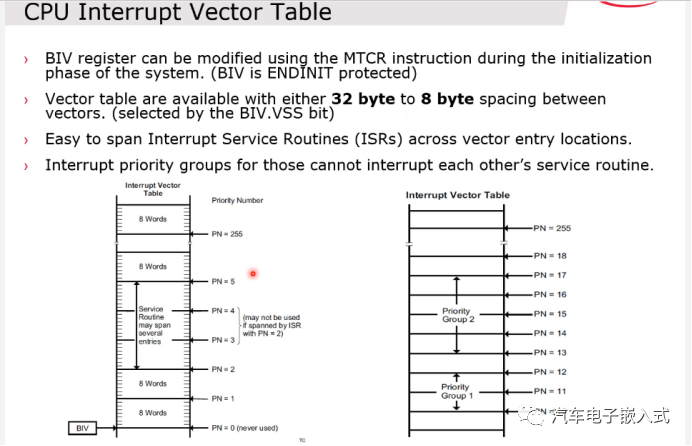

VSS寄存器設置中斷向量表是8字節(jié)對齊還是32字節(jié)對齊。

圖28:中斷向量表

在TricCore里面,中斷向量表不是固定的,是跟著中斷優(yōu)先級走的,也就是整個中斷向量表內中斷服務的排序是會跟著中斷優(yōu)先級的變化而變化的(和其他內核不一樣)。

圖29:中斷處理過程

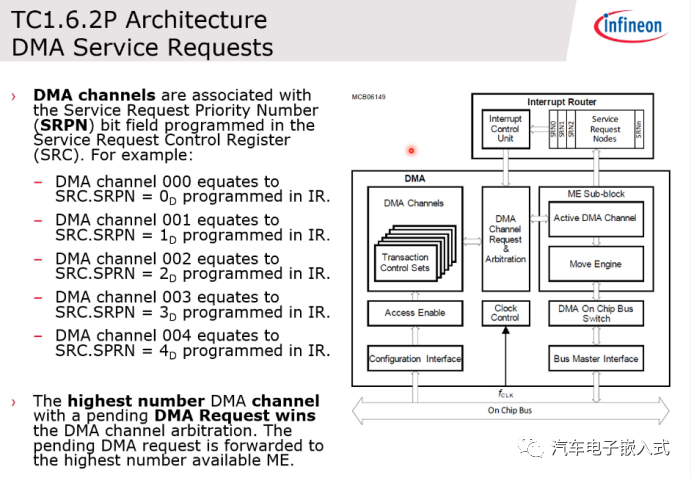

4.9 DMA service requests

圖30:DMA服務請求

SRN目標也可以選擇DMA的,選擇DMA的時候,TOS要設置成1。中斷優(yōu)先級要設置成和DMA的通道號一樣,也就是中斷優(yōu)先級在選擇DMA的時候就是DMA的通道號,這個很關鍵。

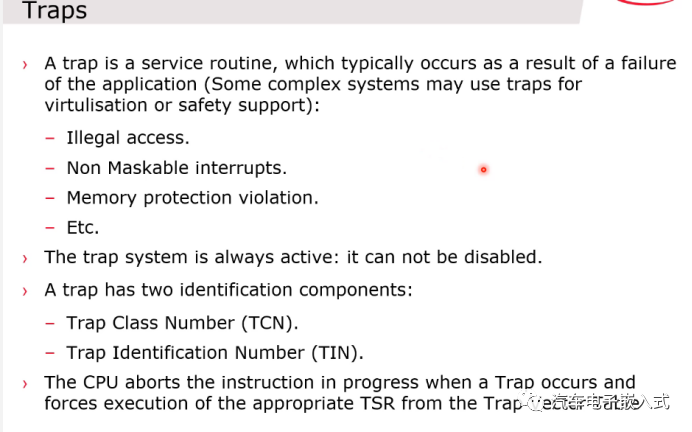

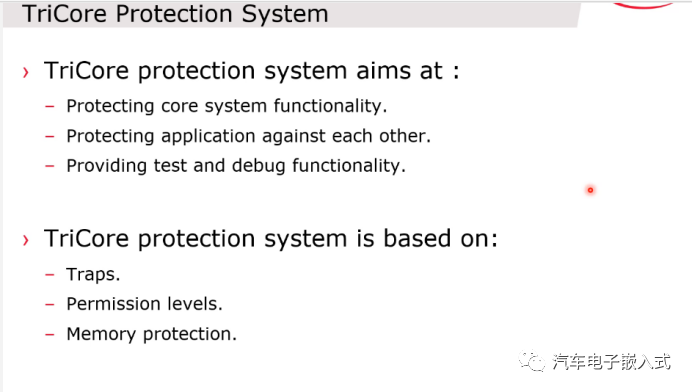

4.10 Traps

圖31:Trap

Trap的概念就類似ARM里面的Exception vector異常向量。Trap也有自己的Trap向量表,Trap是為了檢查一些非法的訪問,例如NMI中斷,內存保護。Trap有自己的類型TCN和ID TIN。

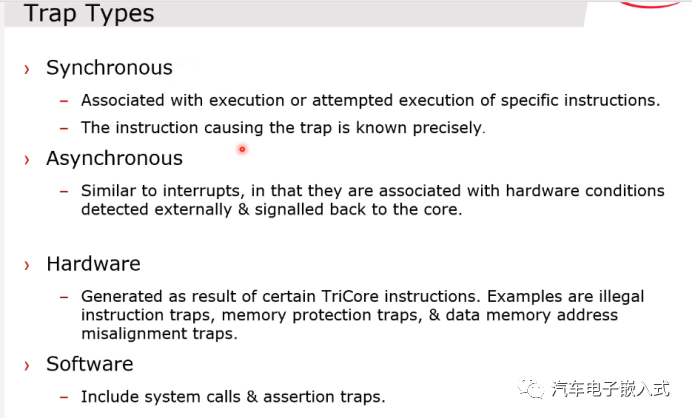

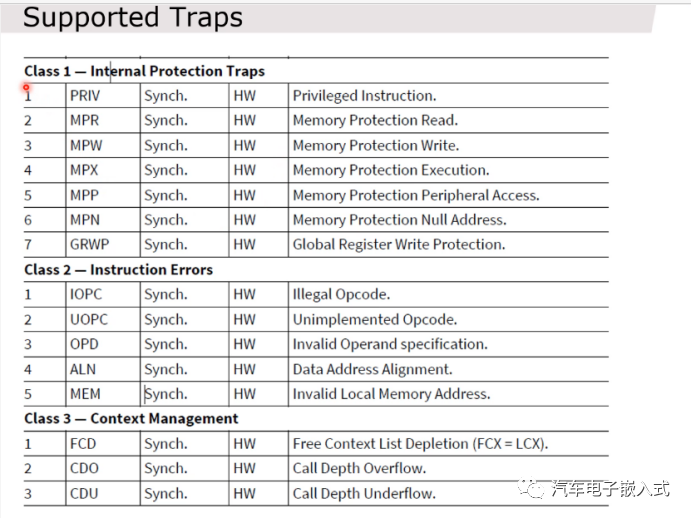

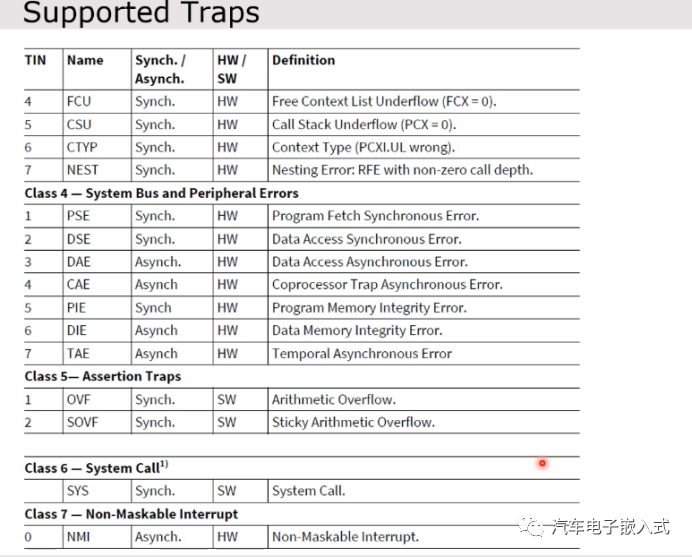

圖32:Trap類型

Trap類型一般有兩種劃分方式,同步或者異步,硬件或者軟件。

同步Trap:CPU在執(zhí)行的過程中發(fā)生的Trap,比如說中斷溢出,取值錯誤,內存非法訪問等。Trap發(fā)生的時候,CPU會把Trap發(fā)生的指令的下一條指令作為返回地址保存到A11寄存器當中,所以在Trap的handler里面可以讀取A11來定位Trap發(fā)生的位置。

異步Trap:和中斷類似,一般由外設或一些協(xié)處理器的錯誤造成的。比如說FPU上發(fā)生的一些Trap。異步Trap發(fā)生的時候,A11中的內容不具備參考意義的。

硬件Trap:比如說CPU執(zhí)行的指令是非法的,內存保護錯誤等。

軟件Trap:軟件調用了一些系統(tǒng)調用指令,比如assert。

圖33:具體的Trap

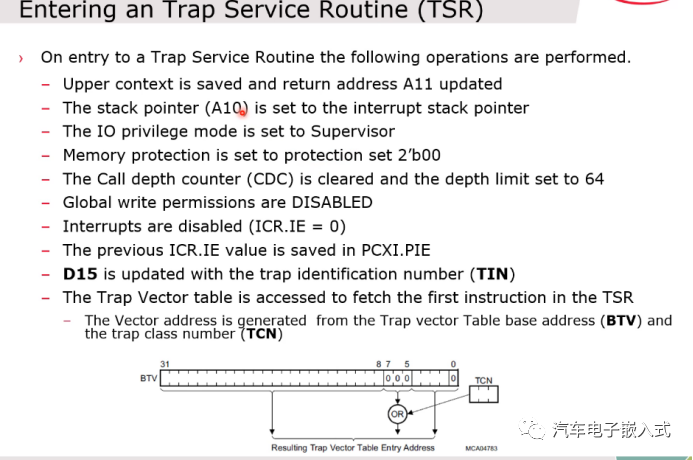

圖34:Trap處理過程

關鍵點,D15保存了Trap的ID號,可以在handler中讀取D15獲取Trap ID。

圖35:Trap保護機制

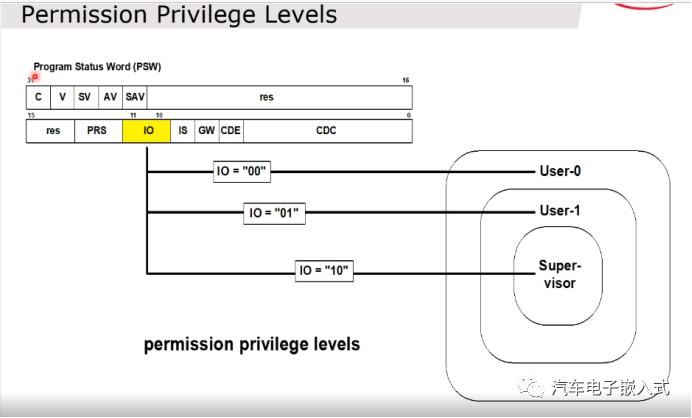

4.11 Permission Privilege Levels

圖36:權限設置

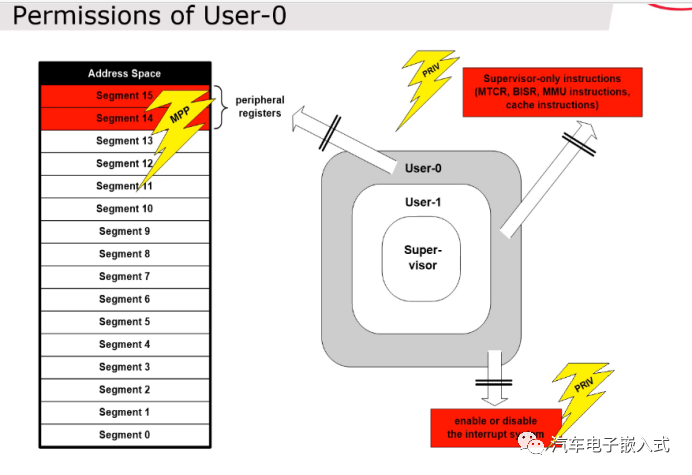

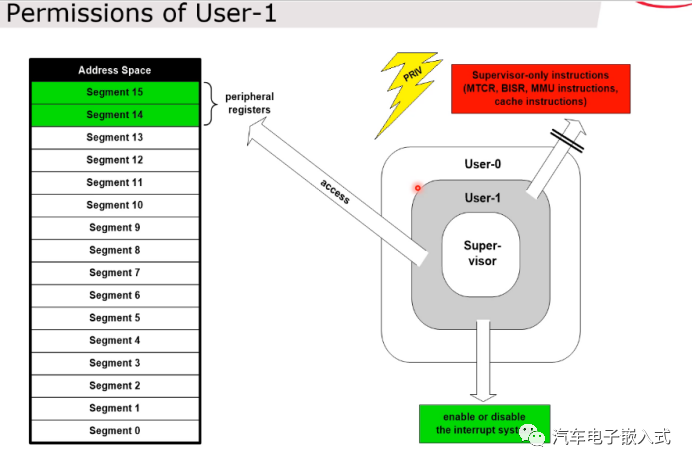

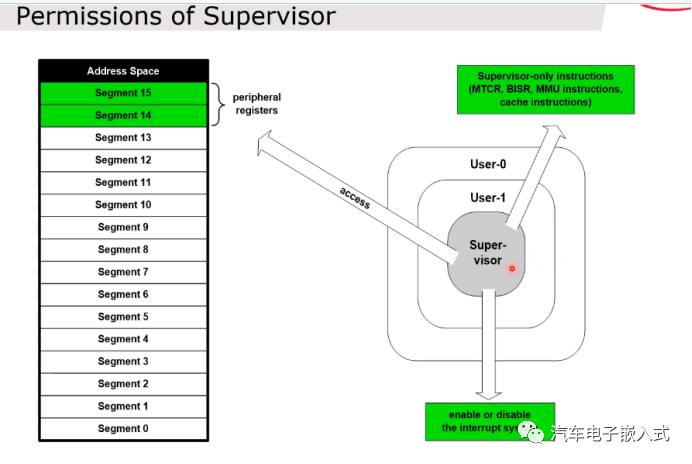

圖37:不同模式下的訪問權限

User0模式允許訪問外設寄存器,不允許訪問內核寄存器,也不允許訪問中斷系統(tǒng)寄存器。

User1模式可以訪問中斷系統(tǒng)寄存器。

Supervisor模式可以訪問核寄存器。

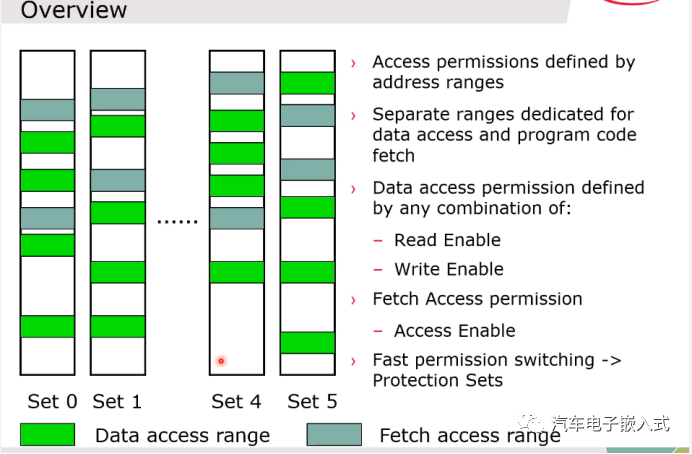

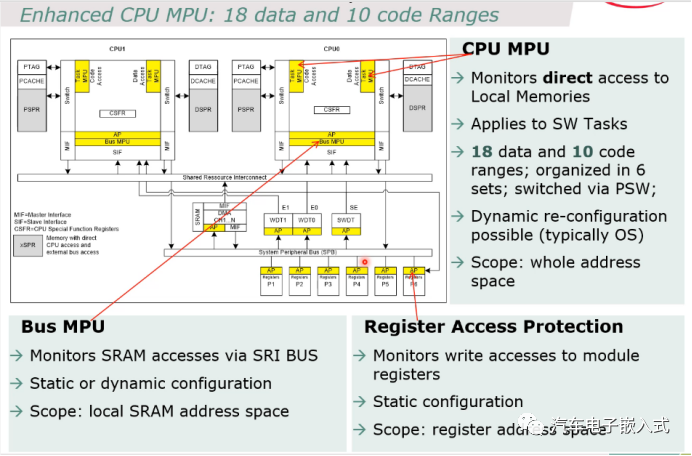

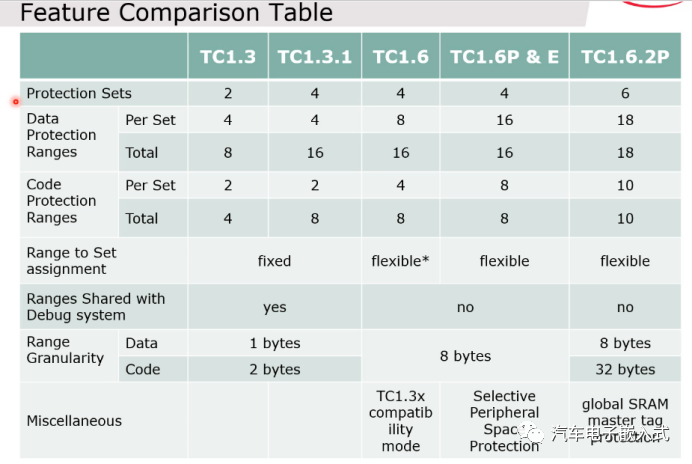

4.12 Memory protection

圖38:內存保護

實際上就是6組MPU保護,6*18的數(shù)據(jù)保護,6*10的代碼保護。

Bus MPU: 可以設置哪些Master Interface可以訪問Local SRAM

圖38:增強的內存保護

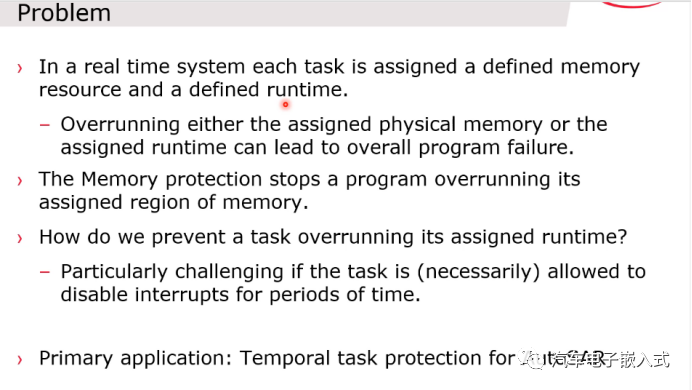

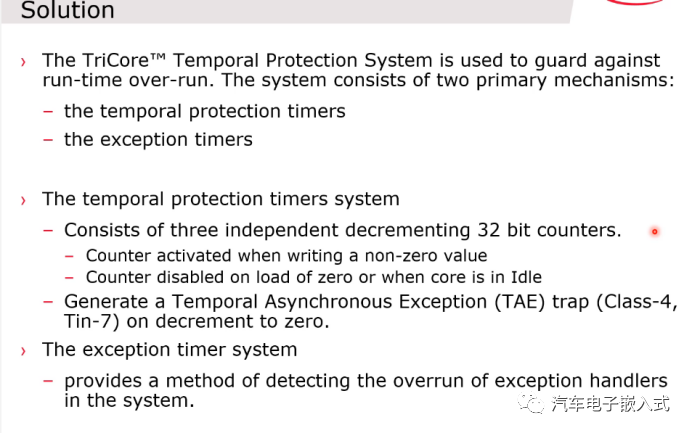

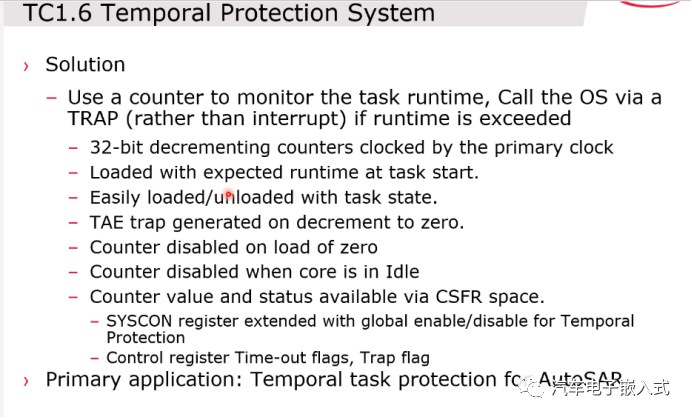

4.13 Temporal Task Protection

實時操作系統(tǒng)對于內存訪問錯誤可以通過MPU內存保護來識別和定位問題,但是對于任務超時該怎么來監(jiān)控了?-- TriCore提供了時間任務保護機制來實現(xiàn)任務超時監(jiān)控。

圖39:時間任務保護

5.Summary

審核編輯:郭婷

-

英飛凌

+關注

關注

66文章

2183瀏覽量

138658 -

存儲器

+關注

關注

38文章

7484瀏覽量

163776 -

總線

+關注

關注

10文章

2878瀏覽量

88056

原文標題:學習筆記 | Aurix TC3xx Architecture

文章出處:【微信號:汽車電子嵌入式,微信公眾號:汽車電子嵌入式】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

TC3xx內部模塊框圖和各種內部總線及存儲器訪問方式

TC3xx內部模塊框圖和各種內部總線及存儲器訪問方式

評論