在眾多電源方案當中,LLC諧振方案是電子愛好者熱衷討論的話題,焦點主要集中在兩點:PCB LAYOUT與諧振回路;優秀的PCB LAYOUT可以讓諧振回路更穩定,糟糕的PCB LAYOUT則會讓諧振回路失去穩定性。而千變萬化的PCB是產品精髓之處,也是LAYOUT有魅力的原因。

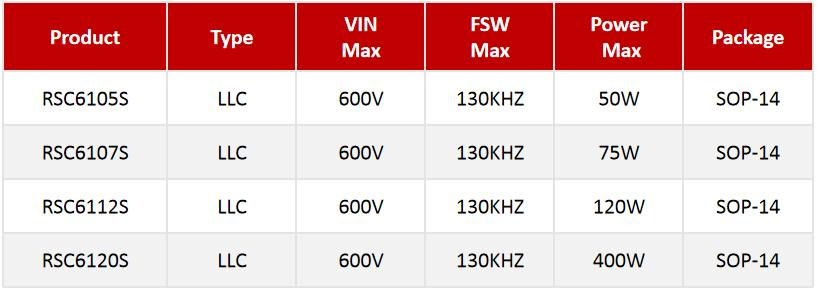

那么接下來小編就結合瑞森RSC6105S的實際應用,分享通過PCB LAYOUT怎樣提升LLC諧振方案的穩定性。

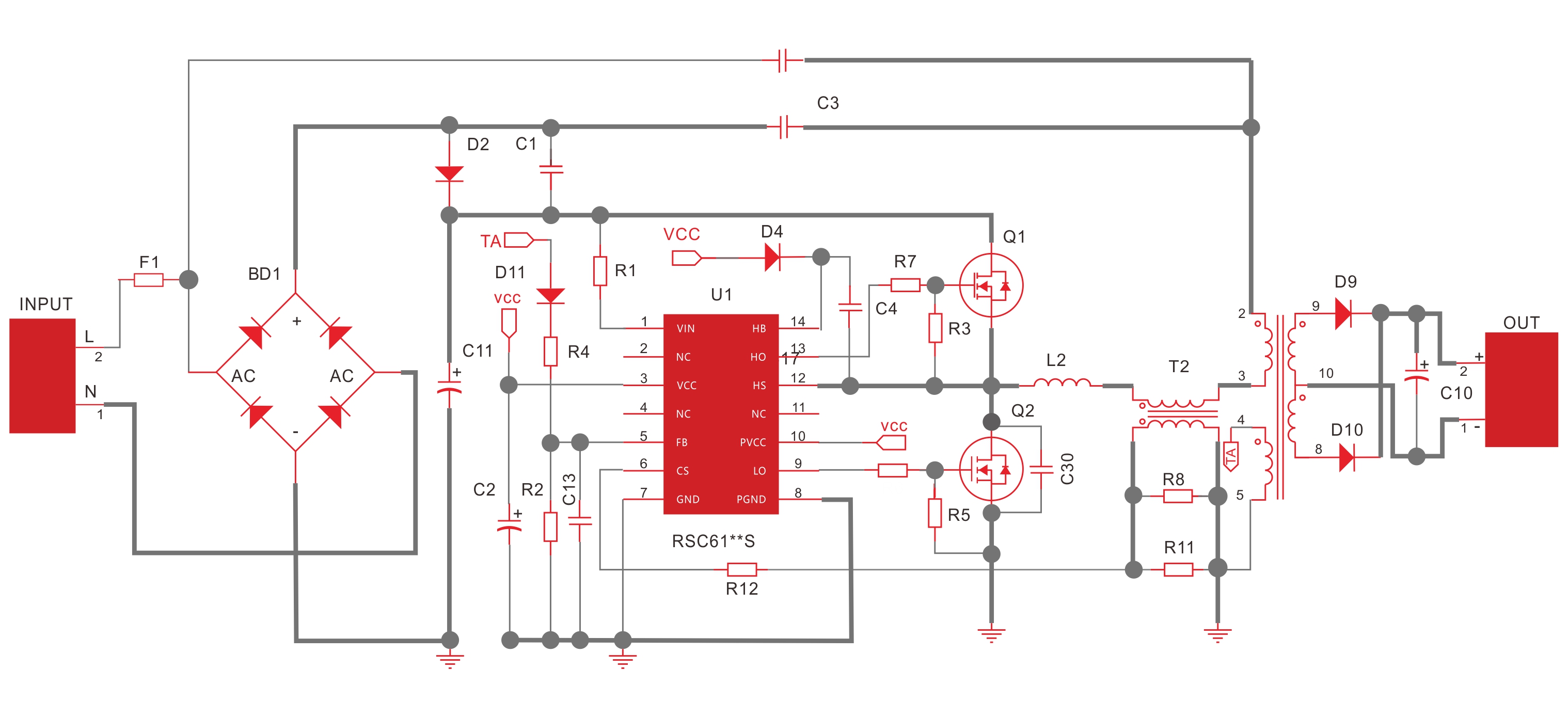

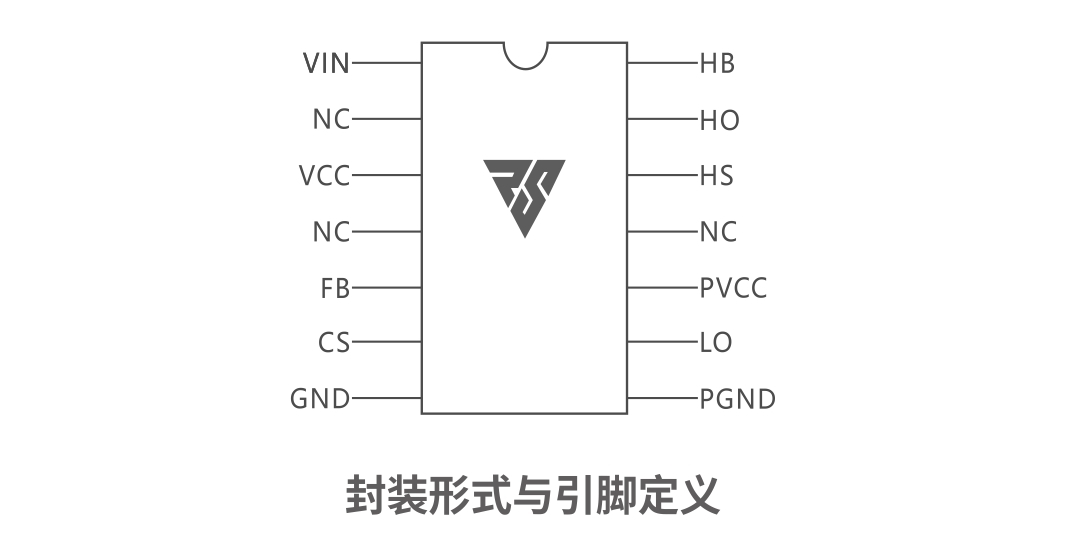

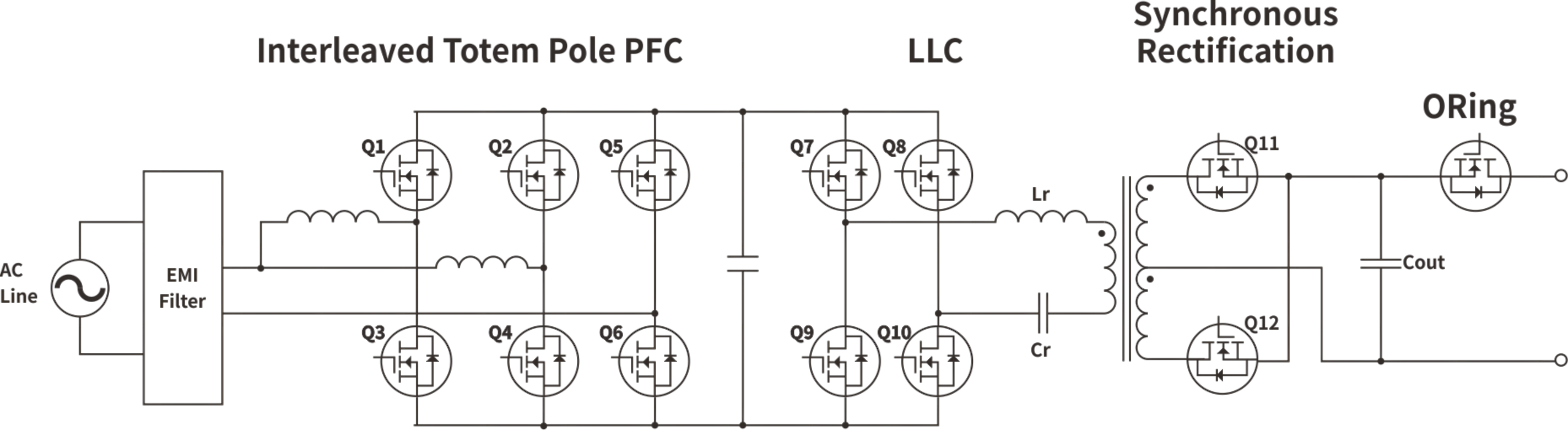

首先開關電源線路的開關特性會使電源的MOS與變壓器產生電磁兼容方面的干擾,作為電源設計工程師必須了解產生電磁兼容問題的原因以及解決措施,同時也要避免干擾源的擴大。如圖結合實例說明LLC諧振電源方案PCB設計的要點:

典型應用線路圖

一、PCB LAYOUT案例分享

結合RSC6105S系列典型應用原理圖,小編與大家分享如何做好PCB LAYOUT方案:

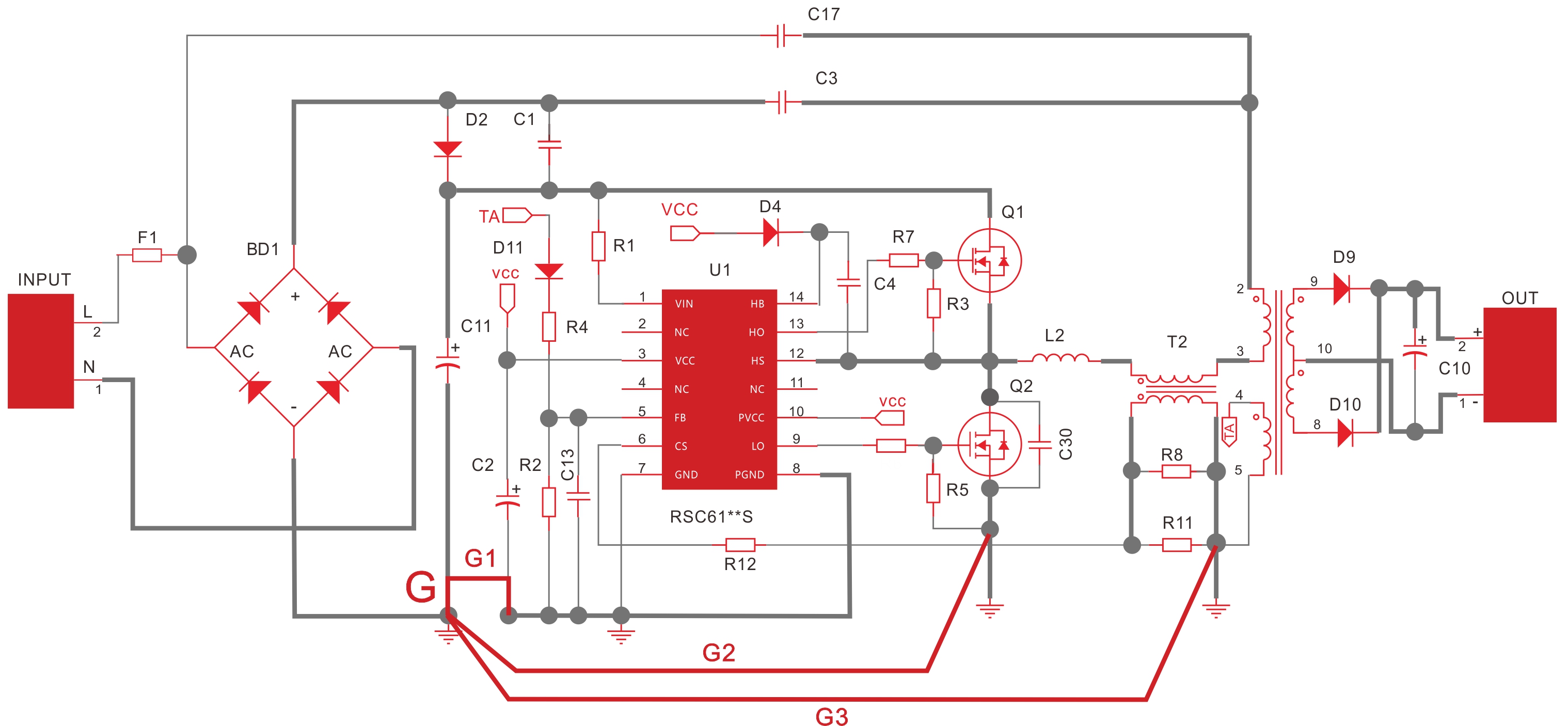

1.嚴格遵循功率GND、信號GND分離的原則;

如圖示例中G1、G2、G3分別單點連到高壓電解C11的負端處,其中G1是重點:LAYOUT注意芯片GND,FB下偏電阻的GND先回到VCC的GND,然后再回到G處。

應用圖

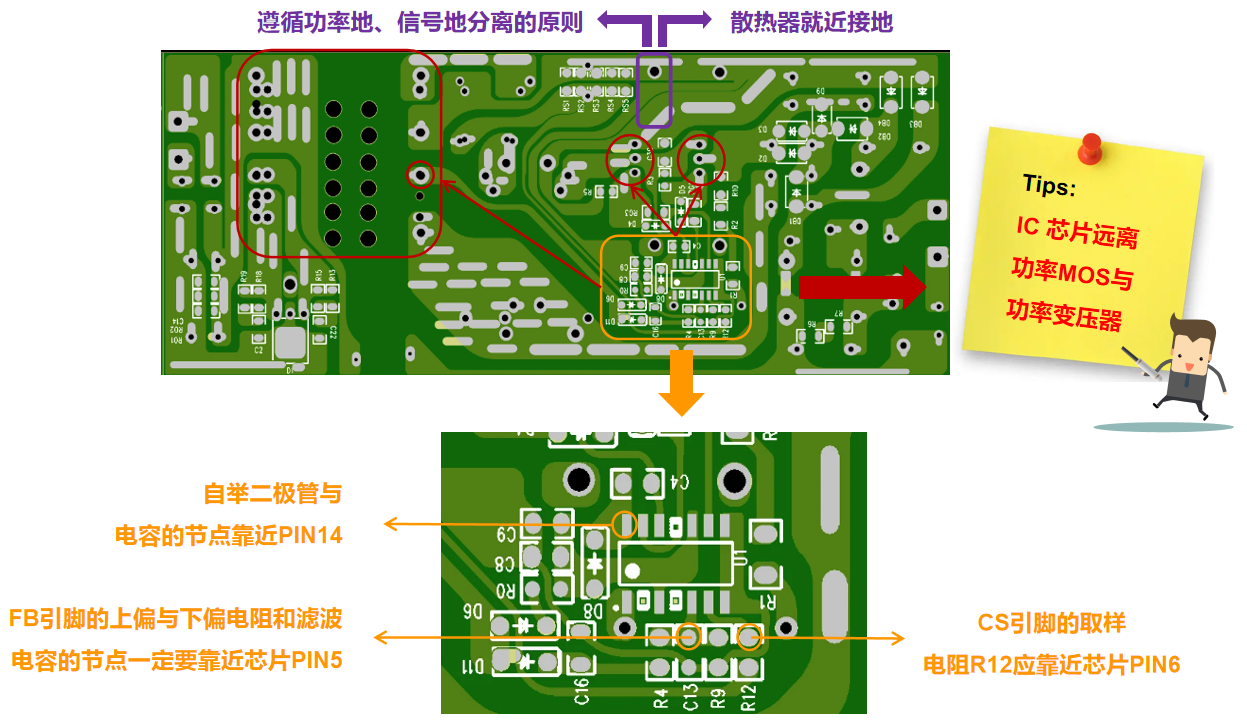

2.減小主功率環路的面積,包括諧振腔回路、開關功率回路、負載電流回路,可有效減少干擾源的擴大;如圖示例中加粗線的部分走線銅箔。

3.連接MOSFET GATE的走線應盡量減短,但為了減小引線電感,GATE走線可適當加粗;如圖示例中Q1、Q2之G端的引線銅箔。

4.自舉升壓回路注意點,自舉二極管與電容的節點靠近PIN14之HB腳, 應避免外來干擾引入,影響系統的穩態工作。

5.FB引腳的上偏與下偏采樣電阻和濾波電容的節點一定要靠近芯片PIN5之FB腳,需要注意的是放置的位置較遠時,會影響OVP點以及可拉載的電壓點。

6.CS引腳的取樣電阻R12應靠近芯片PIN6之CS腳,并且要遠離存在較高di/dt的走線,減少造成恒流點不穩定因素。

7.在使用散熱器時,散熱器上會有高頻電流流過,所以散熱器應就近接GND,這樣可減少干擾源的擴大。

8.芯片背面PCB正上方盡量不要放置與芯片GND存在較高動態電壓差的器件,例如變壓器、臥躺式且大平面緊貼PCB朝下的TO-220封裝MOSFET。

二、實例PCB說明

優秀的PCB LAYOUT可以讓電源系統更穩定的工作,遠離電場與磁場的干擾,避免系統誤動作;順暢的PCB走線可以讓生產線不良率降低,提升直通率;整齊的產品布局可以給產品賣點加分;總之做好產品從PCB LAYOUT開始!

在后續的文章里,將會持續分享相關技術知識,敬請關注!

審核編輯 黃昊宇

-

LLC

+關注

關注

36文章

570瀏覽量

76923 -

諧振

+關注

關注

5文章

376瀏覽量

39621

發布評論請先 登錄

相關推薦

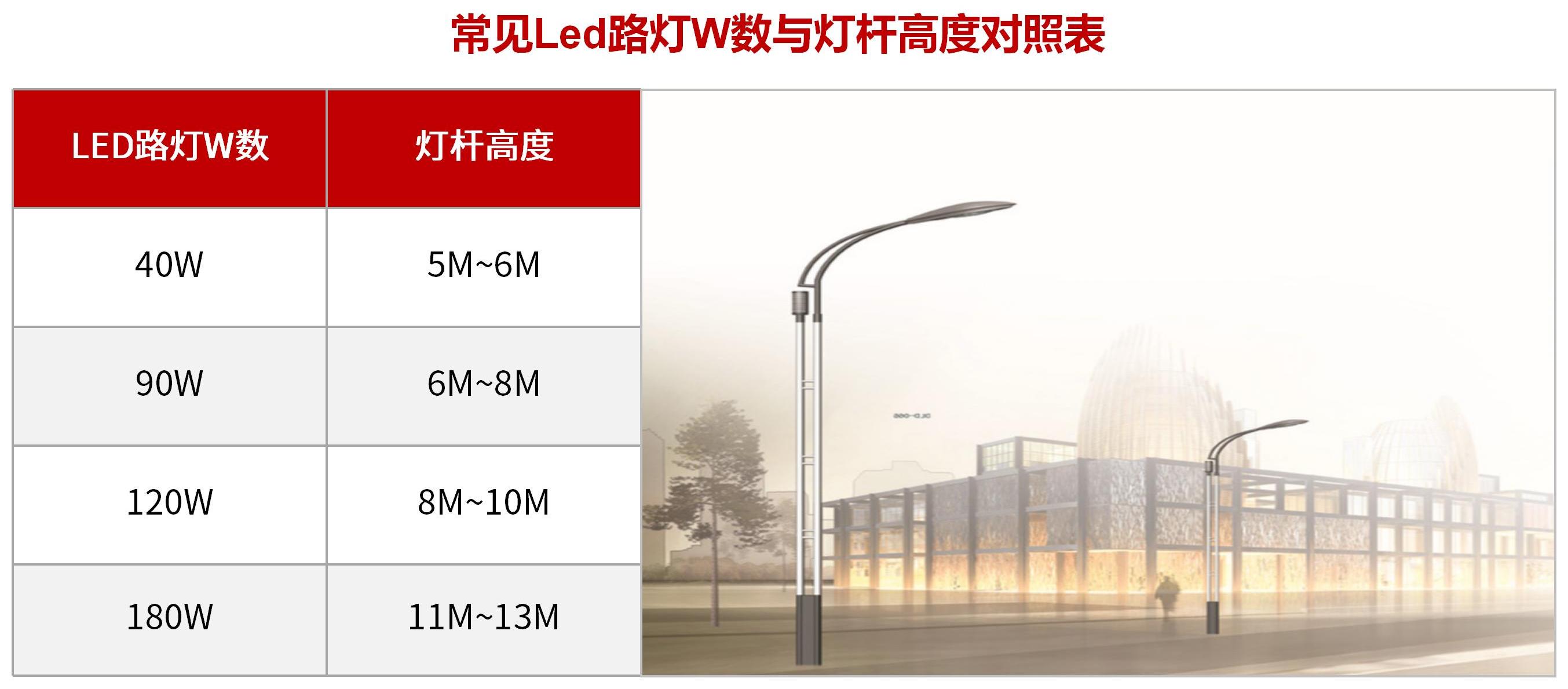

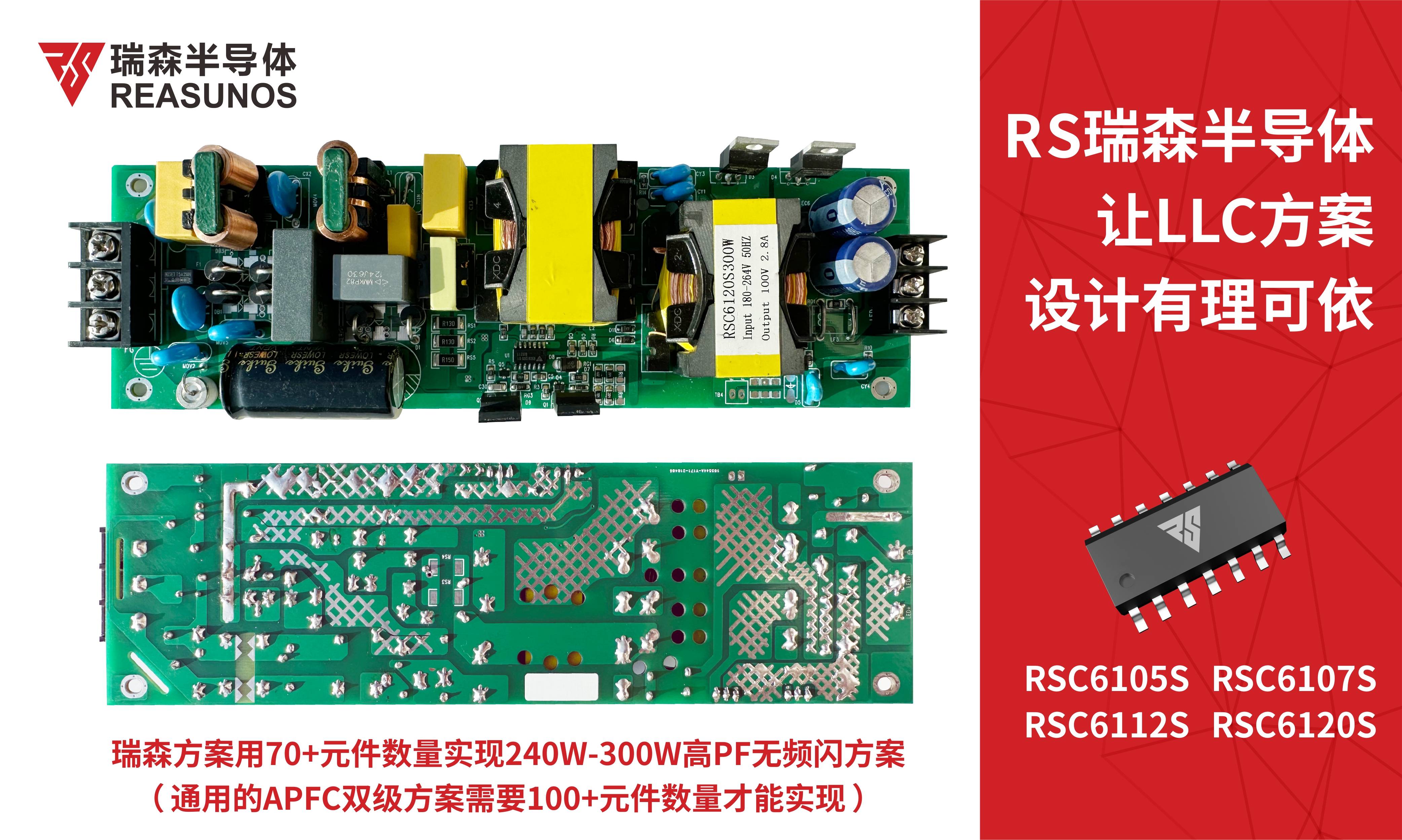

RS瑞森半導體LLC恒流方案在路燈照明的案例分享

RS瑞森半導體LLC恒流方案在路燈照明的案例分享

PMP22088.1-LLC 諧振轉換器控制卡 PCB layout設計

RS瑞森半導體助力實現優秀LLC諧振方案--PCB LAYOUT

RS瑞森半導體助力實現優秀LLC諧振方案--PCB LAYOUT

評論