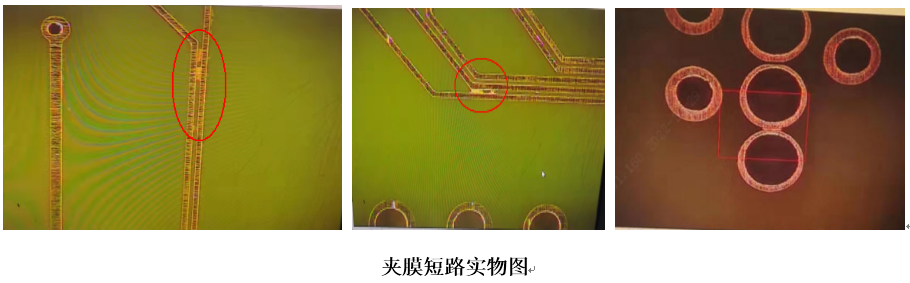

傳統(tǒng)PCB制作流程有兩種:正片圖電流程和負(fù)片直蝕流程,兩種流程對線路圖形的設(shè)計(jì)要求各不相同。特別是正片流程,如果外層線路設(shè)計(jì)不合理,如有大的空曠獨(dú)立線路,會(huì)在圖電時(shí)產(chǎn)生夾膜問題,導(dǎo)致蝕刻時(shí)短路。

為什么正片圖電流程空曠區(qū)這種小間隙的位置會(huì)更容易產(chǎn)生蝕刻不凈短路,首先要了解一下正片圖電流程的生產(chǎn)過程:前工序--à沉銅/板電--à線路圖形轉(zhuǎn)移--à圖電(鍍銅鍍錫)--à退錫蝕刻--à后工序。

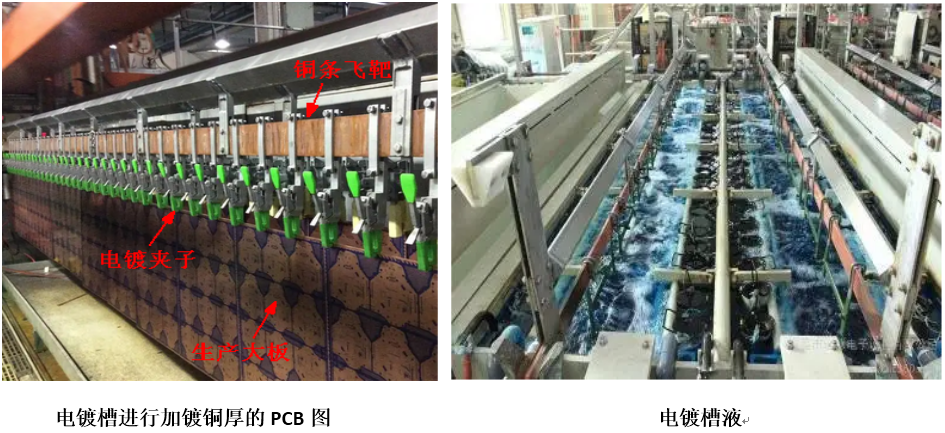

電鍍的原理是將生產(chǎn)大板并排夾在一條銅條飛靶上,再把板子放到含有銅離子的電鍍槽液中,電流通過銅條飛靶傳遞到板子上,板子上露出銅面的地方在電流的作用下,會(huì)吸附電鍍槽液中的銅的離子,并還原成銅原子。

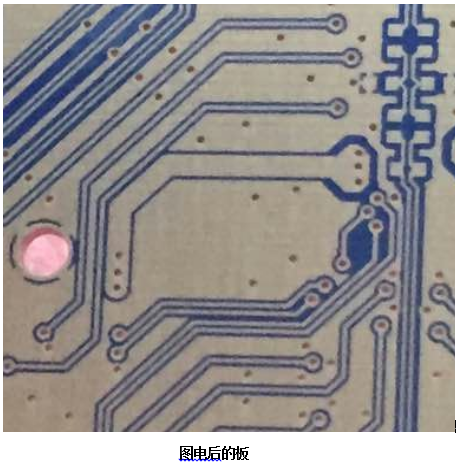

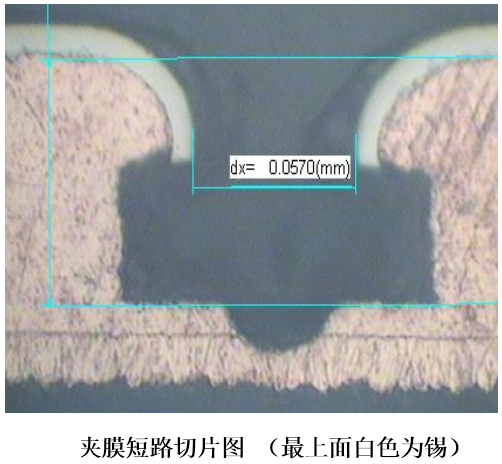

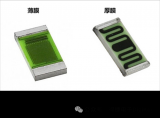

下圖藍(lán)色為干膜,白色為圖電后的線路及銅面,圖電為先鍍銅,后鍍錫,蝕刻時(shí)用錫來保護(hù)走線及銅面的,所以圖電后板面有一層白色的錫,蝕刻前需板藍(lán)色的干膜先退洗掉,露出銅面過行蝕刻,蝕刻后再把錫退先掉,就得到我們想要線路圖形了。

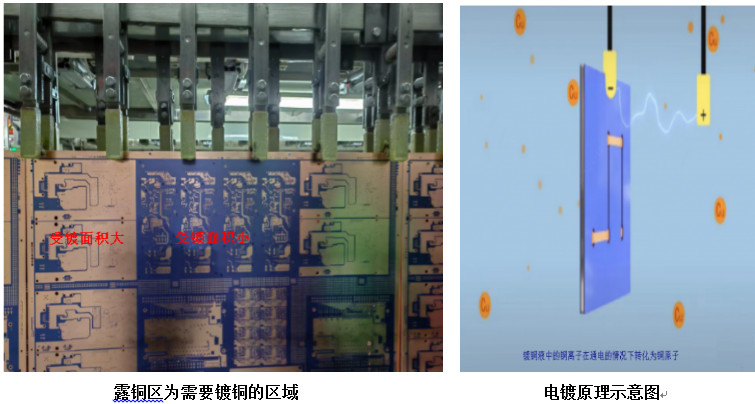

電流的大小與受鍍面積有關(guān),如果板子上線路分布太過空曠,特別是分布不均勻的獨(dú)立線區(qū)域,所受到的電流非常大,嚴(yán)重會(huì)導(dǎo)致電流過大燒板,輕則導(dǎo)致獨(dú)立線區(qū)域鍍銅很厚,當(dāng)線與線,線與焊盤,焊盤與焊盤等間隙過小時(shí),如4mil以下間隙,則會(huì)導(dǎo)致這些間隙過小的地方存在線路板行業(yè)經(jīng)常說的一個(gè)名詞叫“夾膜”就是把下圖中的干膜夾在中間,導(dǎo)致后續(xù)的不能蝕刻,從而造成品質(zhì)問題。

以上說的夾膜,可能有些小伙伴不太理解,做正片線路工藝也叫圖電工藝,做外層線路時(shí)先在板面上壓干膜,再通過曝光,顯影等工序,露出需要電鍍的走線及銅面,成品無銅區(qū)域會(huì)被干膜覆蓋,這樣電鍍就只會(huì)鍍我們需要的走線及孔壁銅等,夾膜是指當(dāng)線路間隙較小時(shí),如果鋪銅不均勻或是沒有鋪銅的線路,電鍍時(shí)走線銅厚會(huì)超過干膜的厚度,隨著電鍍時(shí)間的增加,電鍍銅錫就有可能會(huì)從干膜兩側(cè)延伸包裹干膜,這種現(xiàn)象就稱為夾膜。在蝕刻時(shí)需要先把干膜退洗掉,露出需要蝕刻的銅面,而夾膜的地方干膜就無法完全去掉,由于干膜本身也是抗蝕層,蝕刻時(shí)此處的銅就保留下來造成板子短路。

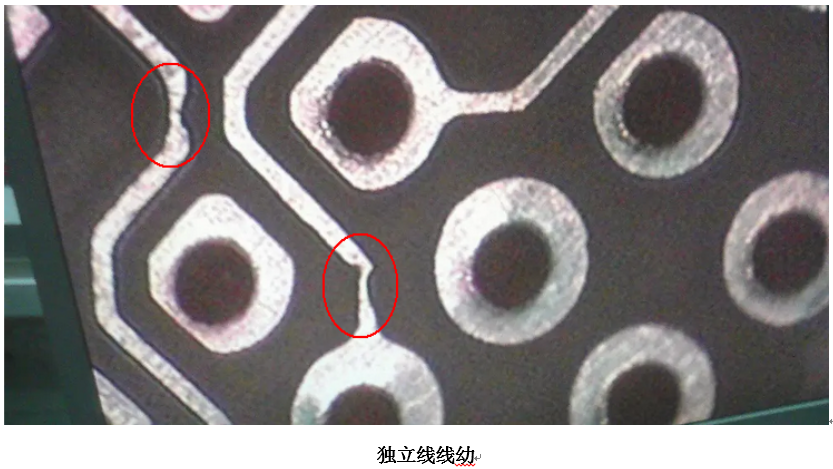

除夾膜外,獨(dú)立線路還會(huì)因?yàn)榭諘鐓^(qū)蝕刻藥水活性大,咬蝕過快,導(dǎo)致線幼。

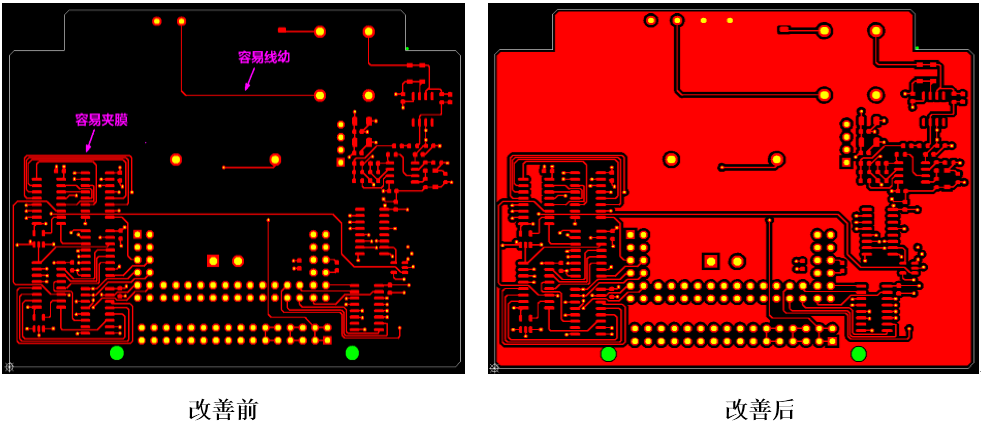

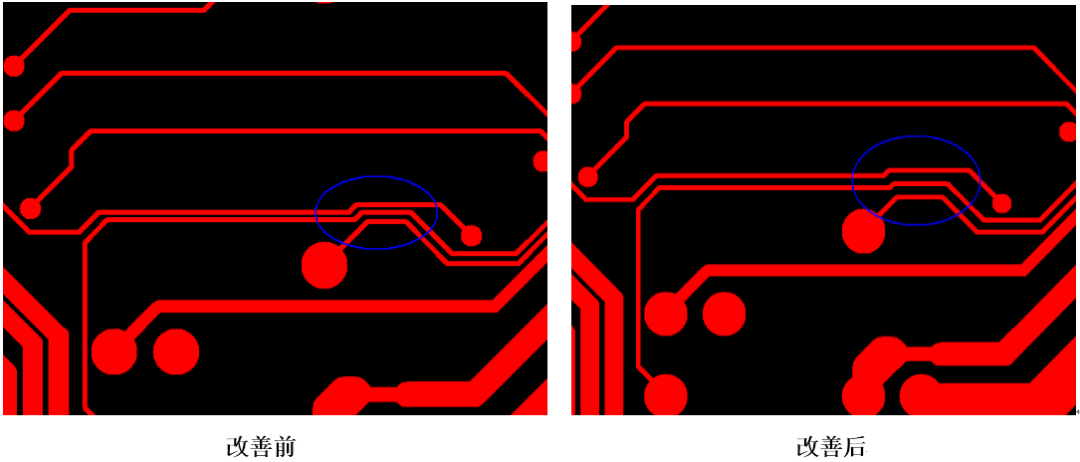

改善建議:

(1)空曠區(qū)鋪銅 ,提高受鍍面積,保證電鍍均勻。

(2)無法鋪銅時(shí),可以加大獨(dú)立區(qū)線距至6mil以上(1OZ)

審核編輯 :郭婷

-

pcb

+關(guān)注

關(guān)注

4319文章

23111瀏覽量

398241

原文標(biāo)題:電鍍夾膜成因及改善方法

文章出處:【微信號:孺子牛PCB,微信公眾號:孺子牛PCB】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

電鍍膜的性能測試方法

電鍍工藝流程詳解 電鍍技術(shù)在工業(yè)中的應(yīng)用

精密連接器件電鍍金異常的原因分析參考

電源整流器對電鍍的影響

導(dǎo)光膜和擴(kuò)散膜的區(qū)別

開爾文測夾四根線怎么接

微流控光刻掩膜制作

THS4303針對低頻段的電流增幅較大,有什么好的建議或改善措施嗎?

常見的錫珠形成的原因和解決方法

點(diǎn)亮創(chuàng)造力,一文詳解pcb電鍍金

USB-C 舌片發(fā)白是什么原因?如何改善?

精密五金電鍍中常見的八種不良問題及原因分析

華為pockets折疊屏手機(jī)怎么貼膜

常見雜音問題及形成原理知識歸納

電鍍夾膜形成的原因及改善建議

電鍍夾膜形成的原因及改善建議

評論