構建自定義 AXI4-Stream FIR 濾波器

副標題:優秀的IC/FPGA開源項目(五)-在Vivado中構建自定義 AXI4-Stream FIR 濾波器 IP

《優秀的IC/FPGA開源項目》是新開的系列,旨在介紹單一項目,會比《優秀的 Verilog/FPGA開源項目》內容介紹更加詳細,包括但不限于綜合、上板測試等。兩者相輔相成,互補互充~

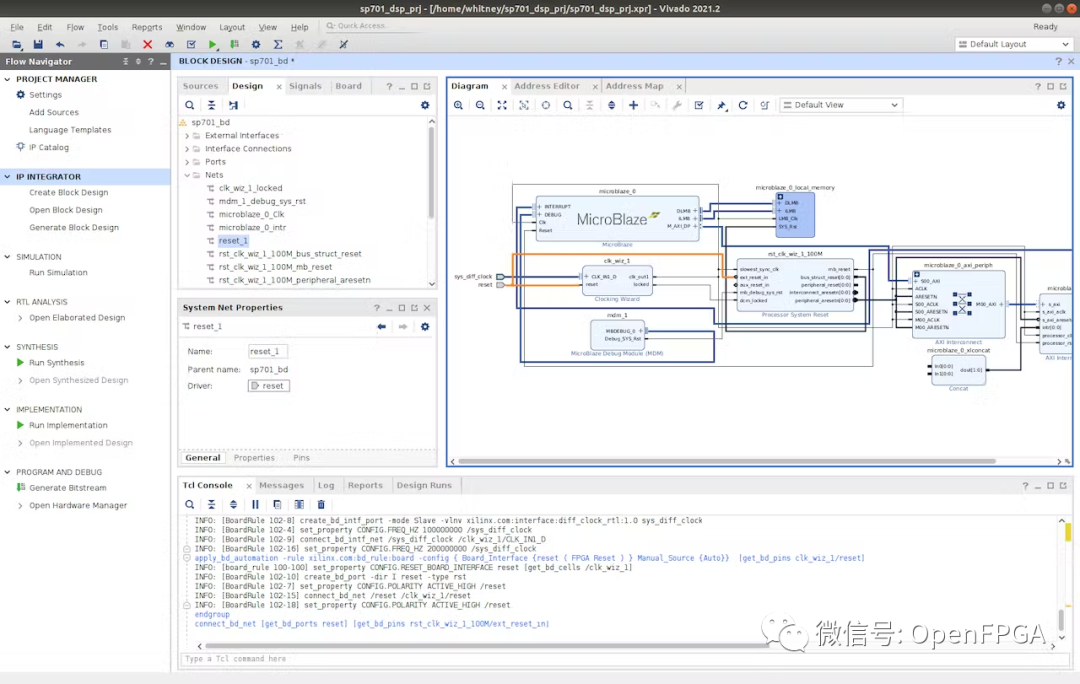

AMD-Xilinx 的 Vivado 開發工具具有很多方便FPGA開發功能,我最喜歡的功能之一是block design的設計流程。Vivado 中的block design是使用RTL IP形式的圖形表示進行設計,在block design中使用 RTL 模塊的方便之處在于,它將自動檢測某些類型的信號,例如時鐘、復位和總線接口,然后,檢測這些信號進行IP間的自動化連接。Vivado 中包含大量預構建 IP 模塊(官方IP)。

為了方便用戶進行相關設計,Vivado 提供了一個內置的 IP 封裝編輯器工具,它可以為 AXI IP 生成框架,只需將自己的 RTL 代碼插入其中。同時也提供了相關的驅動文件,可以在Vitis中方便調試。

為了演示究竟上面流程“好”在哪里,接下來我們創建一個AXI FIR IP 模塊,然后將IP添加到我們設計中最后驗證功能。

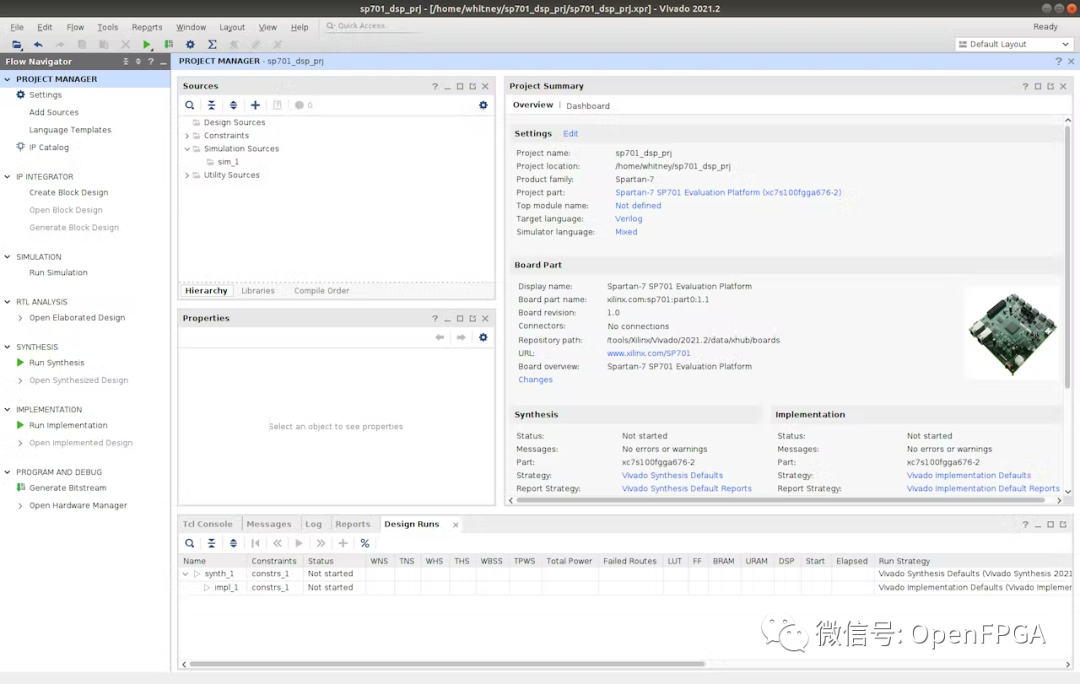

創建 Vivado 項目

首先,啟動 Vivado 并針對自己的FPGA創建一個新項目。

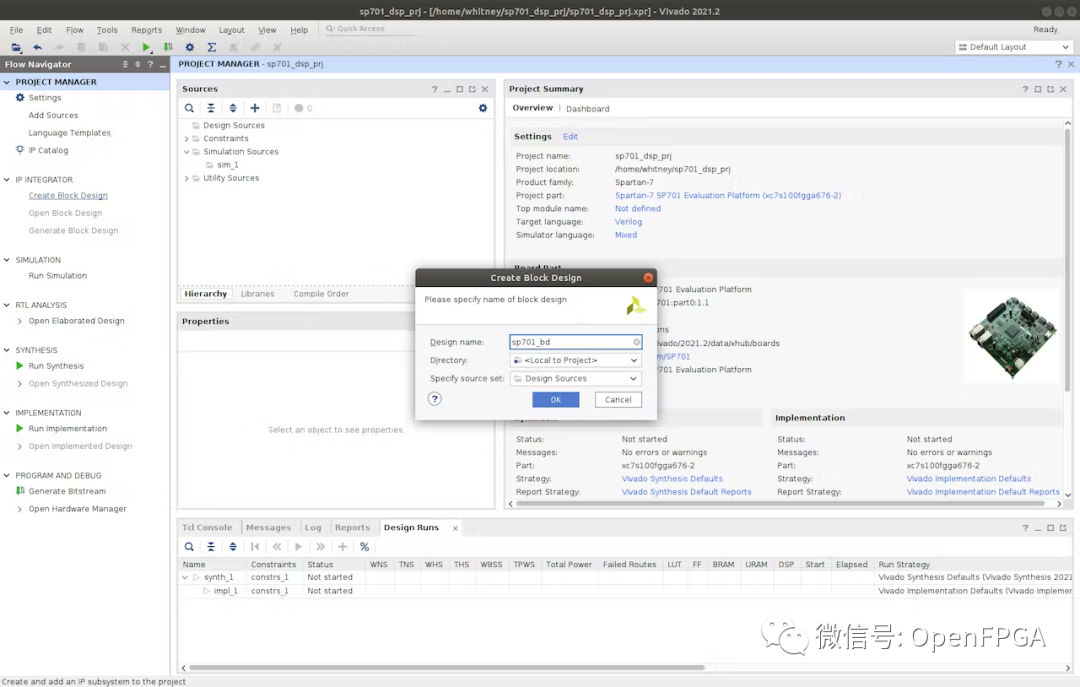

添加 MicroBlaze,對于這個項目來說,使用 BRAM 就足夠了。

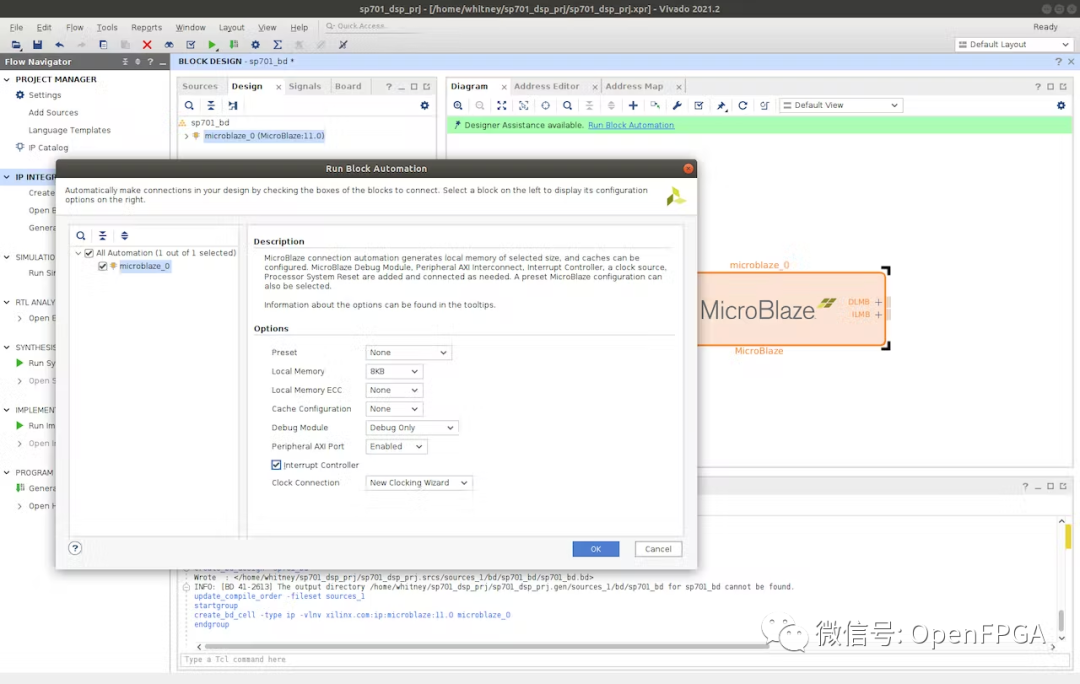

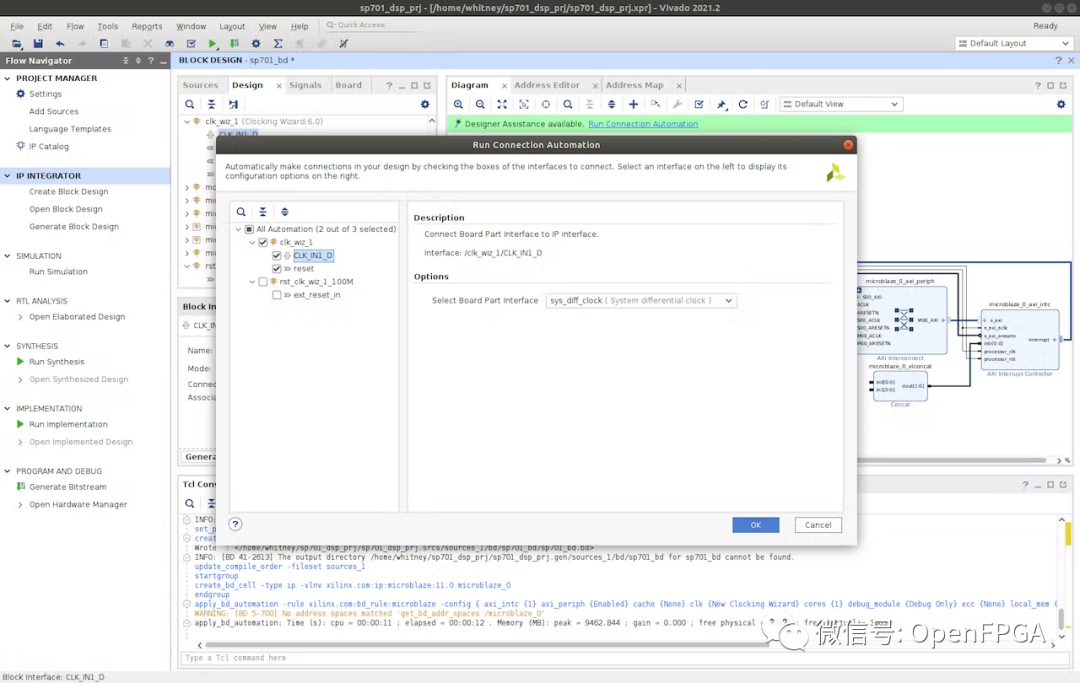

選擇 Add IP 選項并搜索 MicroBlaze,將其添加到模塊設計中并運行 Block Automation,該模塊會在窗口頂部的綠色橫幅中彈出。接下來添加中斷控制器。

驗證并保存塊設計,接下來我們將開始我們的IP設計。

創建新的 AXI4 外設

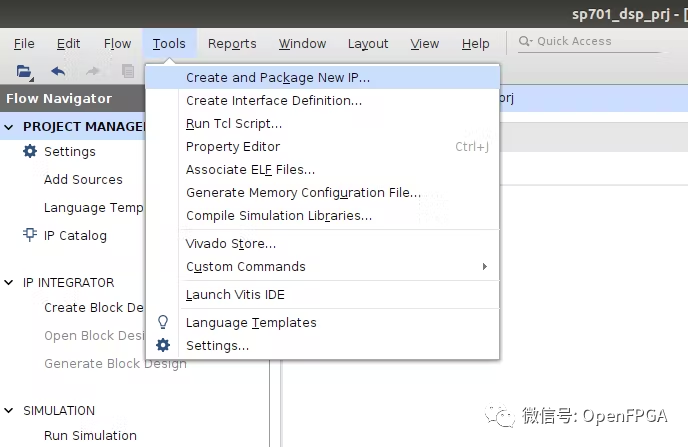

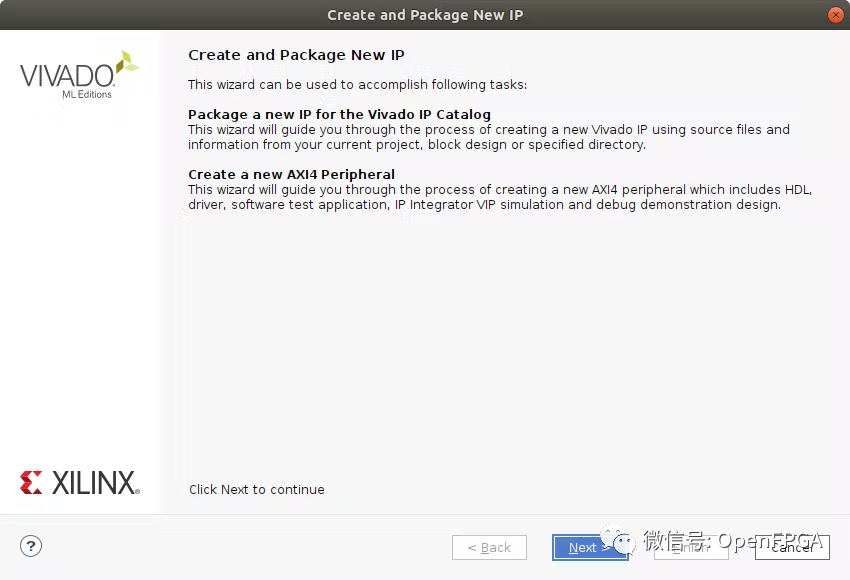

要使用自己的 RTL 創建新的 AXI 外設并將其封裝為 IP ,請選擇工具>創建和打包新 IP...

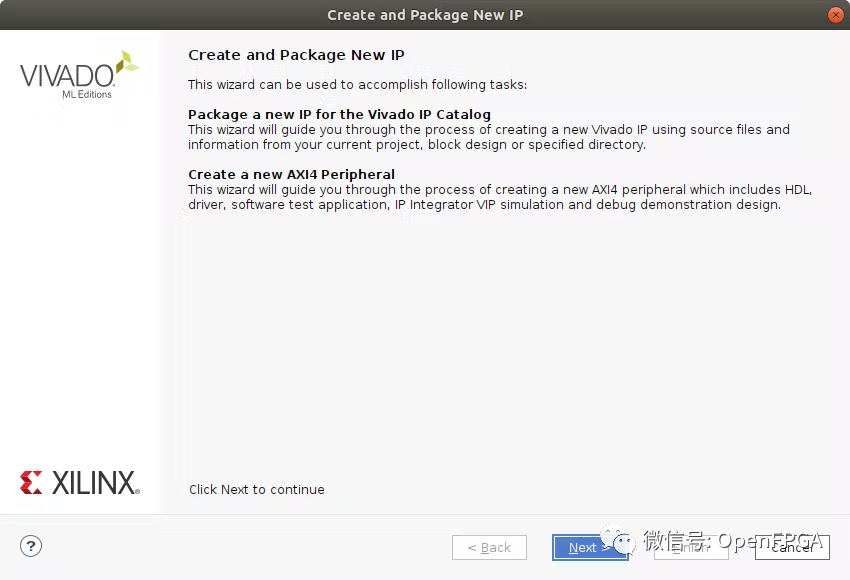

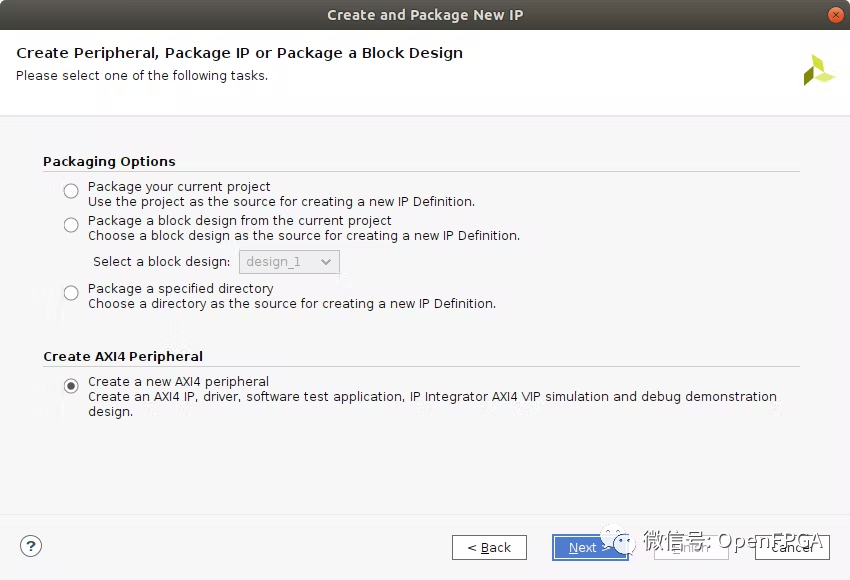

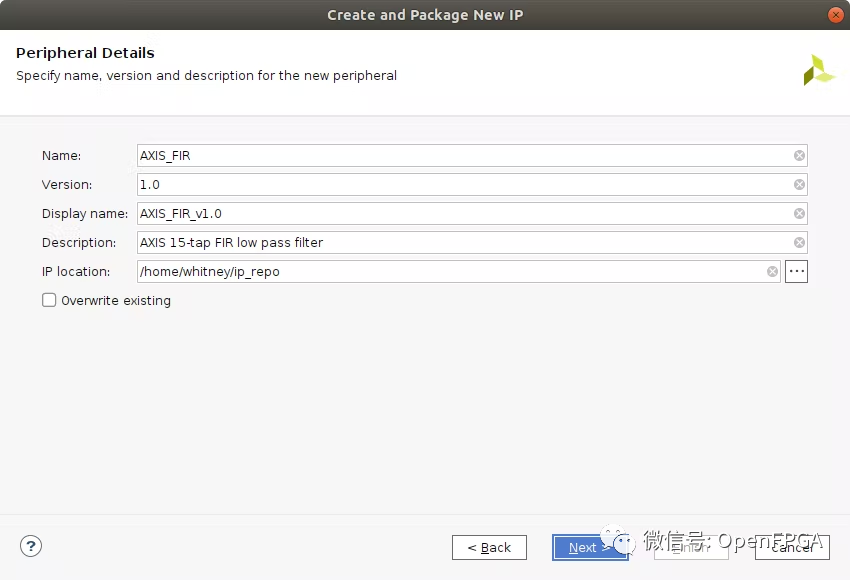

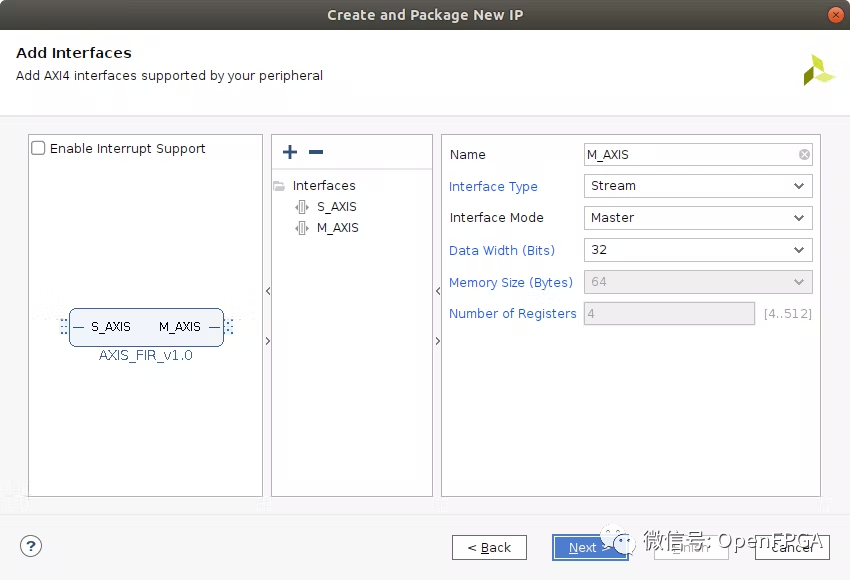

在彈出的窗口中,按照提示逐步瀏覽屏幕,選擇Create AXI4 Peripheral選項,指定 IP 塊的所需名稱、位置目錄以及 IP 將具有的 AXI 接口數量以及 AXI類型。

Vivado 中使用了三種主要類型的 AXI:

- AXI4 (full)

- AXI4-Lite

- AXI4-Stream

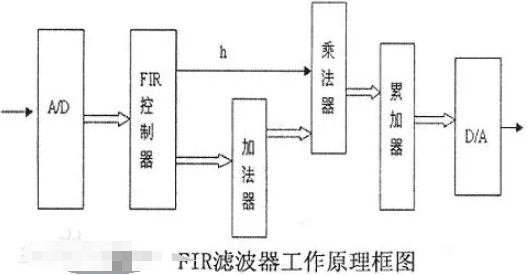

每種類型都適合不同的用例,在這個項目中,我們正在創建自己的 AXI FIR 濾波器 IP 。由于 FIR 濾波器輸入并輸出具有已知數據包邊界和流量控制要求的恒定數據流,因此 AXI4-Stream 是最適合的類型。它將需要一個從接口來輸入數據樣本,并需要一個主接口來輸出處理后的樣本。

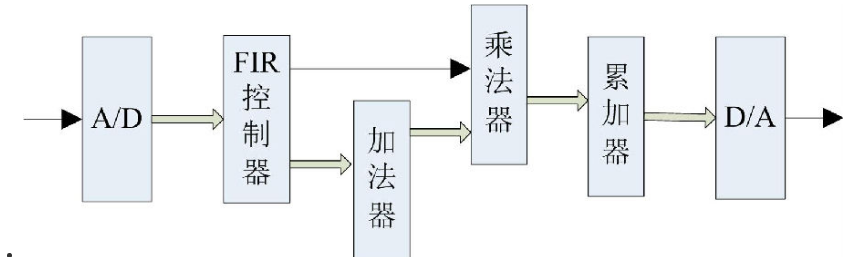

作為參考,FIR 是一個運行速度為 100 MS/s 的 LPF,具有 15 個抽頭,接收帶符號的 16 位數據并輸出帶符號的 32 位數據。它有一個從 1MHz 到 10MHz 的通帶和一個從 20MHz 開始的阻帶。

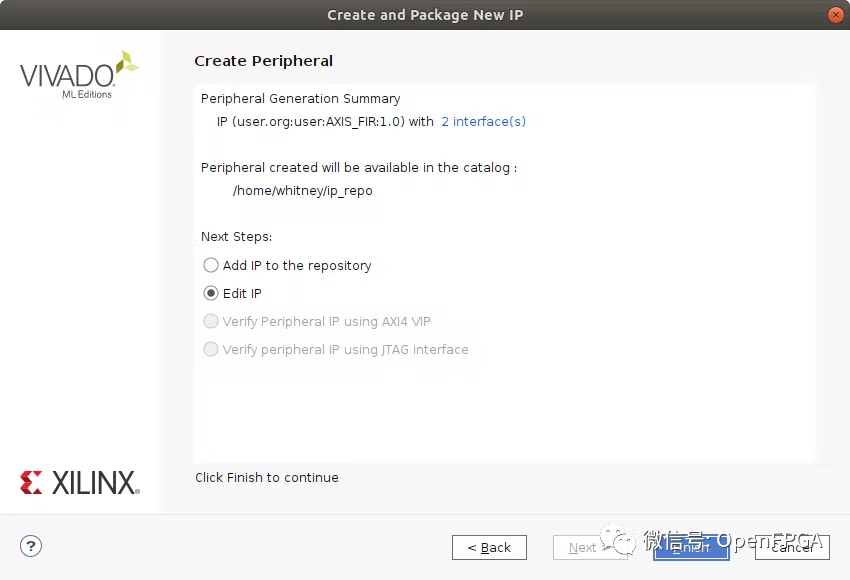

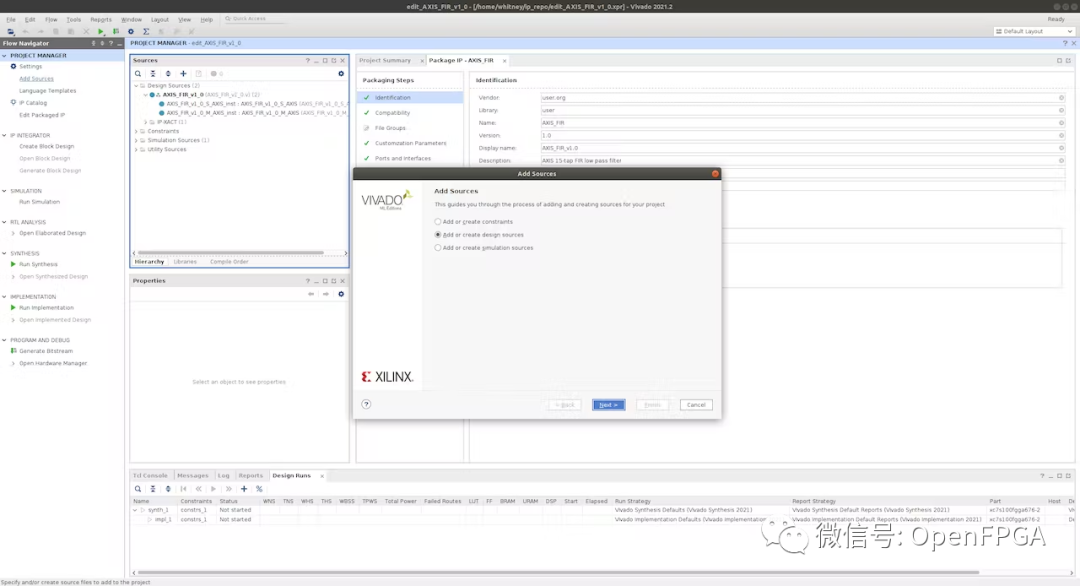

接下來,選擇編輯 IP并單擊完成。IP 包編輯 Vivado 項目將重新打開一個gui。

將自定義 RTL 添加到 AXI4-Stream IP

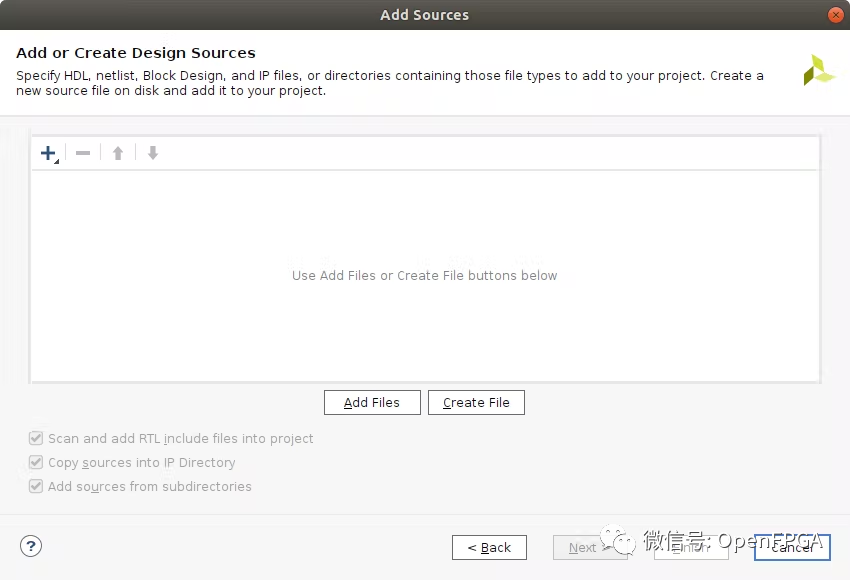

從Flow Navigator中選擇Add Sources添加我們要設計的 FIR Verilog 文件。

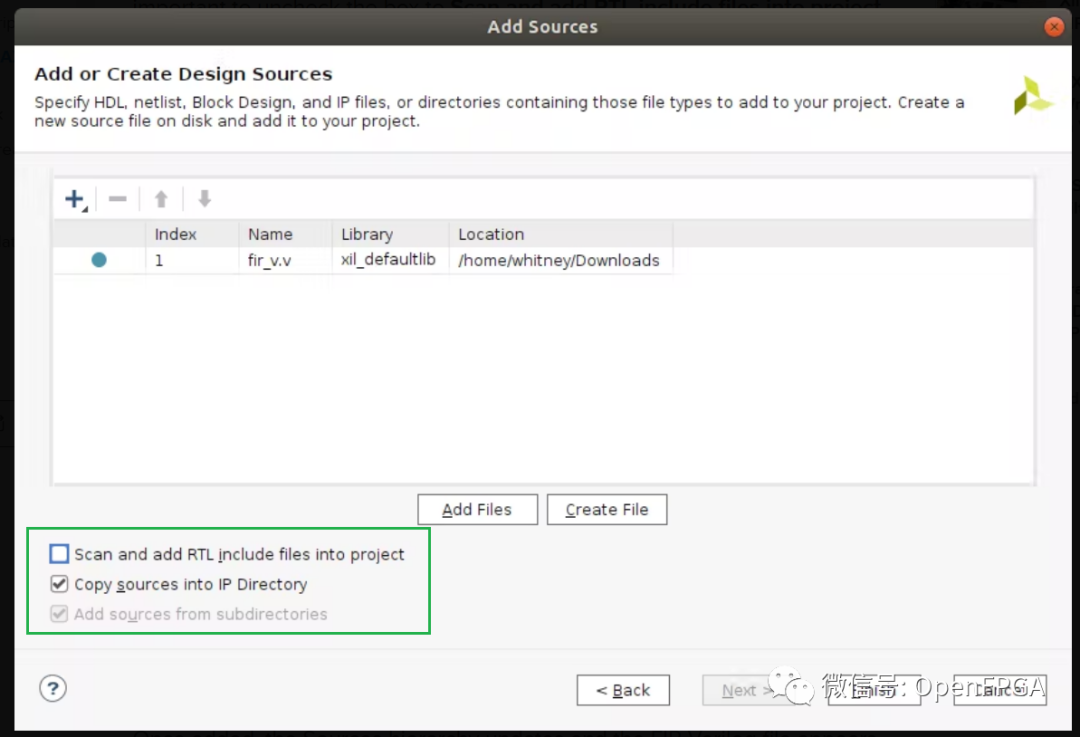

在使用 Add Files 選項指向 FIR Verilog 文件后,取消選中Scan and add RTL include files into project復選框。由于這不是一個普通的 Vivado 項目,并且 Verilog 代碼被打包到一個 IP 塊中,因此選中該選項后將引發錯誤。

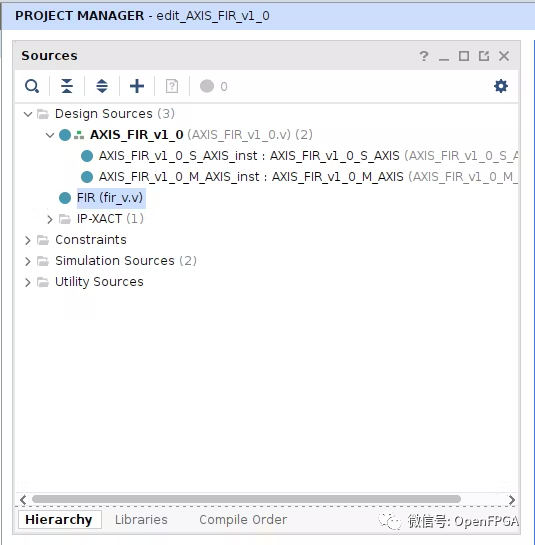

添加后,源層次結構更新并且 FIR Verilog 文件獨立于 AXI Verilog 源文件。

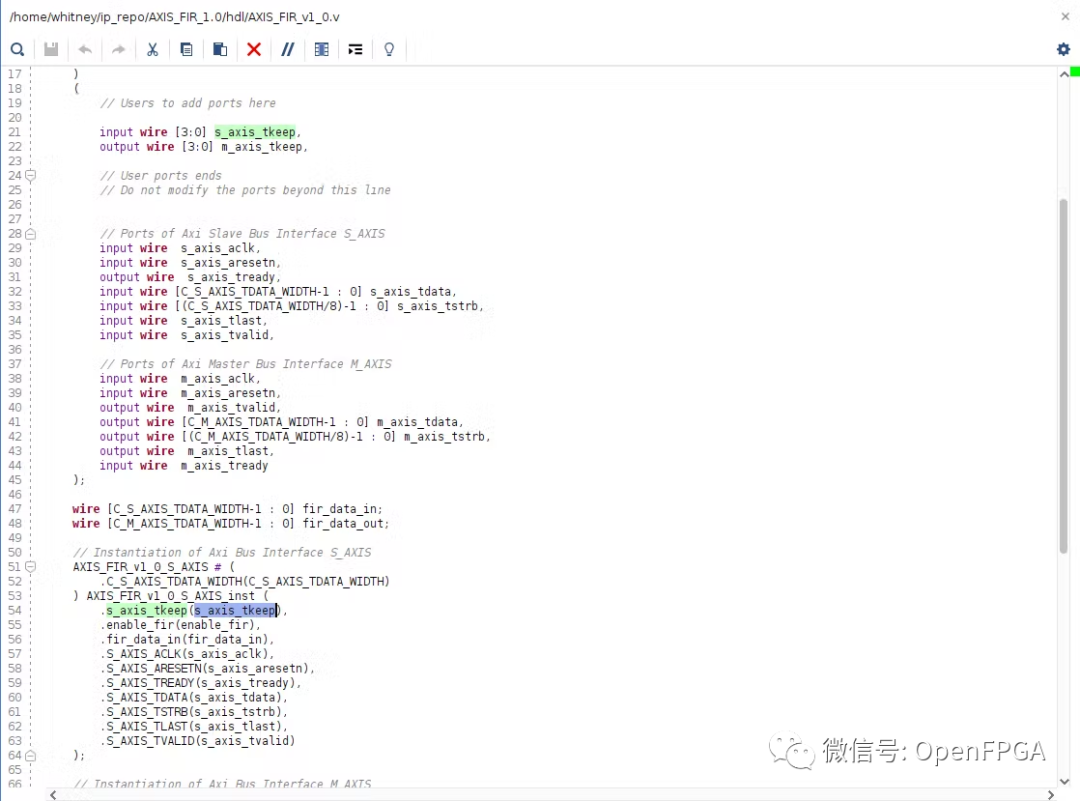

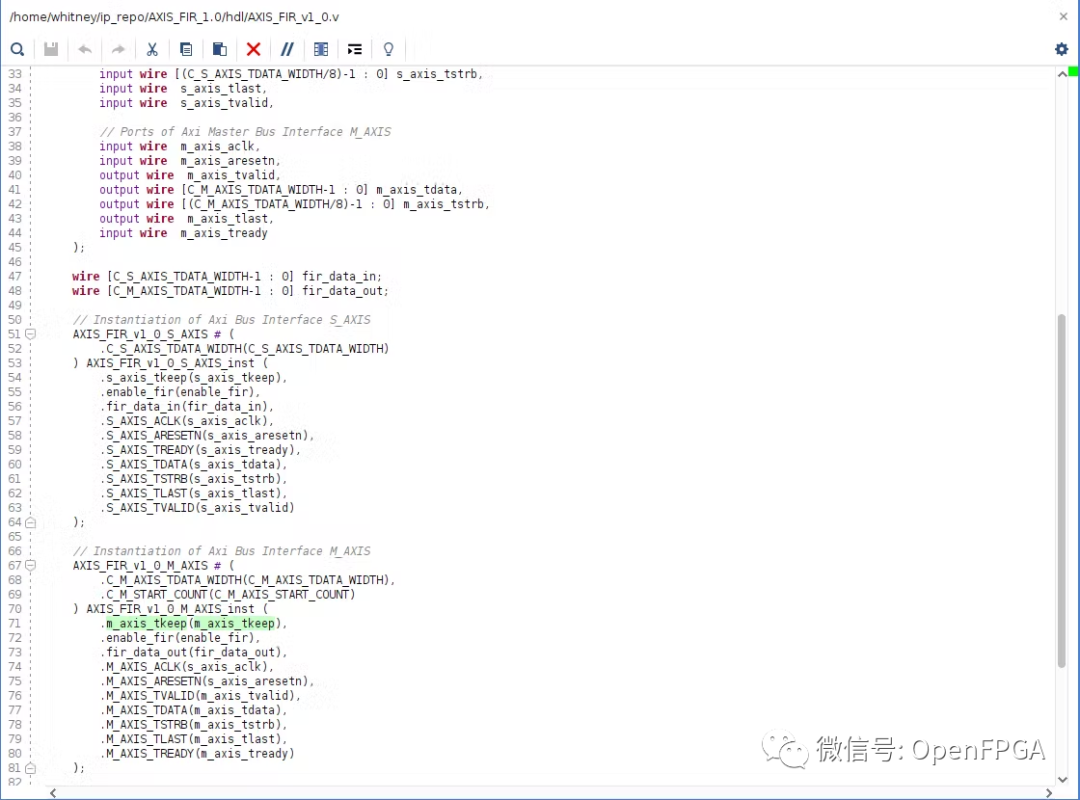

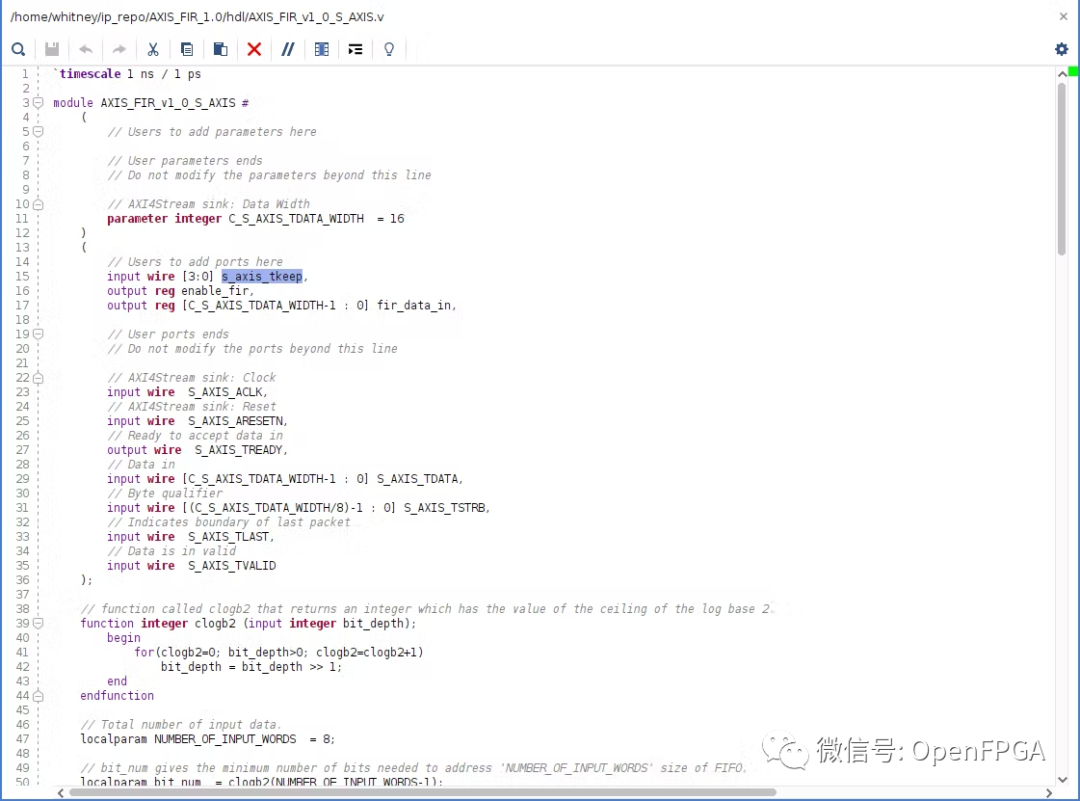

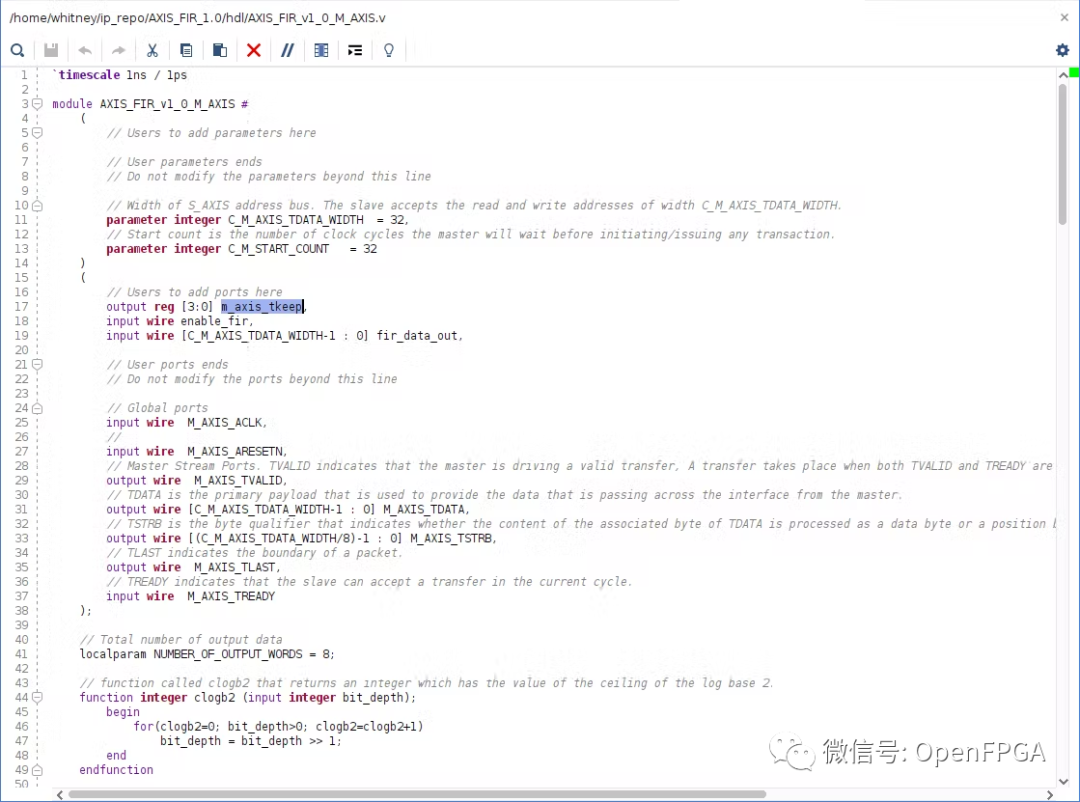

根據生成 IP 編輯器 Vivado 項目時所做的選擇,會為此 AXI4-Stream 外設生成三個 RTL 源文件:

- 從接口功能 RTL。

- 主接口功能 RTL。

- 具有物理接口聲明和主從接口實例化的頂層文件。

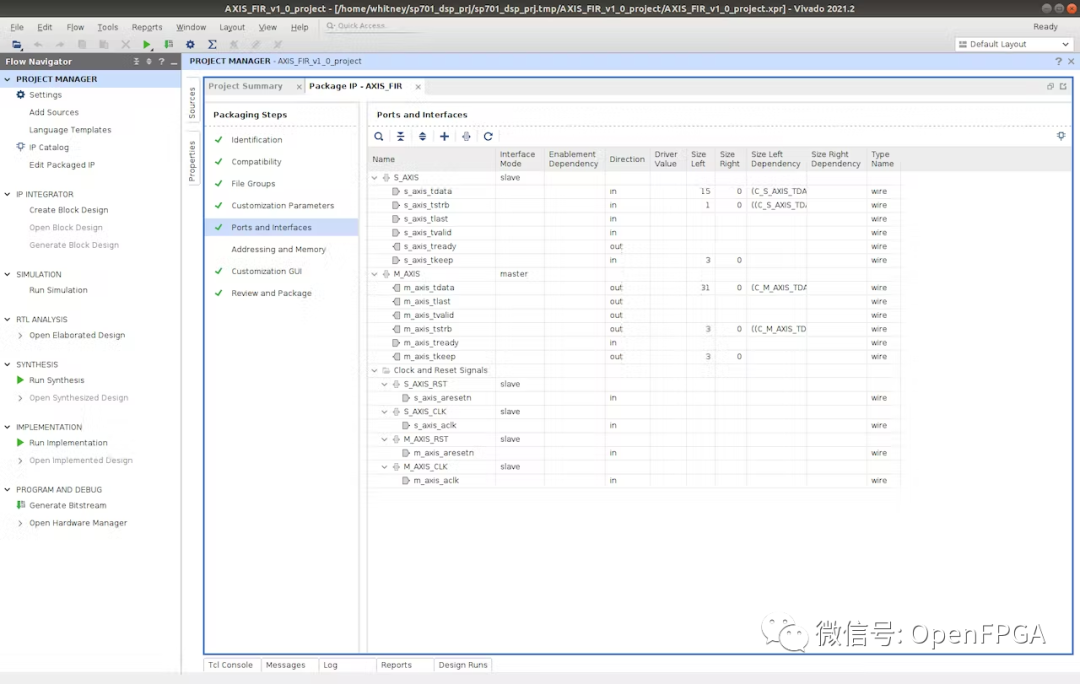

在設計之前,需要將幾個默認未啟用的可選 AXI4-Stream 接口信號添加到主 AXI 端口和從 AXI 端口。大多數 DSP IP 模塊,例如 DDS 利用了 AXI4-Stream 額外的keep 和 tlast信號。

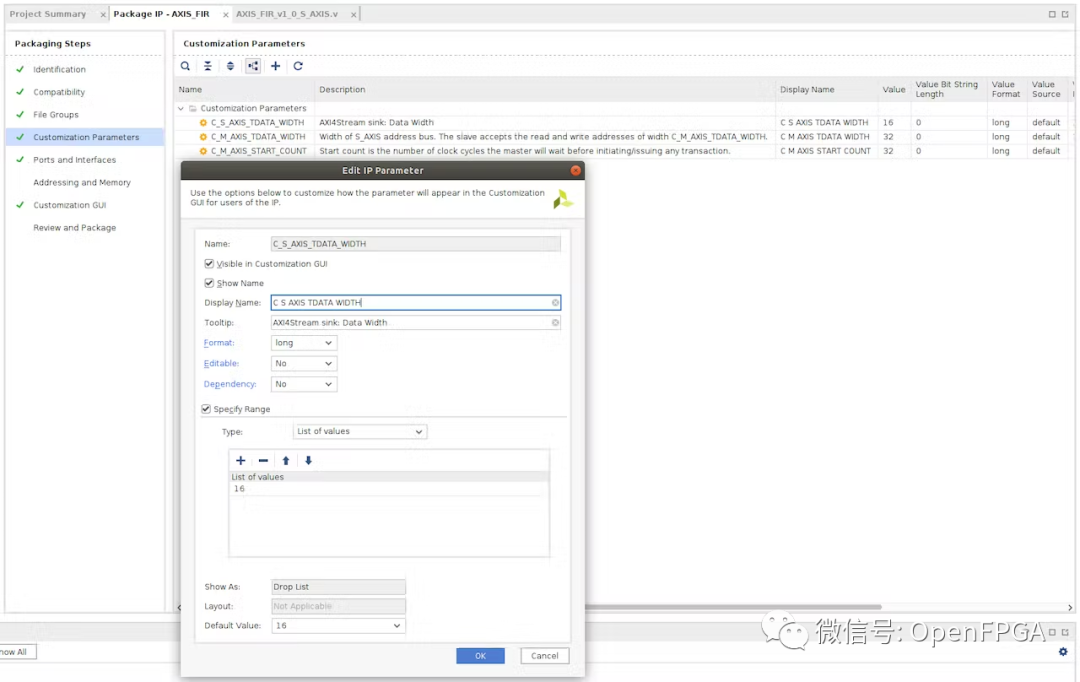

添加這些可選信號很簡單,但最初并不清楚。導航到Package IP窗口中的Customization Parameters選項卡。

主接口和從接口都需要添加它們,因此右鍵單擊每個接口并選擇Edit Interface 。

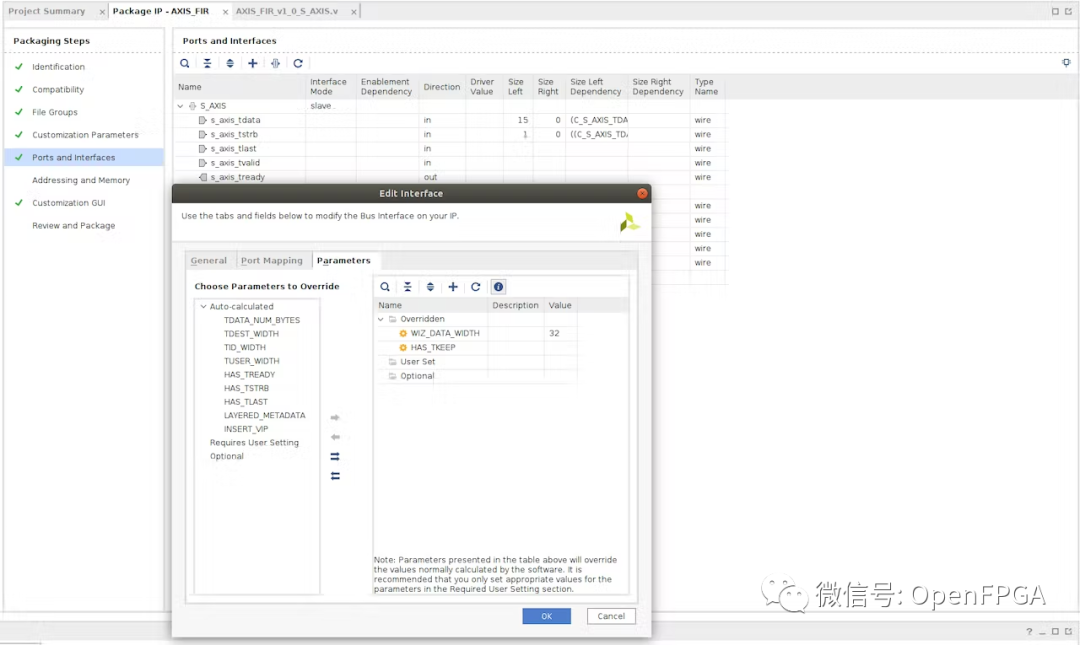

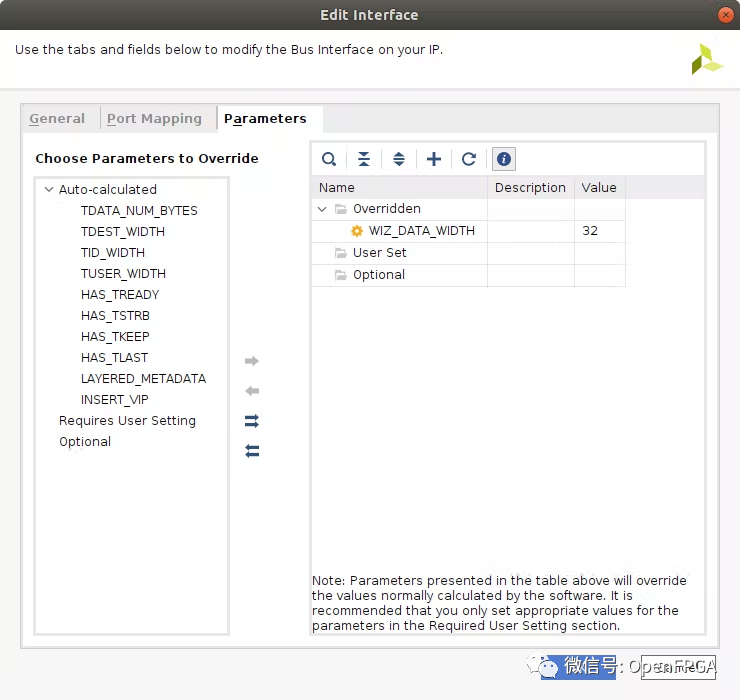

在“Parameters”選項卡中啟用HAS_TKEEP ,方法是單擊每個選項,然后單擊單個箭頭將其從左列移動到右列。

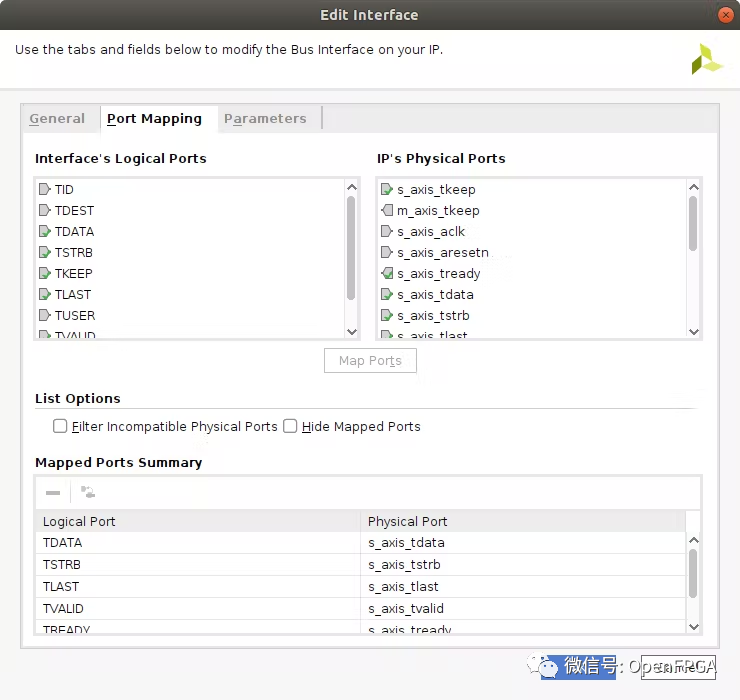

然后切換到Port Mapping選項卡,將 tkeep 和 tlast 映射到 AXI IP 塊的物理接口。在Interface's Logical Ports列和IP's Physical Ports列中分別匹配 tkeep 和 tlast 信號。然后在下面的Mapped Ports Summary列中驗證它們的映射。

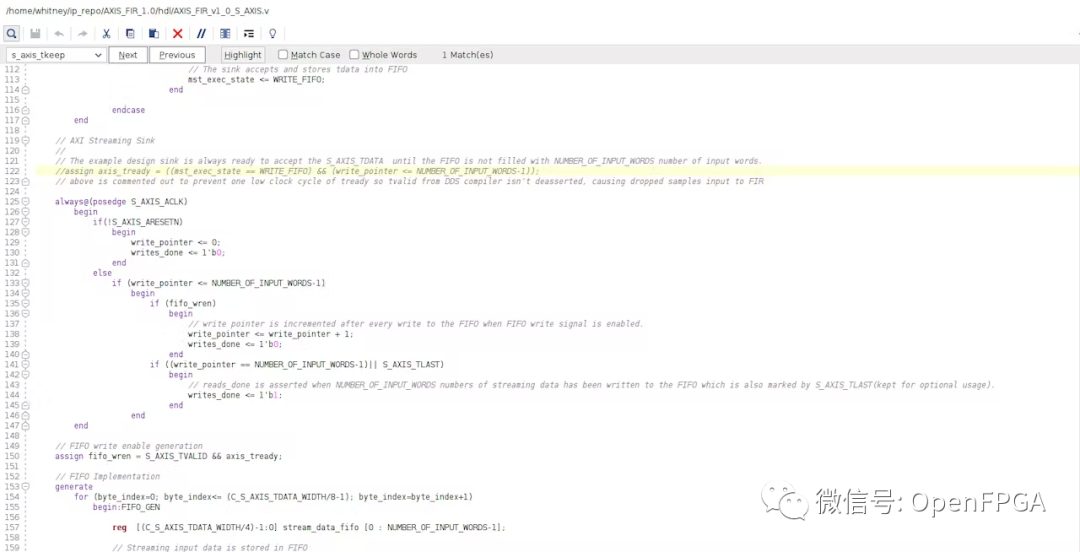

由于默認情況下不啟用 tkeep,因此還必須手動將其端口聲明添加到所有三個 AXI 接口 RTL 源文件的用戶定義端口聲明部分。它還需要添加到頂級 AXI 包裝器中的 AXI 主接口和從接口實例中。

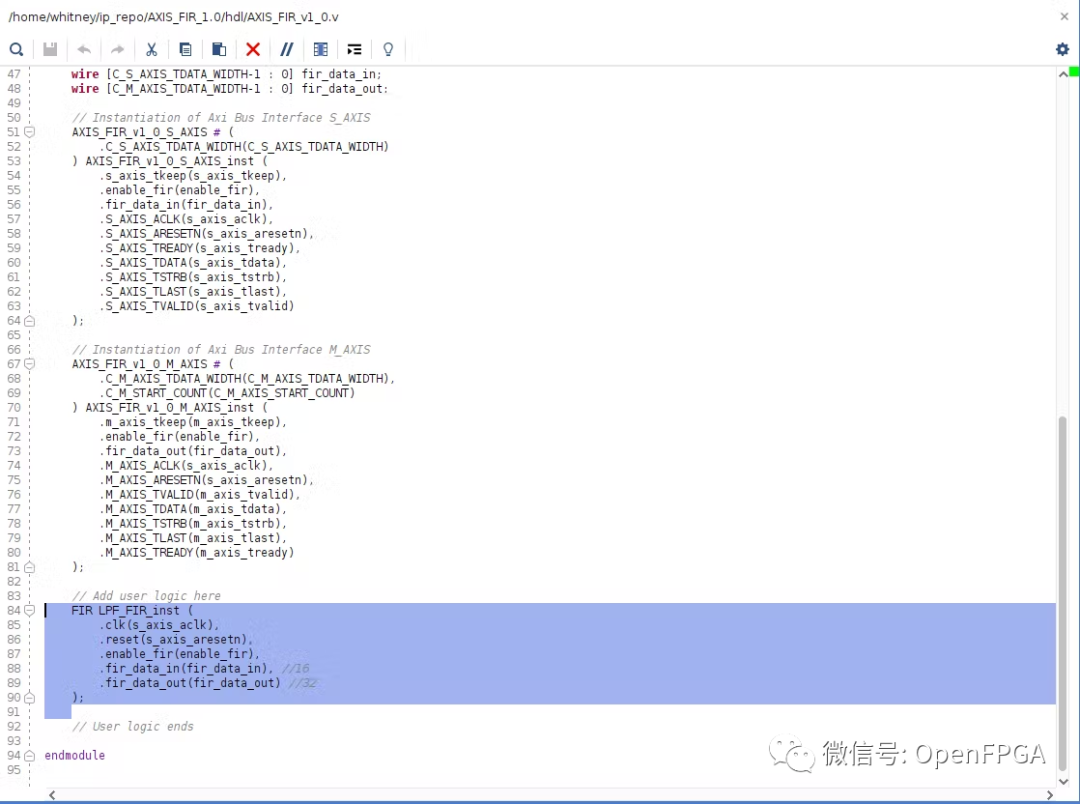

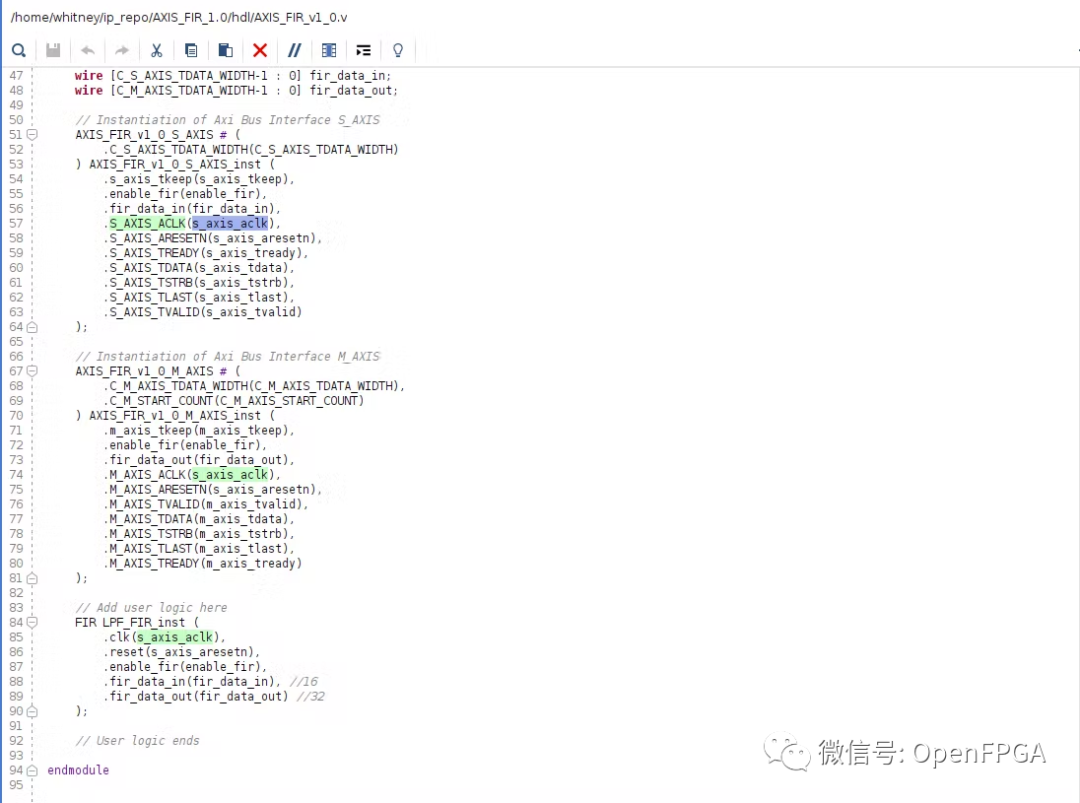

在注釋Add user logic here標記的部分中實例化 FIR Verilog 模塊。

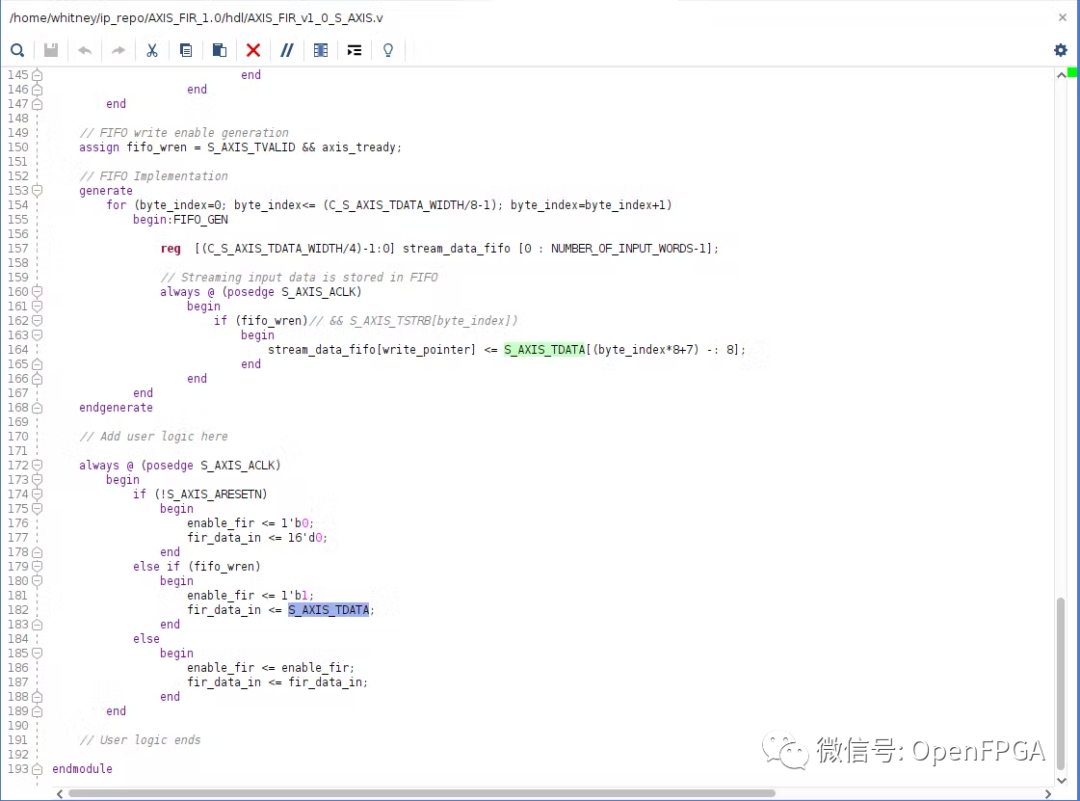

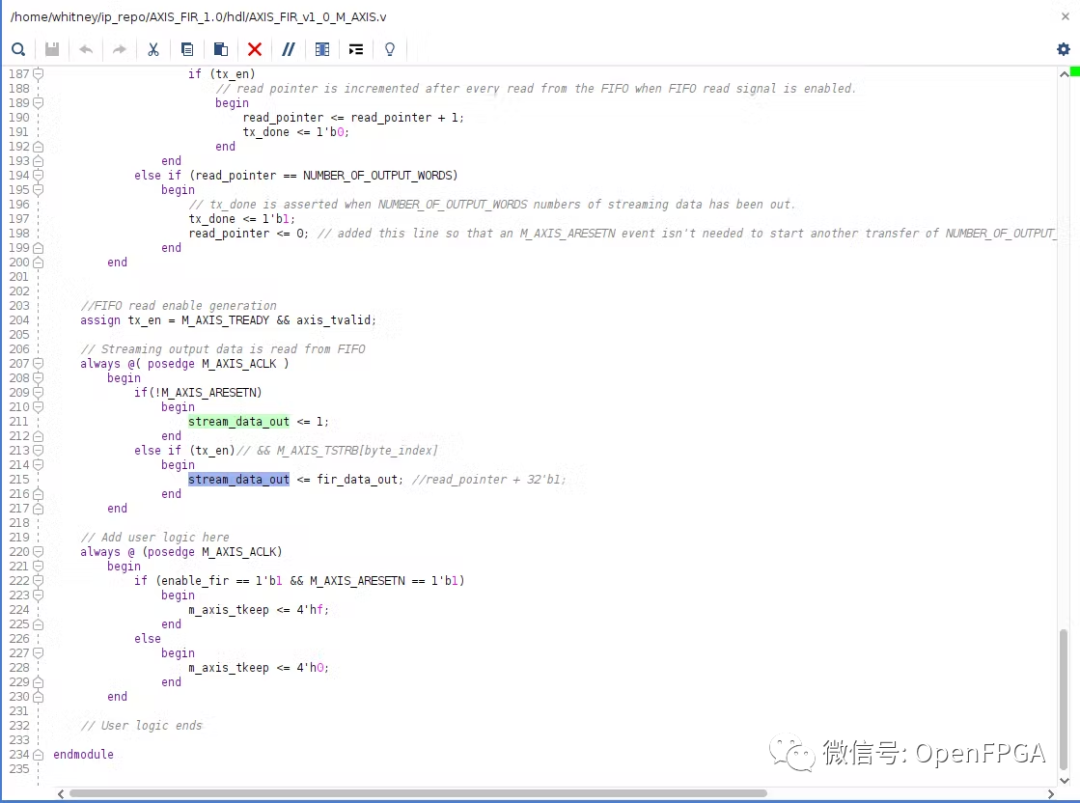

現在,雖然 AXI 接口的基本功能分別在每個 RTL 源文件中自動生成,但如何從輸入數據流中提取數據并傳遞到自己的自定義邏輯中由自己來定義。以及如何將自定義邏輯的數據輸出饋送到主 AXI 接口進行輸出。因此,會在三個自動生成的 RTL 源文件中注意到相同的 Add user 邏輯。

另一點需要注意的是,AXI4-Stream 接口的功能需要進行一些修改,以便將 tkeep 和 tlast 信號功能添加到主 AXI 接口和從 AXI 接口。

這個項目的最后一個獨特的要求是,因為這個邏輯的核心是一個 FIR 濾波器,所以主從 AXI 接口和 FIR 都需要由相同的時鐘作為 FIR 采樣時鐘。所以只是將從 AXI 接口時鐘傳遞給 FIR 和主 AXI 接口。

封裝 AXI IP 塊

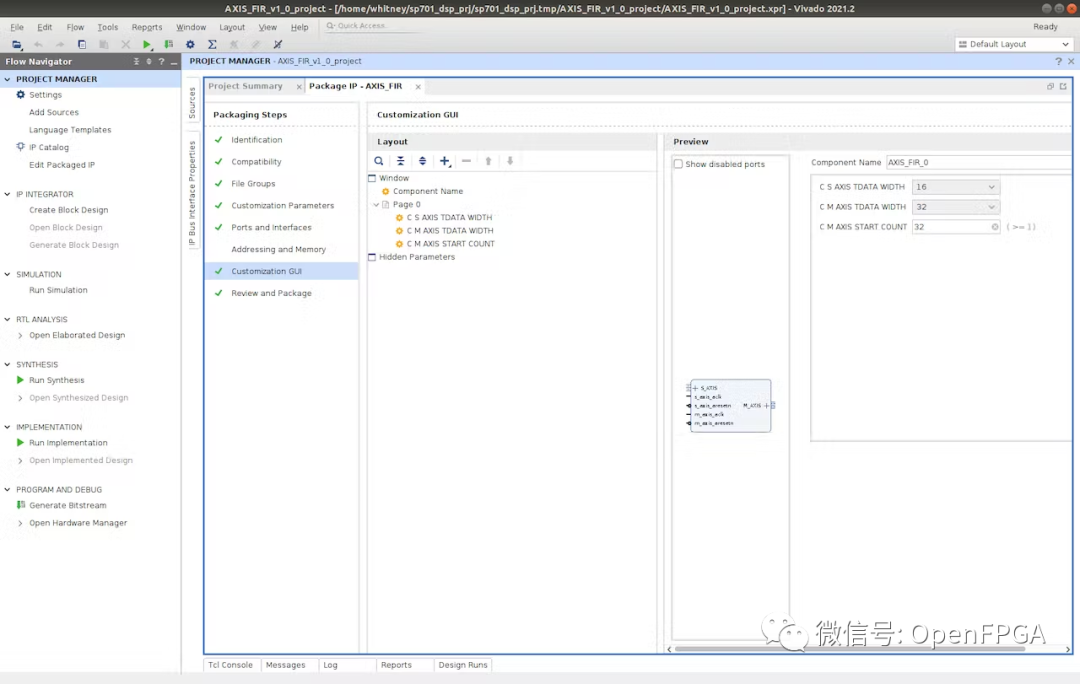

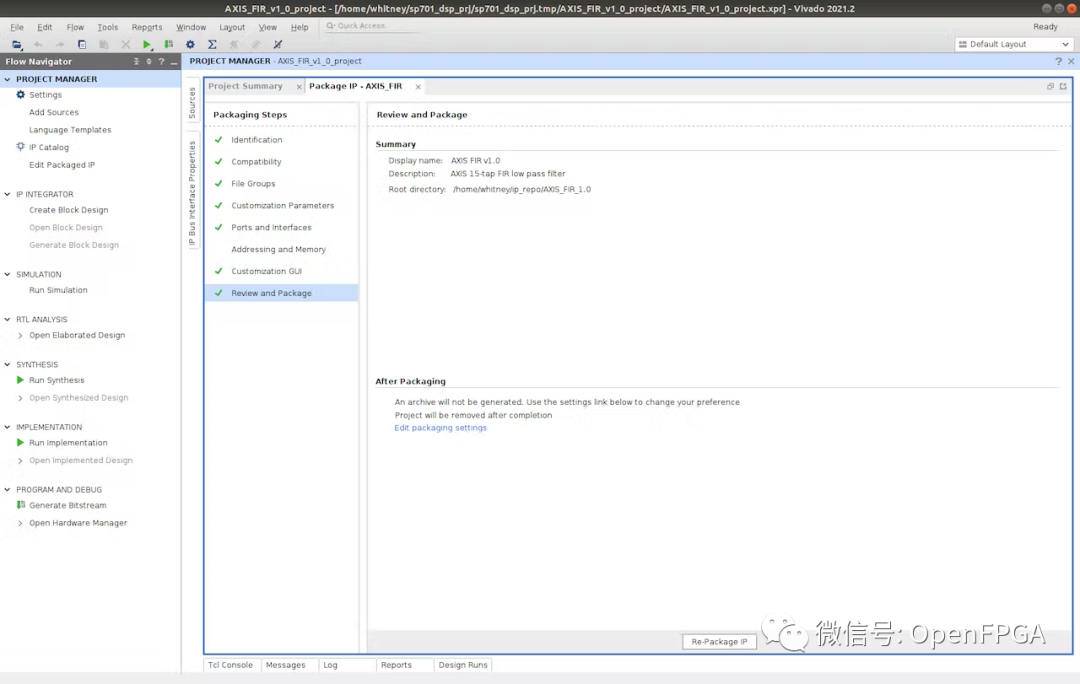

返回到 Package IP 窗口,讓我們瀏覽每個選項卡并驗證,然后最終將其打包。

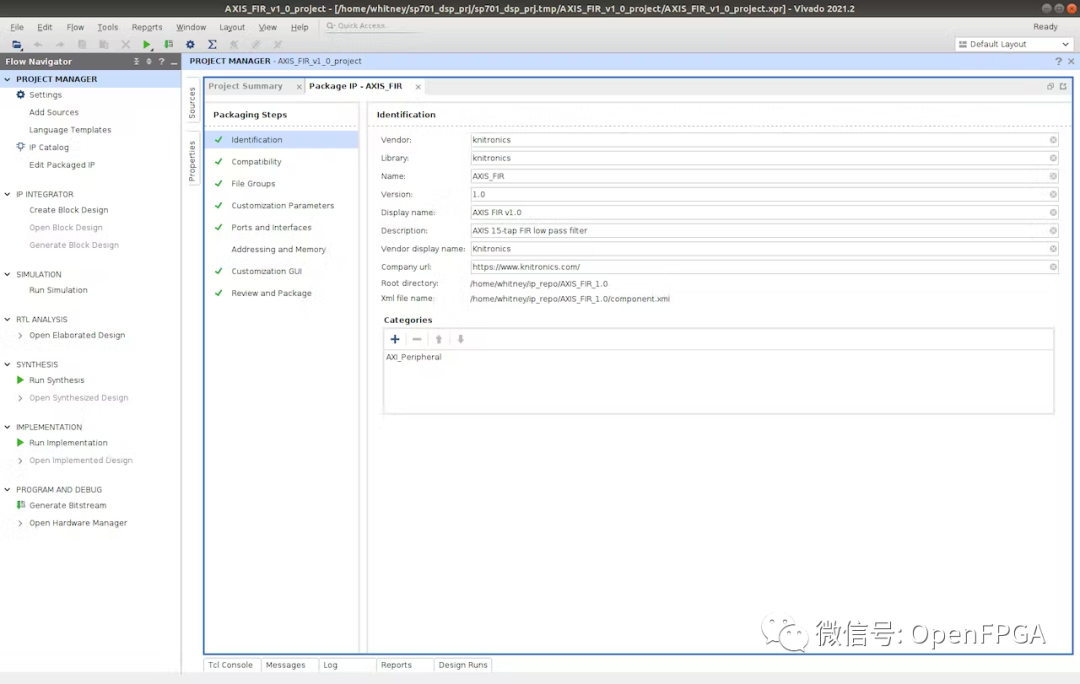

第一個選項卡中是輸出 AXI 外設 IP 包的基本顯示信息。

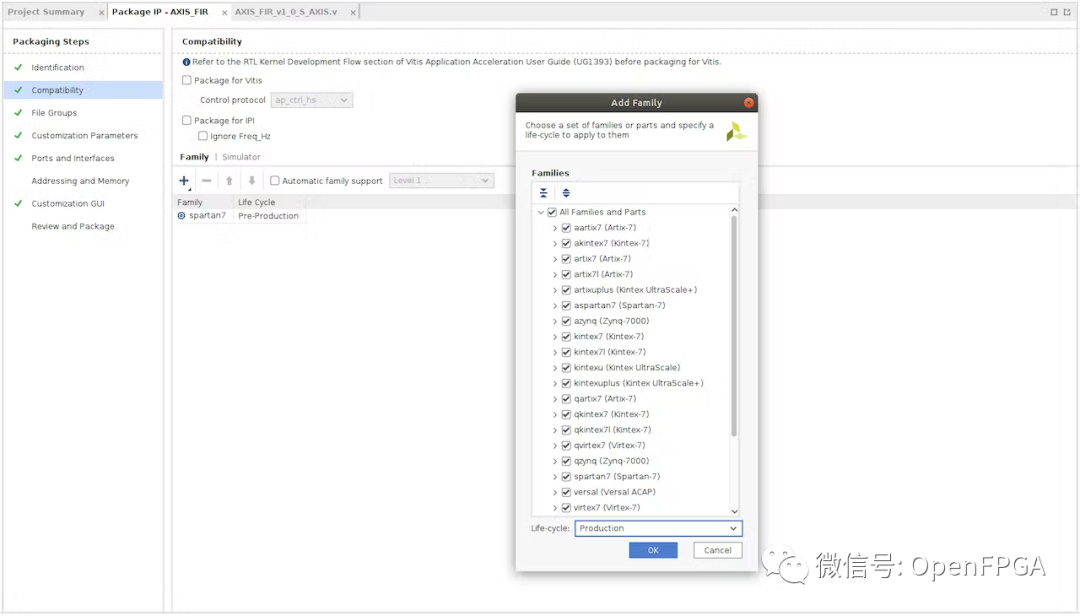

第二個標簽很重要。默認情況下,AXI 外設 IP 僅支持啟動 IP 包編輯器的主 Vivado 所針對的 FPGA 芯片系列。大多數時候,可能希望能夠將 AXI 外設 IP 塊與其他 Xilinx FPGA 芯片系列一起使用,就需要添加我們需要的目標FPGA芯片。

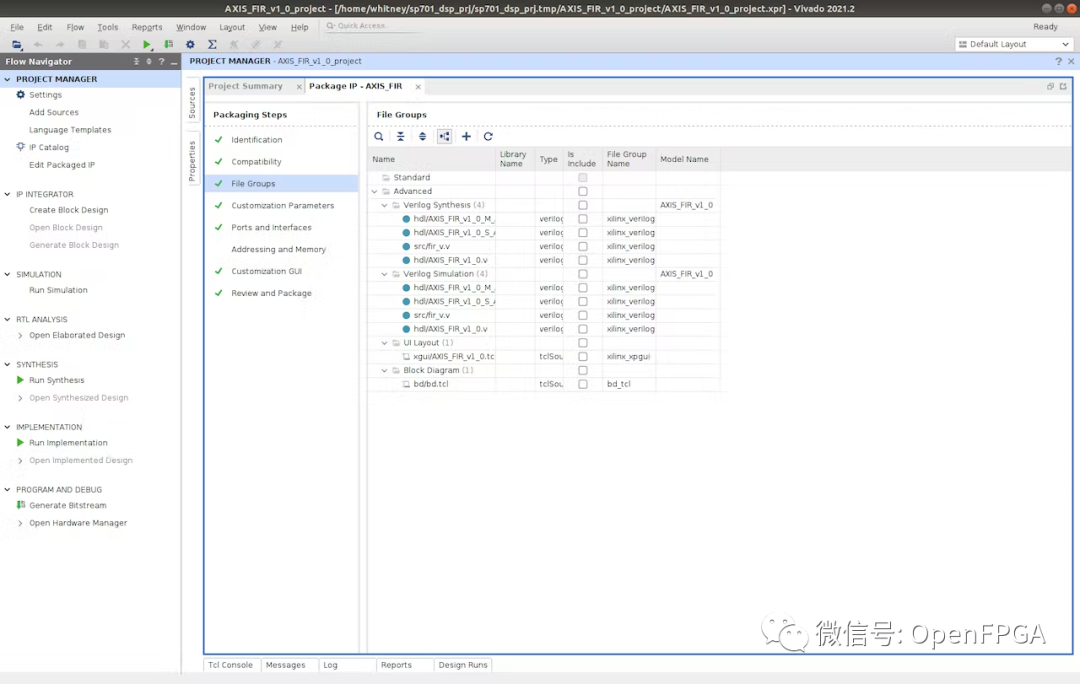

對于其余選項卡,默認需求即可。

在最后一個選項卡中,單擊窗口底部的Package IP按鈕。將出現一個提示,詢問是否要關閉 IP 編輯器 Vivado 項目。

此時,FIR AXI IP 塊被打包并放置在 Package IP 窗口的第一個選項卡指定的目錄中的存儲庫中。

將自定義 AXI4-Stream FIR 添加到項目

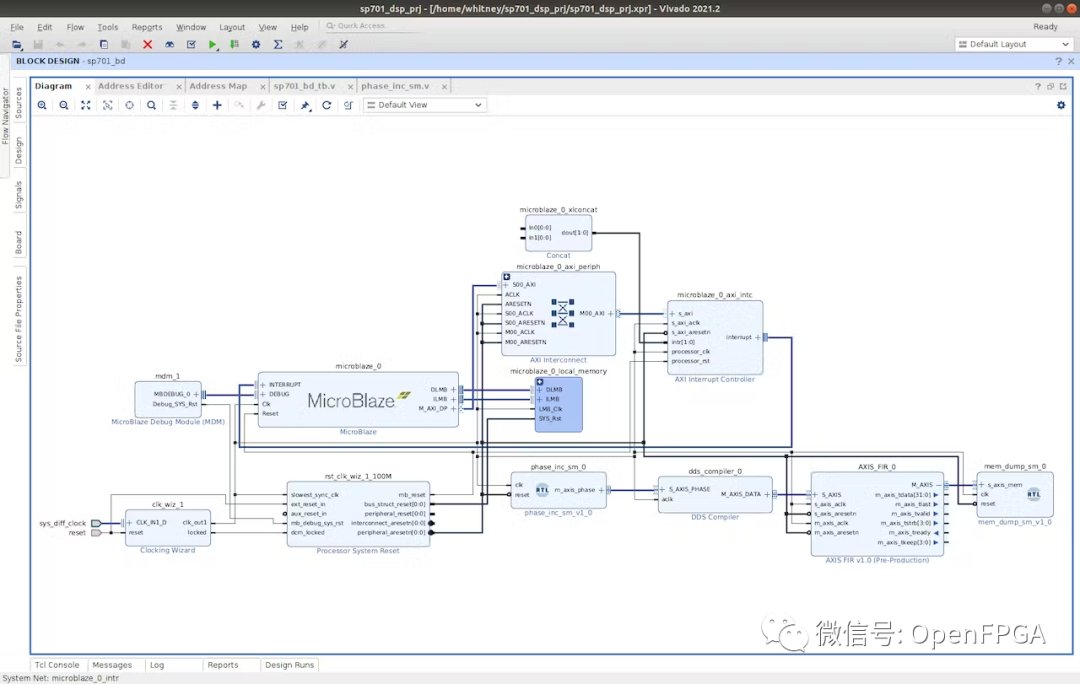

現在自定義 FIR AXI IP 模塊已經完成并封裝,我們可以返回原始 Vivado 項目,將其添加到模塊設計中。

我們的驗證項目如下:

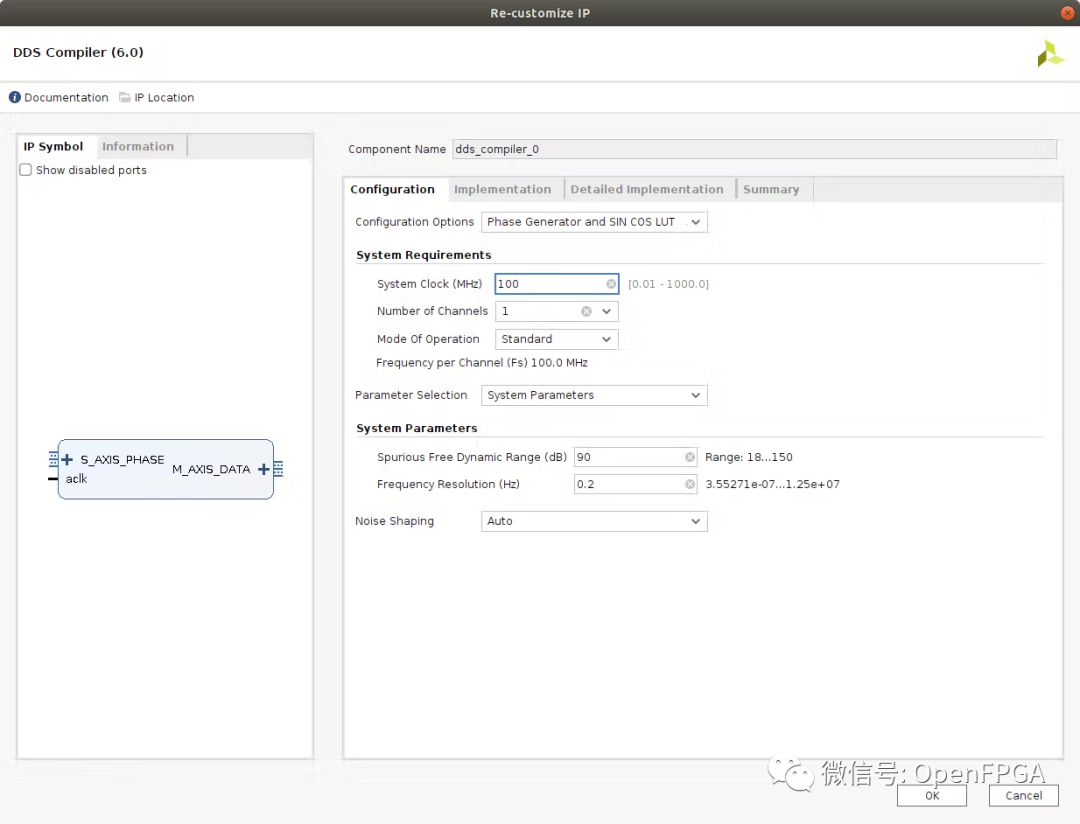

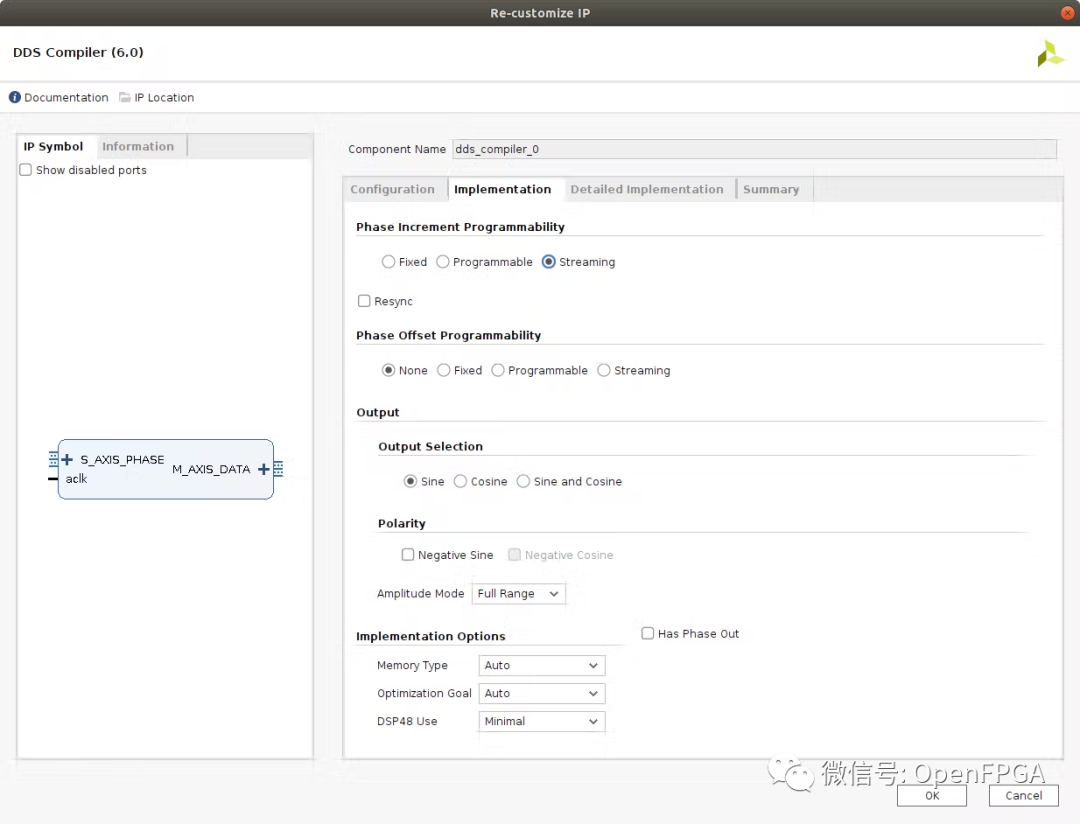

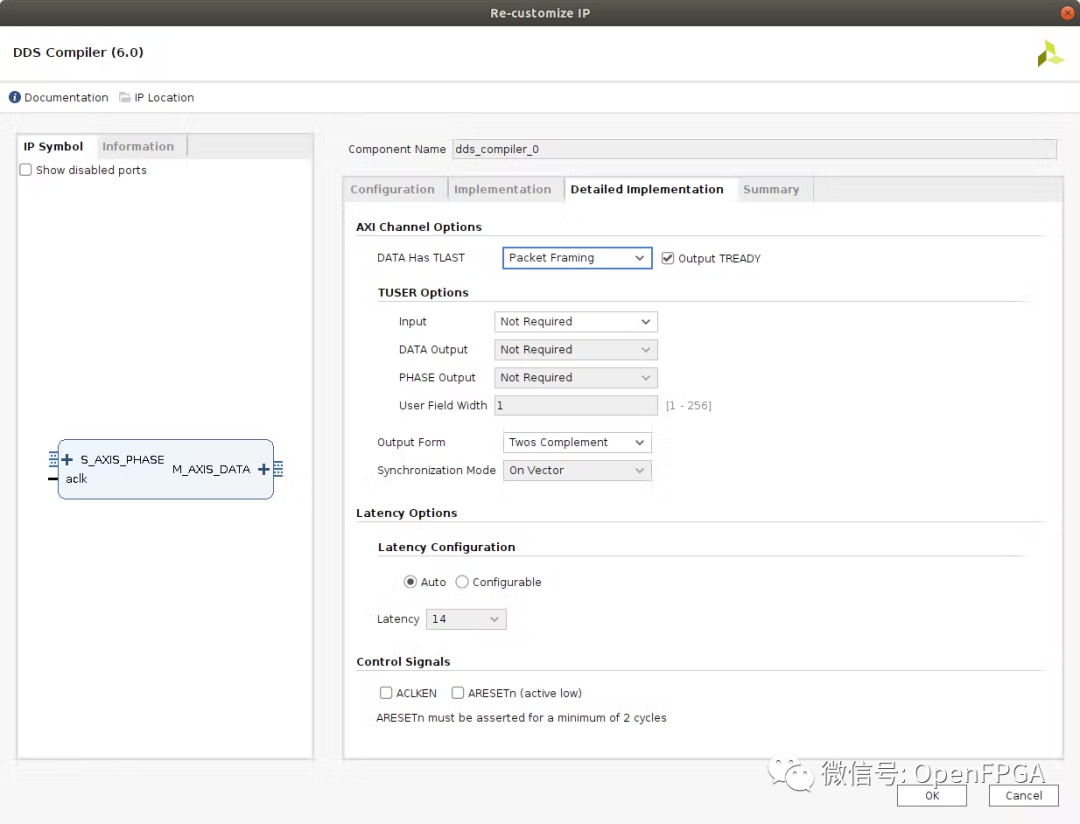

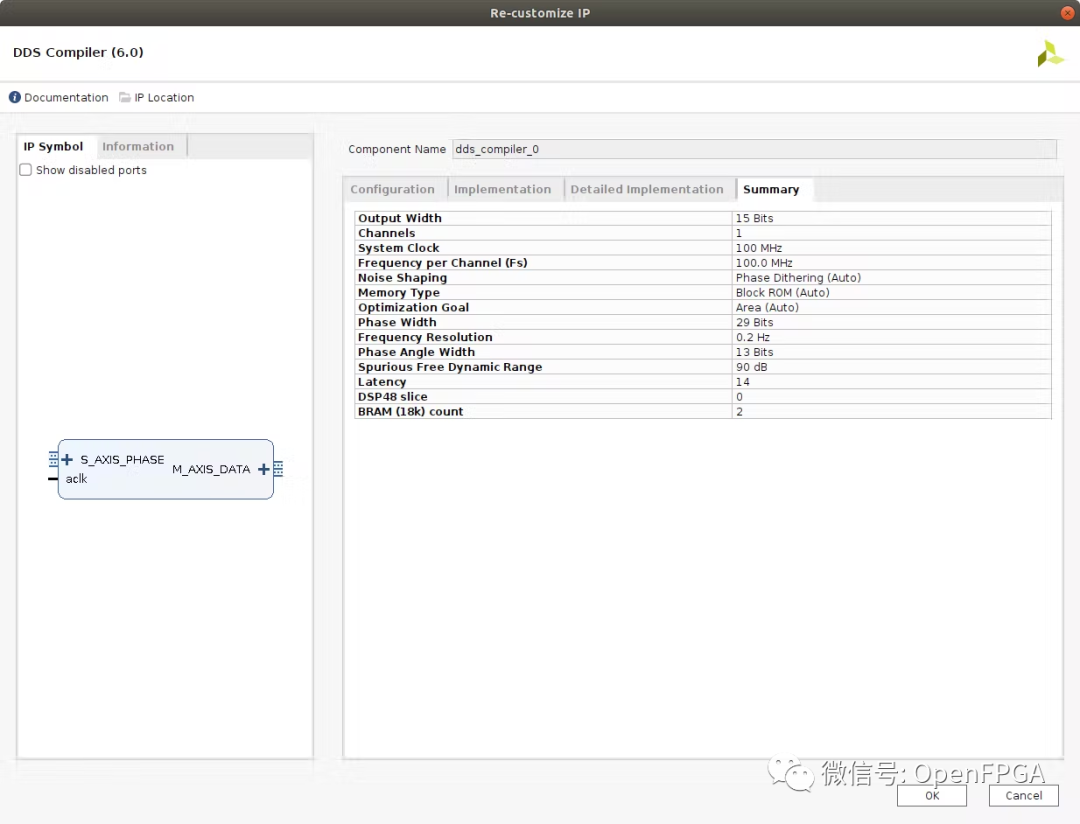

其中DDS IP設置如下:

創建仿真平臺

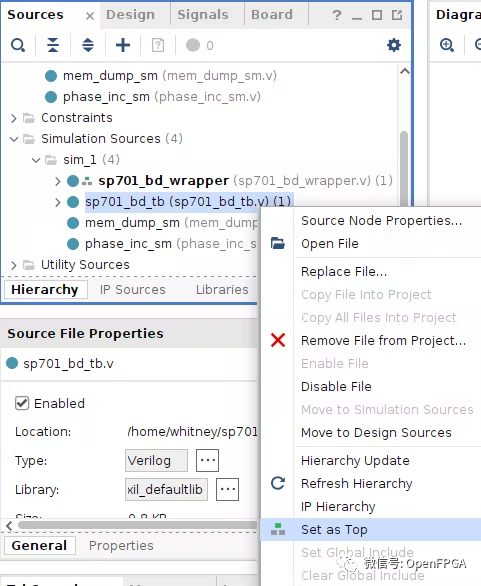

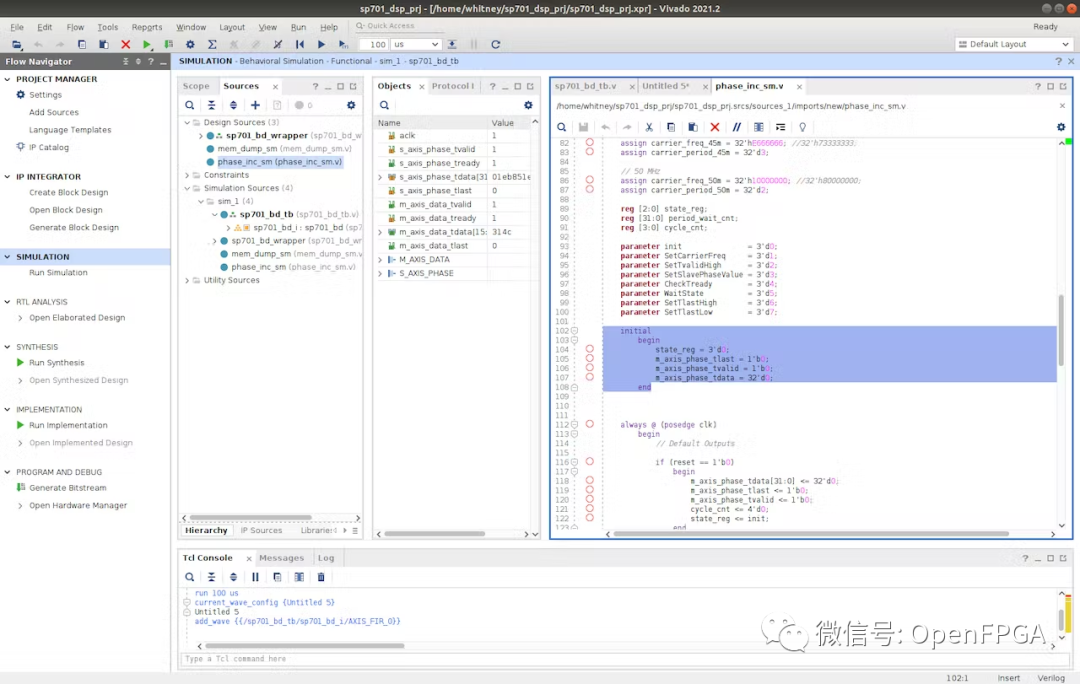

首先創建仿真文件,并在sim文件夾下的 Sources 選項卡中,右鍵單擊它并選擇Set as Top 。

在這種情況下,只需在塊設計中實例化塊設計,并為其提供差分系統時鐘和主 FPGA 復位。一旦接收到時鐘和復位信號,相位增量狀態機就會自行運行。

`timescale1ns/1ps

modulesp701_bd_tb;

regclk_p,clk_n,reset;

alwaysbegin

clk_p=1;clk_n=0;#5;

clk_p=0;clk_n=1;#5;

end

alwaysbegin

reset=1;#40;

reset=0;#1000000000;

end

sp701_bdsp701_bd_i(

.reset(reset),

.sys_diff_clock_clk_n(clk_p),

.sys_diff_clock_clk_p(clk_n)

);

endmodule

這里注意一下主 AXI 接口輸出信號和 tlast、tvalid 和 tdata 需要進行初始化。否則仿真將會報錯。

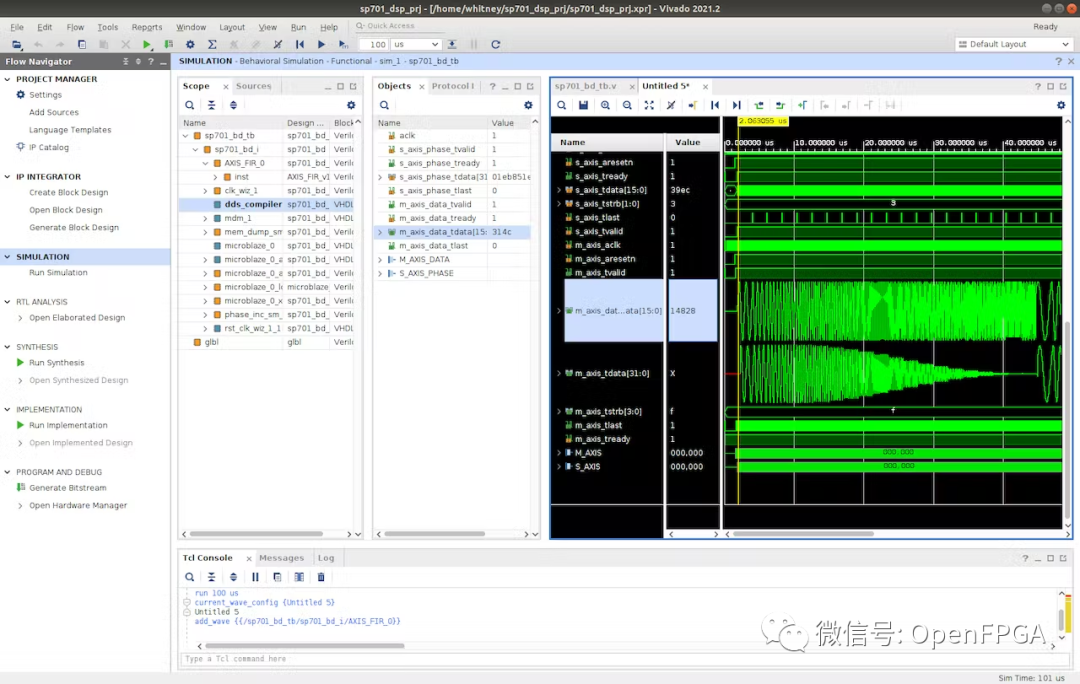

單擊Flow Navigator窗口中的Run Simulation并選擇Run Behavioral Simulation 。

注意仿真結果顯示格式。

參考

https://www.hackster.io/

總結

上面的一些創建細節沒有全部展現,因為本身對于IP的創建不是我們的核心,我們只想說明使用目前這種BD設計可以達達簡化設計,尤其是目前Verilog的一些缺點。

最后說一下調試中的注意點,就是使用ILA查看AXI-Stream輸出時候,會造成FIR的時序與采樣混淆導致 FIR 不再工作,可能會查看不到任何波形,使用AXIS的專用調試IP即可,后續我們在說明這方面的知識。

示例工程

https://github.com/suisuisi/AXI4-Stream-FIR-filter

審核編輯 :李倩

-

濾波器

+關注

關注

161文章

7835瀏覽量

178285 -

自動化

+關注

關注

29文章

5588瀏覽量

79370 -

開源

+關注

關注

3文章

3363瀏覽量

42545

原文標題:?構建自定義 AXI4-Stream FIR 濾波器

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA實現FIR數字濾波器

FIR濾波器的工作原理和特點

如何區分IIR濾波器和FIR濾波器

iir濾波器和fir濾波器的優勢和特點

如何為ESP8266構建自定義盾牌?

基于matlab FPGA verilog的FIR濾波器設計

DSP教學實驗箱_DSP算法實驗_嵌入式教程:4-3 有限沖激響應濾波器(FIR)算法(CCS顯示)

TSMaster 自定義 LIN 調度表編程指導

Matlab生成fir濾波器抽頭系數

Vivado 使用Simulink設計FIR濾波器

鴻蒙ArkUI實例:【自定義組件】

Vivado經典案例:使用Simulink設計FIR濾波器

?構建自定義AXI4-Stream FIR濾波器

?構建自定義AXI4-Stream FIR濾波器

評論