導讀

本篇適用于有一定通信基礎的大俠,本篇使用的理論不僅僅是擴頻通信。為了便于學習,本章將會以實戰的方式,對整個工程的仿真。并對一些關鍵的仿真結果進行說明。各位大俠可依據自己的需要進行閱讀,參考學習。

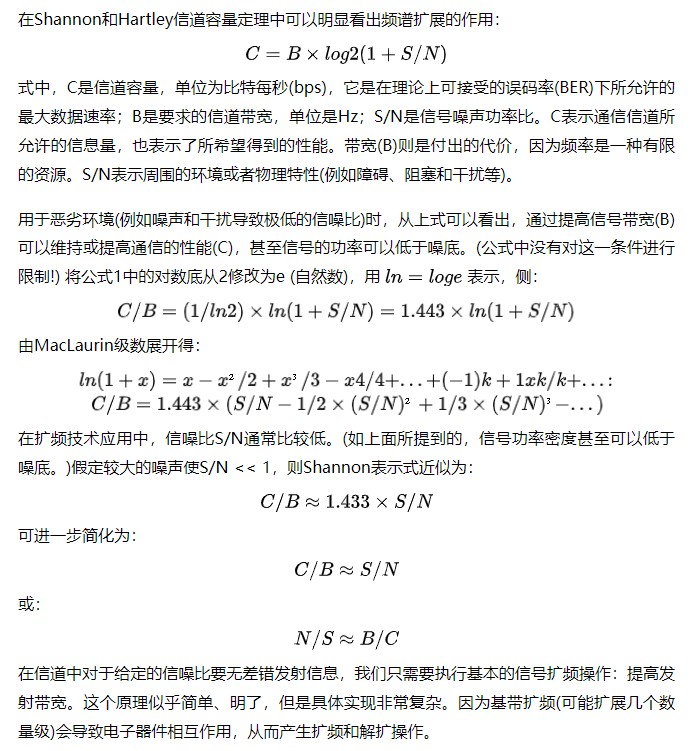

第三篇內容摘要:本篇會介紹系統的仿真設計。

仿真

一、模塊的建立及其仿真環境的生成

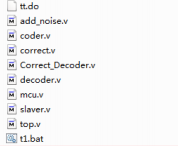

1.1、在計算機上,找一個沒有中文字符的目錄,新建以下幾個文件,如圖 6:

圖6 上圖為可以建立的文件,sim_wave.do 是仿真波形保存文件.tt.do。 其代碼如下:

#建立 library 名為”work” vlib work vmap work work #編譯當前目錄(./)中的 top.v、mcu.v …. vlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./top.v vlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./mcu.v vlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./slaver.v vlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./coder.v vlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./add_noise.v vlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./decoder.v vlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./correct.v vlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./Correct_Decoder.v #仿真 work 中的 top 模型 vsim -novopt work.top

以上是輸入方式進行仿真,也可以直接使用圖形化的方式進行仿真。但沒有開始仿真,因為我們以下還要添加一條語句。但沒有響應的文件。 tt.bat 的代碼如下:

echo

pause

vsim -do 。 t.do

pause

tt.bat 文件為批處理文件,僅為打開 modelsim、運行 tt.do 文件使用。也可以不使用該文件(以下不會詳細介紹)。

1.2、將對應的代碼寫到相應的文件中(sim_wave.do、tt.bat 文件可以不管)。

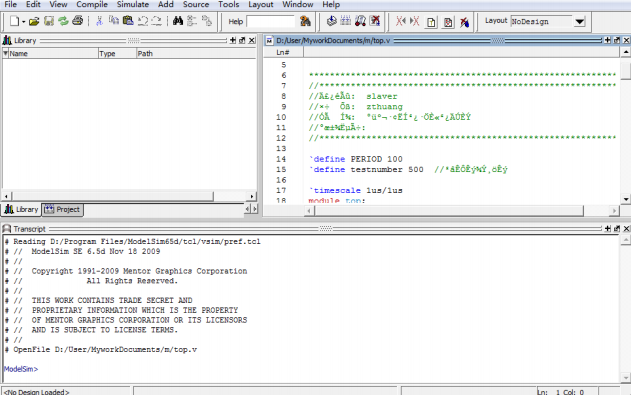

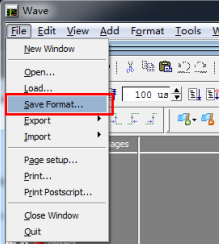

1.3、用 modelsim 的打開方式打開 top.v 文件(或者你先打開 modelsim,然后把目錄修改成以上所述的目錄也可)。運行的界面如圖 7(modelsim6.5d):

圖7 圖中的亂碼均為modelsim不兼容我所使用的notepad軟件編寫的中文字符,大俠均可不以理睬。

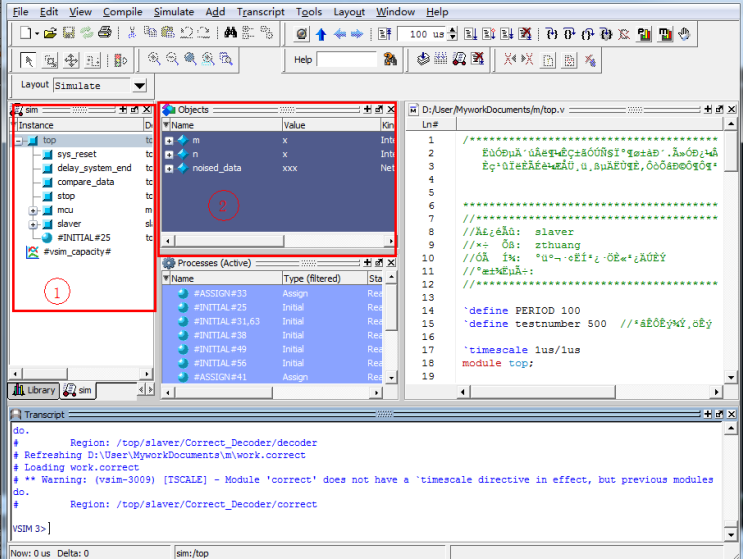

1.4、在 Transcript 中輸入”do tt.do”,運行當前目錄下的 tt.do 文件。 運行過程中,最后跳出如圖 8 的窗口。如果有錯誤,會在 Transcript 中用紅色字體說明(當然,這里都是英文)。

圖8 在框圖 1 中為整個仿真平臺上的模型,可以點擊模型+展開。框圖 2 顯示當前模型所含的項目。

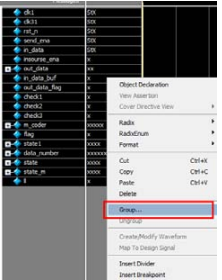

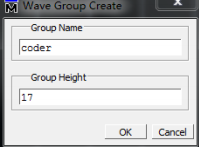

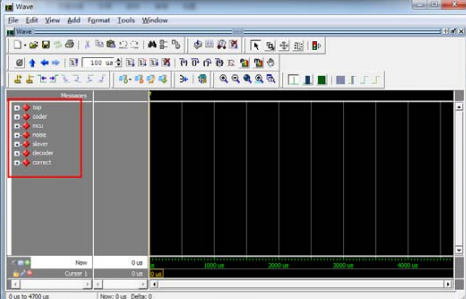

1.5、添加波形,如圖 9、10、11,對模塊 coder 添加波形,并對波形進行分組。

圖9

圖10

圖11 對所有仿真模型添加波形,并且分組,如圖 12。

圖12

圖13

1.6、仿真開始 在 Transcript 中輸入”run -all” 等待結果。以上將生成仿真環境的全過程。下面會將對各個模塊進行說明。

二、模塊仿真

2.1、模塊 mcu仿真

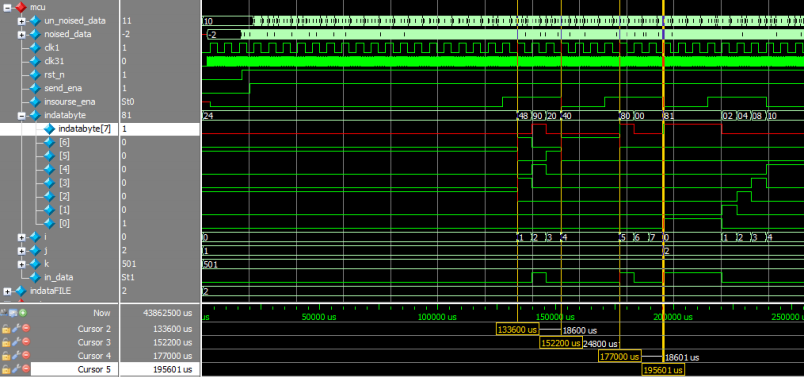

mcu 扮演一個信源產生模塊,其波形如圖 14。

圖14

在 send_ena 使能的情況下,當 insourse_ena 為高時,數據從 indatabyte 第 7 位端口輸出到 coder 模塊,圖中發送十六進制 24 的過程,僅在 insourse_ena 為高時發送。該模塊還產生兩個時鐘,兩個時鐘分別是 31 倍的頻率。clk1 和 clk31。

2.2、模塊coder仿真

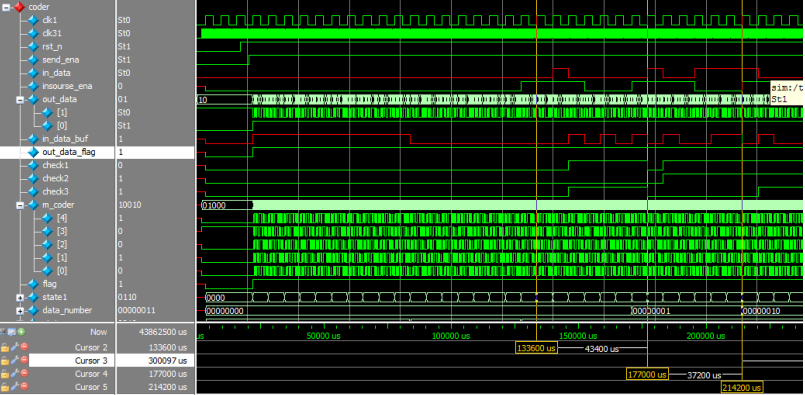

模塊 coder 將對 mcu 傳送的數據進行編碼、擴頻。仿真波形如圖 15。

圖15 圖中的 in_data_buf 為發送碼,當接收到 send_ena 后,先發送頭和數據幀,然后才發送數據如圖中從 133600us 開始發送數據”0010”(十六進制 2)后發送監督碼的”101”,在 177000us 開始發送數據”0100”(十六進制 4)后發送監督碼”110”。所有數據經過信道編碼后,out_data 發送出去。

2.3、模塊noise仿真

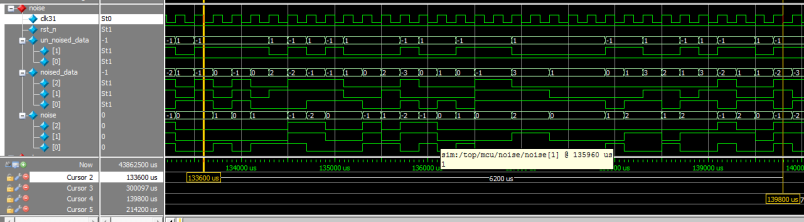

添加干擾,經 coder 發送的 2bit 數據擴展到 3bit 數據,并與噪聲進行加性。

仿真波形如圖 16。

圖16 圖中是對 1bit 數據進行擴頻后,其中 un_noised_data 為輸入數據(無噪聲)、經過與 noise 數據相加,得到數據 noised_data。 這模塊就是充當信道中的加性干擾源。

2.4、模塊decoder仿真

解擴是本系統的設計重點。它包含同步頭的同步和數據的接收等。

本設計采用一個循環偽隨機作為解擴碼。采用一個 31bit 的寄存器,初始化為級數為 5 的 m 序列,首尾循環。那么,在寄存器每一位上采數,都可以得到一個偽隨機序列。分別得出 31 個 m 序列。而且靠近的寄存器位,采集的 m 序列只有一位的移位。因此,可以采用該方法,在發送端發送的數據,不管為何時發送,在 31bit個寄存器中的 1 個寄存器中與之對應。更通俗的說法,不管發送設備何時開始發送。都可以在 31bit 的寄存器中找到一個寄存器采到的 m 序列與之對應。

由于在 31 比特的寄存器同時采數是比較耗費 FPGA 內部資源,所以本設計采用寄存器的每 10 個 bit 位進行一一處理。如果前 10 個沒能找到對應的 m 序列,則累加到后 10 個,以此類推,在 3 次的累加中,總能完全掃描完 31bit 位的寄存器。此時可以找到對應的比特位。

由于發送設備的數據頭為 10 個”1”和 1 個”0”,而在 10 個”1”中的 1 是延伸的,沒法直接得到相鄰”1”的交界,而在得到合適的 m 序列位后,必須進行同步,同步的方法為采集最后一個”0”作為同步。

在接收完成數據頭后,進行數據幀同步。數據幀是 4bit 數據”0000”和 3bit 監督位”000”。

接收完成數據幀之后才是數據的開始。由于數據比較大,累加基數這里是 100,閥值為 30,那么,當接收到 130,說明接收到一個”1”。

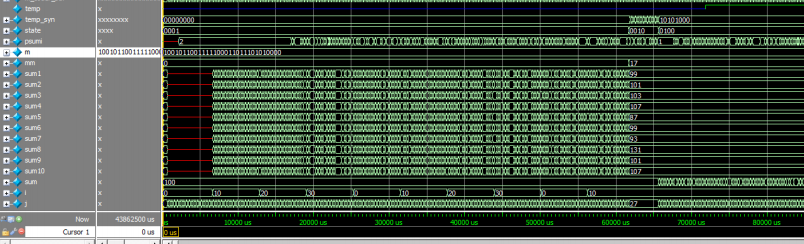

仿真結果如下:

圖17

圖17 為接收的整體工作狀態,sum1~sum10 分別采集 10 個寄存器比特位,當有1 個接收超過 130,說明寄存器該為上的 m 序列可以接收到 1 個”1”,sum 是對數據幀和數據的解擴統計。

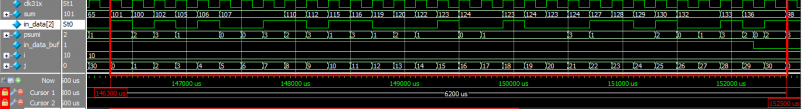

圖18

圖18 是一個完整數據解擴的過程,clk31 是采集時鐘,數據為 in_data_buf,從輸入到輸出,延遲一段時間后傳送到解擴模塊。psumi 為解擴的值,通過累加得到sum(in_data[2]判斷。為 1,則加;為 0,則減)。如果 sum 超過 130,說明發送數據為”1”,否則為”0”。(以上為數據”1”的例子)

通過解擴的數據,送到 correct 模塊進行糾錯。

2.5、模塊correct仿真

模塊 correct 為糾錯模塊。它將解擴后的數據進行分析,即對漢明碼的反運算。該模塊的仿真過程省略。

2.6、模塊Slaver仿真

Slaver 是接收模塊端,它將解擴、糾錯后的數據進行存儲。仿真過程省略。

2.7、模塊Top仿真

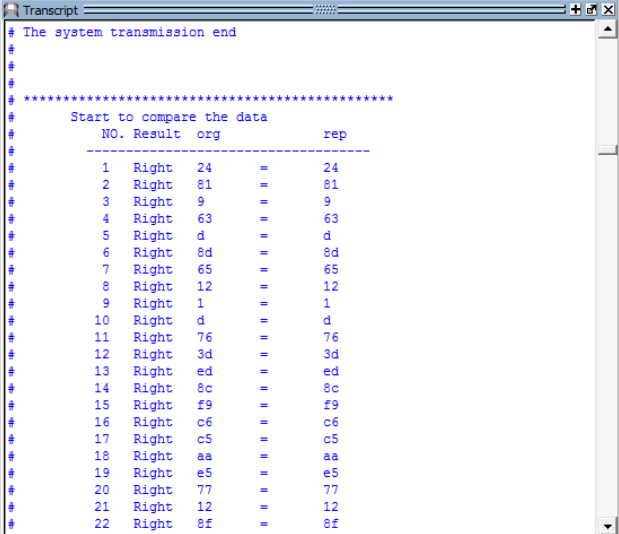

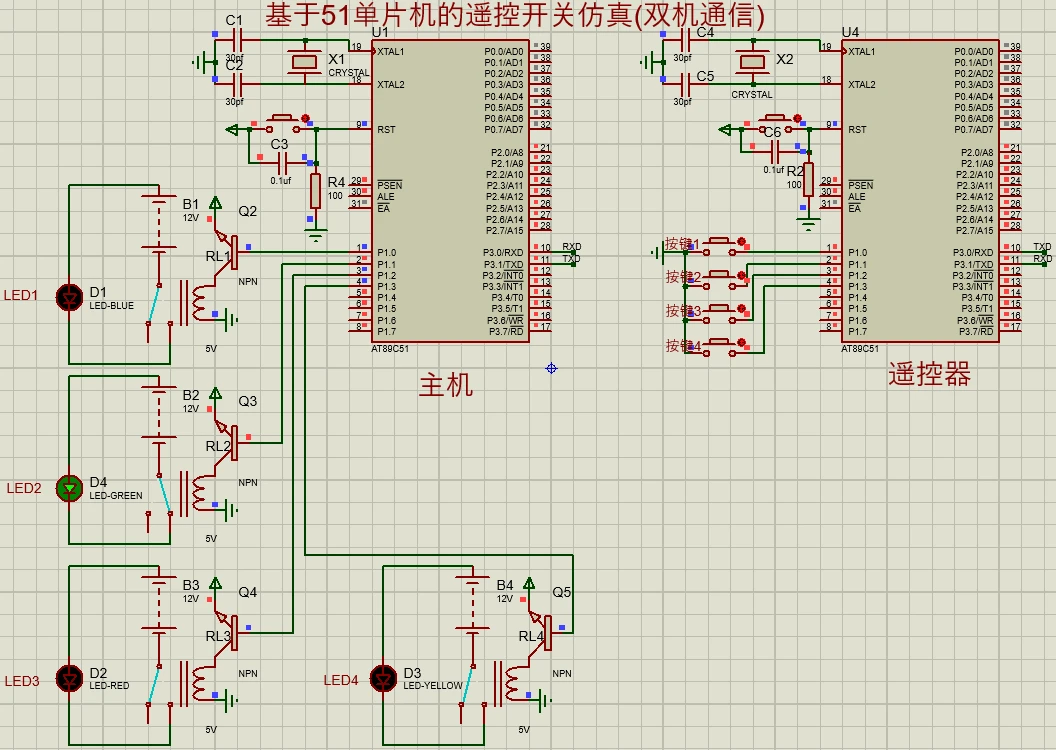

Top 模塊應該放第一塊講解,因為它是一個仿真平臺,它的子模塊包括 mcu 和slaver。它將兩個模塊的發送接收進行統計、并且進行計算、輸出,并對模塊參數設置。以下設置發送數據比特位為 500 的輸出結果(圖 19、圖 20):

圖19

圖20 以上是整個設計的仿真過程。

審核編輯:郭婷

-

仿真

+關注

關注

50文章

4070瀏覽量

133552 -

通信系統

+關注

關注

6文章

1187瀏覽量

53328

原文標題:基于FPGA的直接擴頻通信系統設計(附代碼)

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Ra-09-DTU入門教程,標準LoRaWAN協議對接國外TTN LoRaWAN開源服務器

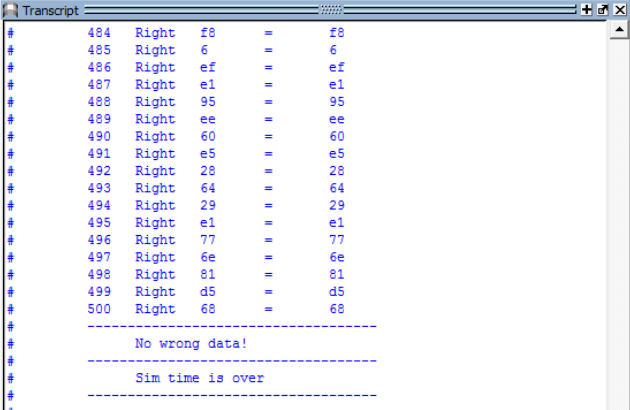

基于51單片機的遙控開關仿真(雙機通信)

基于MATLAB的通信系統設計

安信可 LoRa 系列模塊Ra-01H,可用于自動抄表,安防系統,遠程灌溉系統等

安信可LoRa模組Ra-01,超長距離擴頻通信,抗干擾性強

在用MATLAB仿真跳頻擴頻系統中,在發送端為什么用帶通濾波?

lora技術實現遠距離通信的原因有哪些?

大功率ATA-L50水聲功率放大器可用于水下通信測試系統

LoRa LLCC68模塊:工業級晶振+先進LoRa技術,實現穩定遠距離通信

直接擴頻通信系統的仿真設計

直接擴頻通信系統的仿真設計

評論