在SV中可以使用結構體作為模塊的輸入或輸出,這使得它可以更加清晰地傳遞更多的信號,以簡化RTL代碼,類似于interface。

typedef struct {

bit [7:0] intr = 'h AA;

logic [23:0] addr = 'h FF_FF_FF;

} ext;

module SU (

output ext extOut);

assign extOut = '{intr: 8'hFF, addr:24'haa_aa_aa};

initial begin

#1; $display($stime,,, "extOut = %p", extOut);

end

endmodule

module top;

ext extIn;

//connect extOut of 'SU' with extIn of 'top'

SU SUInst(.extOut(extIn));

initial begin

#2; $display($stime,,, "extIn = %p", extIn);

end

endmodule

仿真log:

1 extOut = '{intr:'hff, addr:'haaaaaa}

2 extIn = '{intr:'hff, addr:'haaaaaa}

V C S S i m u l a t i o n R e p o r t

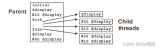

在上面的例子中,我們首先定義了一個名為“ext”的unpacked struct,然后直接作為module的output。

再聲明一個moudle top,連接到這個struct。最后打印表明這個結構體確實完成了連接,打印相同的信息。

struct可以作為參數傳遞給task或function,前提是這個struct需要先使用typedef聲明為用戶自定義類型

typedef struct {

logic [31:0] addr;

logic [63:0] data;

logic [3:0] BEnable;

} control;

function Dbus (input control ct1);

….

endfunction

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Module

+關注

關注

0文章

68瀏覽量

12851 -

SV

+關注

關注

0文章

6瀏覽量

13932 -

Struct

+關注

關注

0文章

31瀏覽量

10864

原文標題:SV Structure作為module的input/output

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Input Filter Design for Multiple-Module DC Power Systems

Input Filter Design for Multiple-Module DC Power Systems[/hide]

發表于 10-12 08:54

求助,FPGA,I/O口作input,輸入外部控制信號與作output有什么區別?

FPGA的I/O口如果作為input,輸入外部控制信號,電平還有其他設置等等,與作output時有什么區別?

發表于 06-21 12:50

使用SystemVerilog來簡化FPGA中接口的連接方式

解釋一句:文件格式都是.sv,這是因為SystemVerilog的語法都是包含Verilog的。 module top( input clk, input rst,

發表于 01-08 17:23

SV Structure作為module的input/output

a t i o n R e p o r t在上面的例子中,我們首先定義了一個名為“ext”的unpacked struct,然后直接作為module的output。再聲明一個moudle top,連接

發表于 11-10 15:30

Input and Output Capacitor Sel

ABSTRACTWhen designing with switching regulators, application requirements determine howmuch input

發表于 11-16 17:05

?36次下載

LTM8001: 36VIN, 5A μModule (Power Module) Regulator with 5-Output Configurable LDO Array Data Sheet

LTM8001: 36VIN, 5A μModule (Power Module) Regulator with 5-Output Configurable LDO Array Data Sheet

發表于 01-28 10:26

?1次下載

LTM4656/LTM4656-1: Synchronous Boost μModule Regulator with Input-Output Short Protection Data Sheet

LTM4656/LTM4656-1: Synchronous Boost μModule Regulator with Input-Output Short Protection Data Sheet

發表于 01-29 14:47

?1次下載

SystemVerilog中的Packed Structure

一個packed structure有很多的bits組成,這些bit在物理上連續存儲。packed structure只允許包含packed數據類型。

SV Structure作為module的input/output

在SV中可以使用結構體作為模塊的輸入或輸出,這使得它可以更加清晰地傳遞更多的信號,以簡化RTL代碼,類似于interface。

MAX14906: Quad-Channel Industrial Digital Output, Digital Input Data Sheet MAX14906: Quad-Channel Industrial Digital Output, Digital Input D

電子發燒友網為你提供ADI(ADI)MAX14906: Quad-Channel Industrial Digital Output, Digital Input Data Sheet相關產品參數

發表于 10-13 18:44

MAX22195: High-Speed, Octal, Industrial Digital Input with Parallel Output Data Sheet MAX22195: High-Speed, Octal, Industrial Digital Input

電子發燒友網為你提供ADI(ADI)MAX22195: High-Speed, Octal, Industrial Digital Input with Parallel Output Data

發表于 10-17 19:15

verilog中input和output作用

在Verilog中,input和output用于定義模塊的輸入和輸出端口。它們是用于通信的關鍵元素,定義了模塊與其它模塊之間的數據傳輸接口。通過input和output端口,模塊之間可

input和output的用法

輸入和輸出(input and output)是計算機科學中常用的術語,用于描述數據在計算機系統中的流動和交互。輸入是指將數據或命令送入計算機系統,輸出則是計算機系統對輸入數據進行處理后返回的結果

SV Structure作為module的input/output

SV Structure作為module的input/output

評論