查找表(Look-Up-Table)

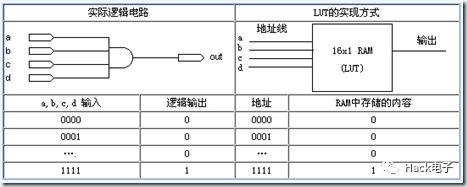

LUT就是查找表,對于4輸入的LUT而言,實際上就是4位地址位,一位數據位的存儲器,能夠存儲16位數據,所以我們在FPGA設計中可以用LUT組建分布式的RAM。

LUT的一個重要功能是邏輯函數發生器。本質上,邏輯函數發生器存儲的是真值表(Truth Table)的內容,而真值表則是通過布爾表達式獲得。在vivado中,打開網表文件,選擇相應的LUT,在property窗口中可以看到真值表。

如果用6輸入的LUT實現4輸入LUT的功能,那么就浪費了1-16/64=75%的資源,所以采用少輸入的LUT可以更好的節省面積和資源

因為當輸入數據的位數遠大于一個LUT的輸入時,就需要用多個LUT級聯來實現邏輯,那么級聯產生的延時也就不可避免了,這樣就會制約系統的運行頻率。那么為了避免級聯數過于多,就采用插入寄存器的方法來實現

通過LUT代替組合邏輯,而LUT中的值只和輸入有關,因此組合邏輯的功能由輸入決定,不在和復雜度有關;

CLB可配置邏輯快

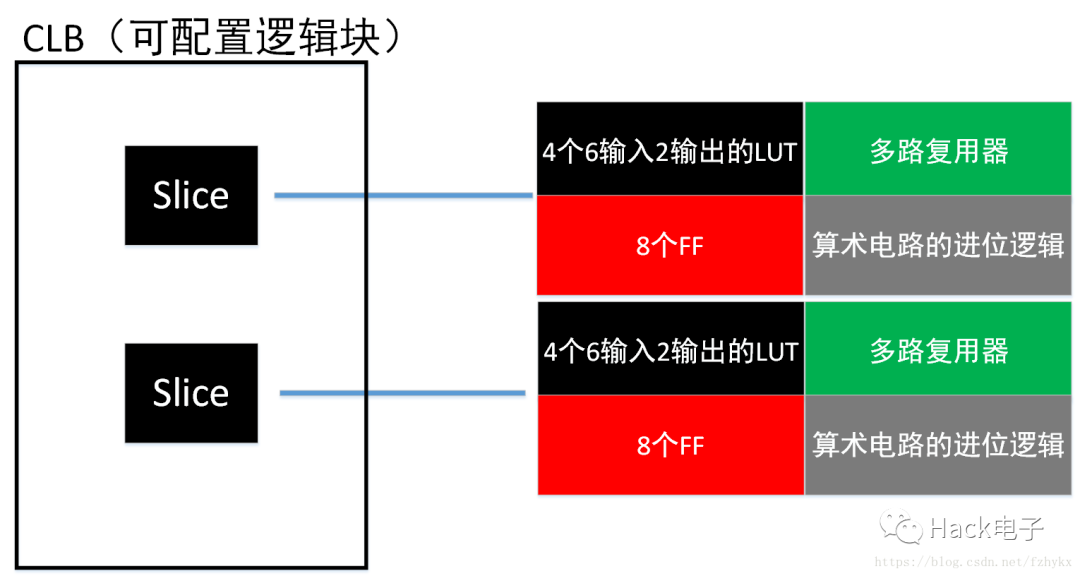

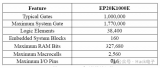

CLB是xilinx基本邏輯單元,每個CLB包含兩個slices,每個slices由4個(A,B,C,D)6輸入LUT和8個寄存器組成(中間應該還有一些選擇器、與非門、或非門之類的東西)。

”logic cells” 是 Xilinx 創造出來的一個市場用的刻度,可以用來衡量不同內部結構甚至不同廠商的資源情況。

LC邏輯單元

“logic cells”代表的是一個沒有其他任何功能的4輸入LUT,在老一些的Xilinx的FPGA中,他們使用LUT的數目乘以1.2來計算LC的數目,因為一個LUT中還有一個進位鏈和MUX。

在較新的FPGA中,Xilinx采用了6輸入LUT,這時他們采用系數1.6。

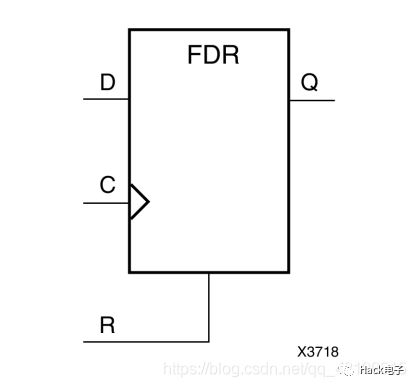

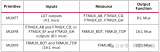

FDR : D Flip-Flop with Synchronous Rsest

同步清除D觸發器。FDR 擁有一個時鐘輸入接口,一個D觸發器數據接口,一個同步復位接口和一個觸發器輸出接口,當同步復位接口為高電平時,時鐘的上升沿觸發寄存器復位(置0);當同步時鐘接口為低電平時,時鐘的上升沿觸發寄存器裝載數據接口的數據。

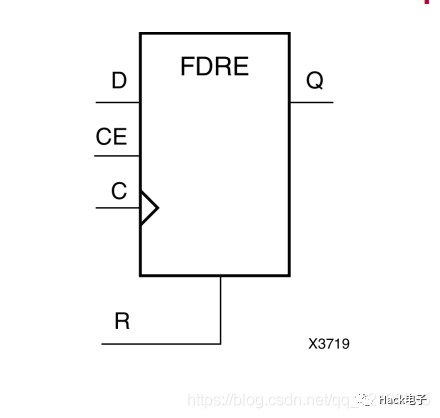

FDRE:D Flip-Flop with Clock Enable and Synchronous Reset 帶使能功能的同步清除D觸發器,相比與FDR多了一個使能接口,當同步復位接口為高電平時覆蓋所有其他輸出,時鐘的上升沿觸發寄存器復位(置0);當同步時鐘接口為低電平且使能接口為高電平時,時鐘的上升沿觸發寄存器裝載數據接口的數據。

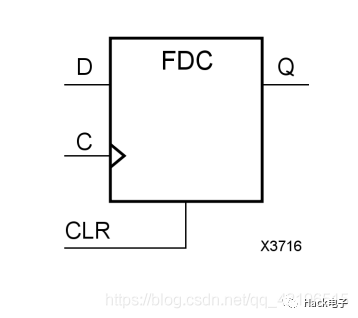

FDC :: D Flip-Flop with Asynchronous Clear 帶異步清除D觸發器 ,與 FDR的區別是。當CLR置為高電平時,不需要等到下一個時鐘的上升沿就可以復位寄存器。

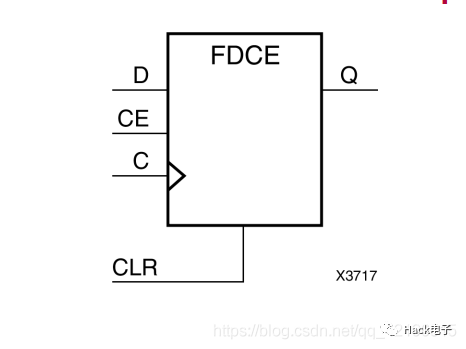

FDCE:D Flip-Flop with Clock Enable and AsynchronousReset 帶使能功能的異步清除D觸發器,相比與FDRE將同步復位變化成異步復位,當同步復位接口為高電平時,直接觸發寄存器復位(置0);當同步時鐘接口為低電平且使能接口為高電平時,時鐘的上升沿觸發寄存器裝載數據接口的數據。

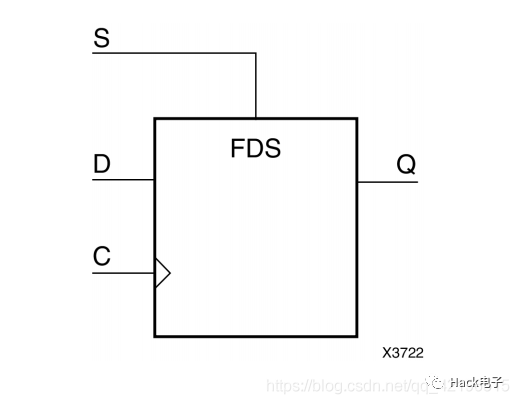

FDS:D Flip-Flop with Synchronous Set 帶同步置位的D觸發器 當置為端為低電平時,在時鐘的上升沿觸發數據保存在觸發器中,當置位端為低電平時,在一個時鐘的上升沿觸發導致觸發器清0

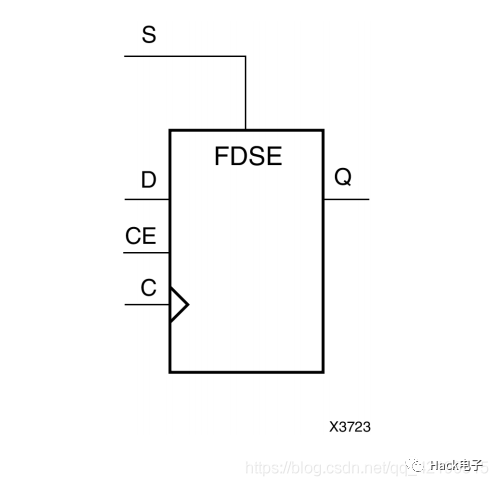

FDSE:D Flip-Flop with Clock Enable and Synchronous Set 帶時鐘使能和同步置位的D觸發器。當置位端為高電平是覆蓋所有輸出,一個時鐘的上升沿觸發導致寄存器置位,當置位端為低電平和時鐘使能位為高電平時,在一個時鐘的上升沿觸發導致寄存器裝載數據口的數據。

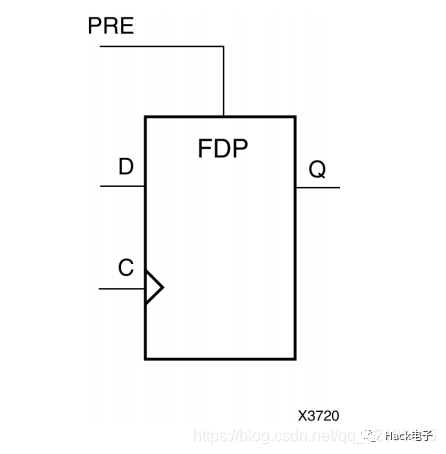

FDP:D Flip-Flop with Asynchronous Preset 帶有異步預置的D觸發器 相比FDS不需要等到時鐘的上升沿,即刻可進行置位。

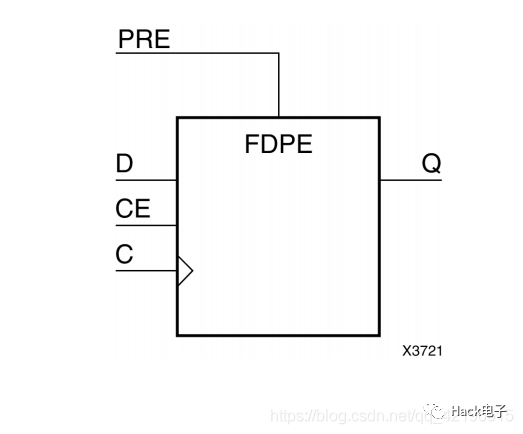

FDPE:D Flip-Flop with Clock Enable and Asynchronous Preset 帶有時鐘使能和異步置位的D觸發器 相比于FDSE不需要等到時鐘的上升沿,即刻可進行置位。

使用always塊綜合實現各種觸發器

module exp(

input clk,

input rst,

input A,

input B,

output reg Q,

output reg Q1,

output reg Q2,

output reg Q3

);

//or posedge rst

always @(posedge clk or posedge rst) begin //異步復位 綜合出FDCE

if(rst)

Q<=0;

else begin

Q<=A|B;

end

end

always @(posedge clk ) begin //同步復位 綜合出FDRE

if(rst)

Q1<=1;

else begin

Q1<=A|B;

end

end

always @(posedge clk or posedge rst) begin//異步置位 綜合出FDPE

if(rst)

Q2<=1;

else begin

Q2<=A|B;

end

end

always @(posedge clk) begin//同步置位 綜合出FDSE

if(rst)

Q3<=1;

else begin

Q3<=A|B;

end

end

endmodule

審核編輯 :李倩

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603010 -

存儲器

+關注

關注

38文章

7484瀏覽量

163765 -

觸發器

+關注

關注

14文章

2000瀏覽量

61132

原文標題:FPGA——LUT/FDRE/FDCE/FDSE/FDPE

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

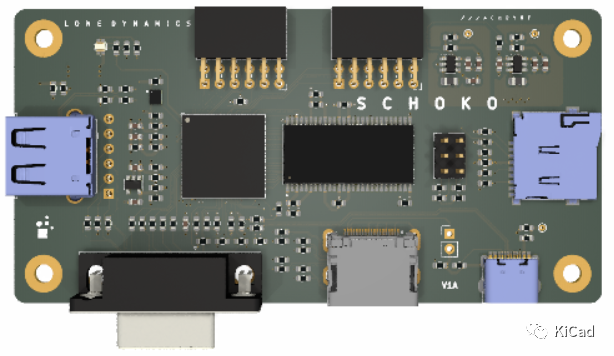

Made with KiCad(八):Schoko FPGA電腦板

松下推Lumix S9全幅無反相機,LUT功能成亮點

FPGA時序優化:降低MUXF映射的策略

FPGA——LUT/FDRE/FDCE/FDSE/FDPE

FPGA——LUT/FDRE/FDCE/FDSE/FDPE

評論