本文來源電子發(fā)燒友社區(qū),作者:yuzhiwen1986, 帖子地址:https://bbs.elecfans.com/jishu_2295853_1_1.html

高云FPGA 平臺(tái)介紹

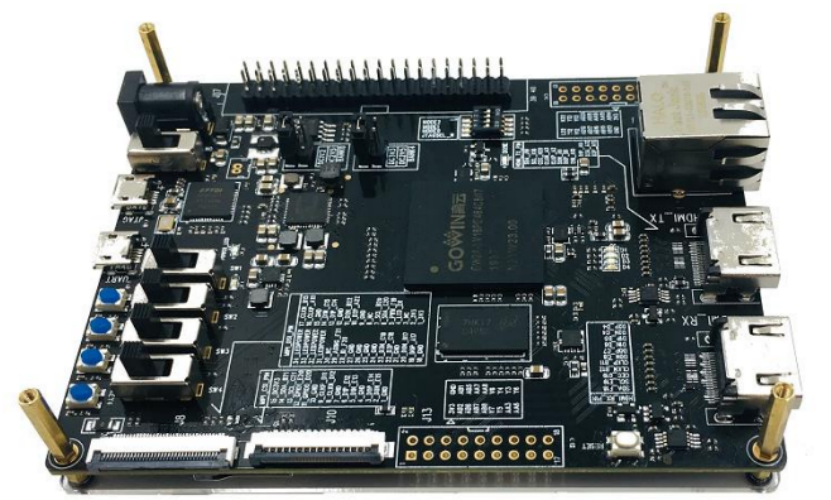

Combat開發(fā)套件是以高云半導(dǎo)體 GW2A 系列 FPGA 產(chǎn)品為核心,是高云半導(dǎo)體晨熙?家族第一代產(chǎn)品,內(nèi)部資源豐富,具有高性能的 DSP資源,高速LVDS 接口以及豐富的 BSRAM 存儲(chǔ)器資源,這些內(nèi)嵌的資源搭配精簡的FPGA 架構(gòu)以及 55nm 工藝使 GW2A 系列 FPGA 產(chǎn)品適用于高速低成本的應(yīng)用場合。

外設(shè)接口管腳說明

本次項(xiàng)目中用到的I/O口如表下描述

| 信號(hào)名 | FPGA管腳序號(hào) | BANK | 描述 | I/O電平 |

|---|---|---|---|---|

| SYS_CLK | M19 | 2 | 50Mhz有源晶振 | 3.3V |

| FPGA_RST | AB3 | 5 | 復(fù)位,低電平有效 | 3.3V |

| LED1 | U17 | 3 | LED指示燈1 | 1.5V |

| LED2 | U19 | 3 | LED指示燈2 | 1.5V |

| LED3 | U18 | 3 | LED指示燈3 | 1.5V |

| LED4 | T17 | 3 | LED指示燈4 | 1.5V |

| QSPI_DQ[0] | ||||

| QSPI_DQ[0] | ||||

| QSPI_DQ[0] | ||||

| QSPI_DQ[0] | ||||

| QSPI_CS | ||||

| QSPI_SCK | ||||

| MCU_TCK | C22 | 2 | ||

| MCU_TDI | F22 | 2 | ||

| MCU_TMS | J22 | 2 | ||

| MCU_RST | V14 | 4 | ||

| MCU_WAKE_UP | R18 | 3 | 按鍵3喚醒MCU | 1.5V |

| PMU_PADRST | T19 | 3 | 按鍵2復(fù)位PMU | 1.5V |

| PMU_PADRST |

時(shí)鐘復(fù)位電路

開發(fā)板為 FPGA 提供了一個(gè) 50MHz 有源晶振,連接到了全局時(shí)鐘引腳。

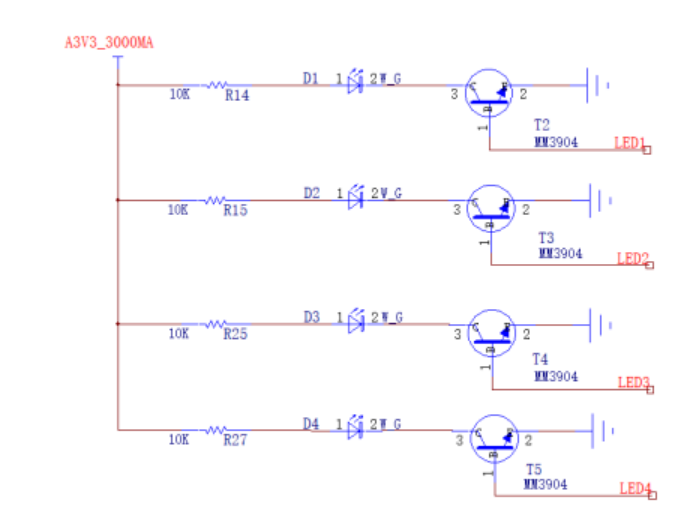

LED指示燈

開發(fā)板中有 4 個(gè)綠色 LED 燈,用戶可通過 LED 燈顯示所需狀態(tài)。可通過以下方式對(duì) LED 燈進(jìn)行測試:? 當(dāng) FPGA 對(duì)應(yīng)管腳輸出信號(hào)為邏輯高電平時(shí),LED 被點(diǎn)亮;當(dāng)輸出信號(hào)為低電平時(shí),LED 熄滅

MCU 喚醒電路

開發(fā)板有4個(gè)按鍵開關(guān),用戶可以通過手動(dòng)控制對(duì)應(yīng)FPGA管腳輸入低電平,觸發(fā)MCU喚醒。本項(xiàng)目中使用KEY2/3/4作為復(fù)位和喚醒電路,電路圖如下

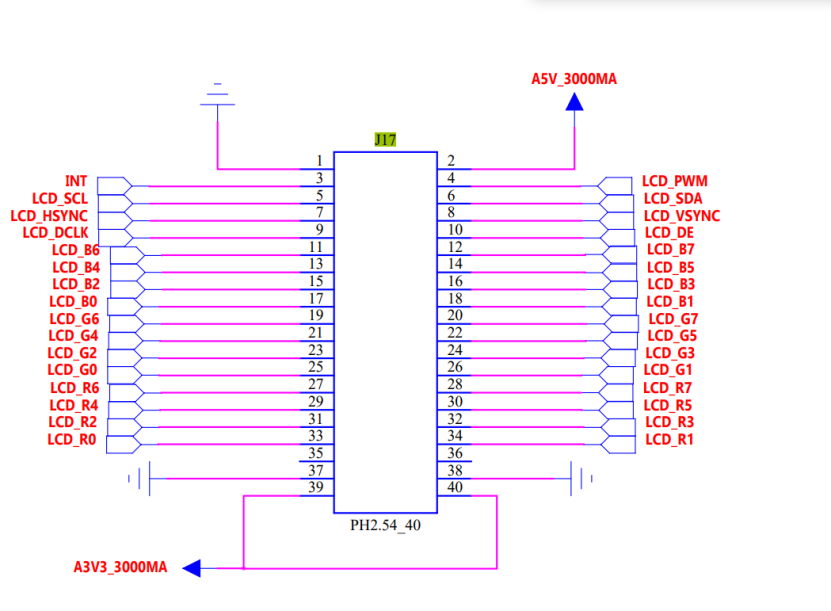

復(fù)用J17作為MCU的JTAG調(diào)試接口

LCD_PWM ->C22 -> MCU_TCK

LCD_SDA ->F22 ->MCU_TDI

LCD_VSYNC->G22 -> MCU_TDO

LCD_DE -> J22 ->MCU_TMS

LCD_B7 ->V14 -> MCU_RST

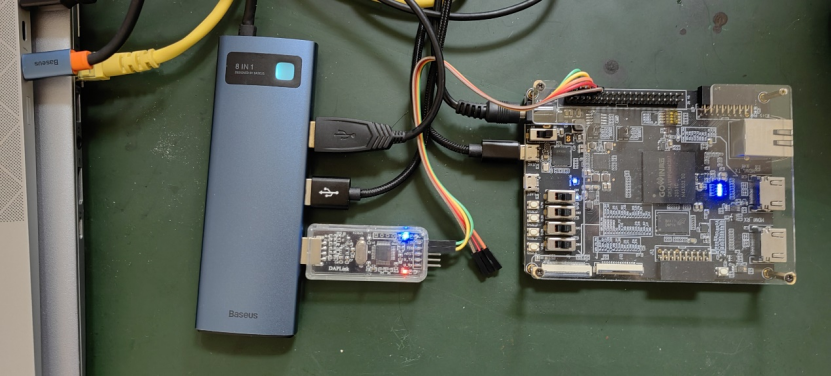

FPGA 原型平臺(tái)和MCU調(diào)試仿真器

FPGA 原型主要分為兩部分:FPGA 開發(fā)板,和調(diào)試器。接下來章節(jié)分別予以介紹。完整的 FPGA 開發(fā)板原型(包括 FPGA 開發(fā)板和MCU調(diào)試器)如下圖所示:

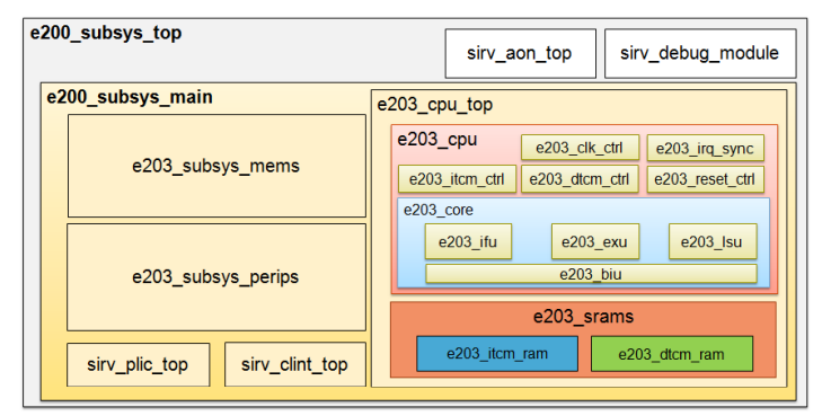

蜂鳥E203開源SoC

對(duì)于一個(gè)處理器核,還需要配套的 SoC 才能具備完整的功能。蜂鳥 E203 內(nèi)核不僅僅完全開源了 Core的實(shí)現(xiàn),還搭配完整的開源 SoC 平臺(tái),請(qǐng)參見《蜂鳥 E203 開源 SoC 簡介》了解更多 SoC 的介紹與信息。蜂鳥 E203 開源 SoC 的Subsys 模塊的款圖如下:

Linux平臺(tái)環(huán)境搭建

這里以Ubuntu系統(tǒng)為例進(jìn)行說明。

代碼下載和基本環(huán)境配置

- 下載E203源碼

git clone https://github.com/SI-RISCV/e200_opensource.git

- 下載iverilog源碼

`git clone https://github.com/steveicarus/iverilog.git

- 切換到v11分支(必須用V11或以上的版本)

git checkout v11-branch

- 安裝依賴

sudo apt-get install autoconf gperf flex bison build-essential

- 編譯、安裝iverilog和vvpsh autoconf.sh

./configure

make

make install

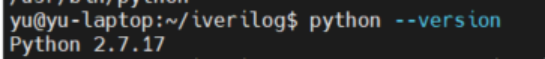

- 創(chuàng)建python軟鏈接

查看一下python的版本,我的還是Python2,新更新一下:

查看一下/usr/bin目錄下面有哪些版本,如果有python3版本就創(chuàng)建一個(gè)新的軟連接

sudo ln -s /usr/bin/python3.8 /usr/bin/python

其中/usr/bin/python3.8對(duì)應(yīng)你實(shí)際安裝的python版本。7. 安裝gtkwave

sudo apt-get install gtkwave

HBird-E-SDK 下載和配置1. 將 HBird-E-SDK 項(xiàng)目下載到本機(jī) Linux 環(huán)境中,使用如下命令:

git clone [https://github.com/SI-RISCV/hbird-e-sdk](https://github.com/SI-RISCV/hbird-e-sdk)

- 由于編譯軟件程序需要使用到GNU 工具鏈,假設(shè)使用完整的 riscv-tools 來自己編譯 GNU 工具鏈則費(fèi)

時(shí)費(fèi)力,因此本文檔推薦使用預(yù)先已經(jīng)編譯好的 GCC 工具鏈。我們已經(jīng)將工具鏈上傳至網(wǎng)盤,網(wǎng)盤具體地址記載于

hbird-e-sdk 項(xiàng)目(https://github.com/SI-RISCV/hbird-e-sdk)的 prebuilt_tools 目錄下的 README

中,用戶可以在網(wǎng)盤中的“RISC-V SoftwareTools/RISC-V_GCC_201801_Linux”目錄下載壓縮包gnu-mcu-eclipse-riscv-none-gcc-7.2.0-2-20180111-2230-centos64.tgz和gnu-mcu-eclipse-openocd-0.10.0-6-20180112-1448-centos64.tgz,然后按照如下步驟解壓使用(注意:上述鏈接網(wǎng)盤上的工具鏈可能會(huì)不斷更新,用戶請(qǐng)注意自行判斷使用最新日期的版本,下列步驟僅為特定版本的示例)。

cp gnu-mcu-eclipse-riscv-none-gcc-7.2.0-2-20180111-2230-centos64.tgz ~/

cp gnu-mcu-eclipse-openocd-0.10.0-6-20180112-1448-centos64.tgz ~/

//將兩個(gè)壓縮包均拷貝到用戶的根目錄下

cd ~/

tar -xzvf gnu-mcu-eclipse-riscv-none-gcc-7.2.0-2-20180111-2230-centos64.tgz

tar –xzvf gnu-mcu-eclipse-openocd-0.10.0-6-20180112-1448-centos64.tgz

// 進(jìn)入根目錄并解壓上述兩個(gè)壓縮包,解壓后可以看到一個(gè)生成的 gnu-mcu-eclipse 文件夾

cd ~/hbird-e-sdk // 進(jìn)入 hbird-e-sdk 目錄文件夾

mkdir ~p work/build/openocd/prefix

// 在 hbird-e-sdk 目錄下創(chuàng)建上述這個(gè) prefix 目錄 cd work/build/openocd/prefix // 進(jìn)入到 prefix 該目錄

ln –s ~/gnu-mcu-eclipse/openocd/0.10.0-6-20180112-1448/bin bin

// 將用戶根目錄下解壓的

OpenOCD 目錄下的 bin 目錄作為軟鏈接鏈接到該

prefix 目錄下

cd ~/hbird-e-sdk // 進(jìn)入 hbird-e-sdk 目錄文件夾

mkdir -p work/build/riscv-gnu-toolchain/riscv32-unknown-elf/prefix/

// 在 hbird-e-sdk 目錄下創(chuàng)建上述這個(gè) prefix 目錄

cd work/build/riscv-gnu-toolchain/riscv32-unknown-elf/prefix

// 進(jìn)入到 prefix 該目錄

ln -s ~/gnu-mcu-eclipse/riscv-none-gcc/7.2.0-2-20180111-2230/bin bin

// 將用戶根目錄下解壓的 GNU

Toolchain 目錄下的 bin 目錄作為軟鏈接鏈接到

// 該 prefix 目錄下 注意:此步驟完成工具鏈的安裝之后,后續(xù)開發(fā)程序示例無需重復(fù)執(zhí)行此步驟。

Verilog 仿真測試

使用E203 源代碼運(yùn)行基于 Verilog 的仿真測試程序,可以使用如下步驟進(jìn)行。

**步驟一:**準(zhǔn)備好自己的電腦環(huán)境,可以在公司的服務(wù)器環(huán)境中運(yùn)行,如果是個(gè)人用戶,推薦如下配置:

(1)本項(xiàng)目使用 Ubuntu 18操作系統(tǒng)

(2)由于 Linux 操作系統(tǒng)的版本眾多,推薦使用 Ubuntu 18.04 版本的 Linux 操作系統(tǒng)有關(guān)如何安裝 Ubuntu 操作系統(tǒng)本文不做介紹,有關(guān) Linux 的基本使用本文也不做介紹,請(qǐng)用戶自行查閱資料學(xué)習(xí)。

**步驟二:**將 e200_opensource 項(xiàng)目下載到本機(jī) Linux 環(huán)境中,使用如下命令:

git clone https://github.com/SI-RISCV/e200_opensource.git

**步驟三:**編譯 RTL 代碼,使用如下命令:

cd /vsim

// 進(jìn)入到 e200_opensource 目錄文件夾下面的 vsim 目錄。

make install CORE=e203

// 運(yùn)行該命令指明需要為 e203 進(jìn)行編譯,該命令會(huì)在 vsim 目錄下生成一個(gè) install

// 子文件夾,在其中放置所需的腳本,且將腳本中的關(guān)鍵字設(shè)置為 e203。

make compile

// 編譯 Core 和 SoC 的 RTL 代碼

// 注意:在此步驟之中,編譯 Verilog 代碼需要使用到仿真器工具,在 github 上的 Makefile

// 中使用的是免費(fèi)的 iverilog 工具,如果需要使用商業(yè) EDA 的用戶需要自行修改 Makefile 中的

// 對(duì)于免費(fèi)的 iverilog 工具如何安裝請(qǐng)用戶在互聯(lián)網(wǎng)上自行搜索。

步驟四:運(yùn)行默認(rèn)的一個(gè) testcase(測試用例),使用如下命令:

make run_test

注意:在此步驟中,運(yùn)行仿真需要使用仿真器工具,在 github 上的 Makefile 中此部分空缺,實(shí)際運(yùn)行的是”echo PASS”命令打印一個(gè)虛假的 PASS 到 log 文件中。用戶需要使用真正的仿真器運(yùn)行仿真得到真實(shí)的運(yùn)行結(jié)果。

注意:make run_test 將執(zhí)行 e200_opensource/riscv-tools/

riscv-tests/isa/generated 目錄中的一個(gè)默認(rèn) testcase,如果希望運(yùn)行所有的

回歸測試,請(qǐng)參見步驟五。

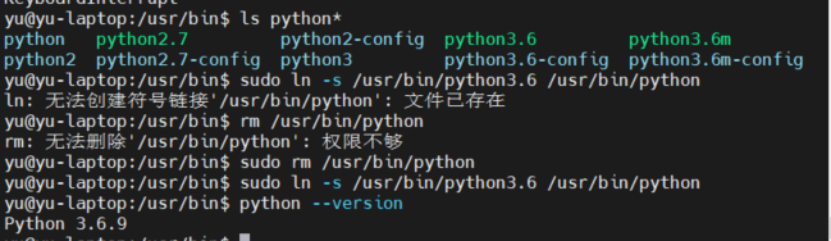

當(dāng)用make去編譯Makefile文件的時(shí)候,如果有出現(xiàn)/bin/sh:Syntax error: 的錯(cuò)誤時(shí)候,一般是當(dāng)前默認(rèn)的shell不正確的原因首先可以用命令ls -l /bin/sh 看看當(dāng)前默認(rèn)的是什么shell,Ubuntu一般默認(rèn)為bash再用要修改默認(rèn)的shell,可以采用命令sudo dpkg-reconfigure dash。會(huì)出現(xiàn)如下窗口,然后選擇否。

步驟五:運(yùn)行回歸(regression)測試集,使用如下命令:

make regress_run

注意:這使用 e200_opensource/ riscv-tools/riscv-tests/isa/generated 目錄中 testcases,逐個(gè)的運(yùn)行 testcase。

步驟六:查看回歸測試結(jié)果: make

regress_collect // 該命令將收集步驟五中運(yùn)行的測試集的結(jié)果,將打印若干行的結(jié)果,每一行對(duì)應(yīng)一個(gè)測 // 試用例,如果那個(gè)測試用例運(yùn)行通過,那一行則打印的 PASS,如果運(yùn)行失敗,那一行則 // 打印的 FAIL。如圖 所示

代碼編譯下載

工程導(dǎo)入

在Opensource

目錄下FPGA文件夾創(chuàng)建一個(gè)新的文件夾gowin,

將相關(guān)的rtl文件拷入,并對(duì)top文件進(jìn)行的對(duì)應(yīng)修改,文件目錄如下圖:

打開gowin軟件,創(chuàng)建工程,選擇好對(duì)應(yīng)的器件并導(dǎo)入文件。導(dǎo)入具體軟件操作說明參見SUG100-1.7_Gowin云源軟件用戶指南,本項(xiàng)目中導(dǎo)入之后界面如下:

程序編譯和下載

修改完程序之后保存點(diǎn)擊Process 點(diǎn)擊Place&Route編譯,編譯通過之后前面會(huì)出現(xiàn)綠

.編譯通過后雙擊Program Device彈出下載窗口,點(diǎn)擊開始下載

運(yùn)行和調(diào)試軟件

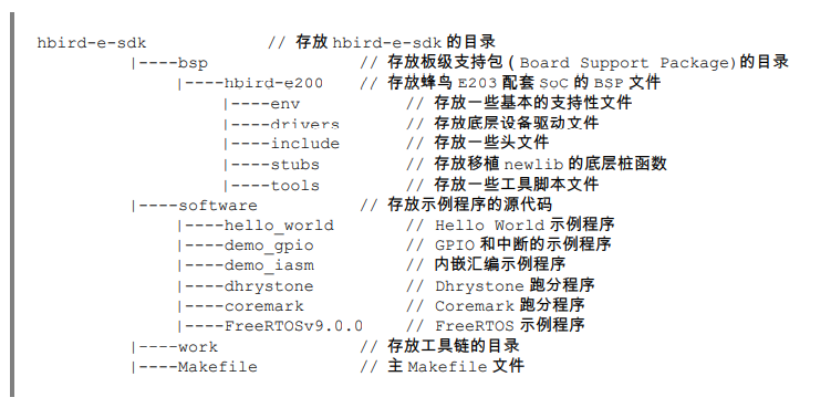

HBird-E-SDK介紹

HBird-E-SDK 并不是一個(gè)軟件,它本質(zhì)上是由一些 Makefile、板級(jí)支持包(Board Support Package,

BSP)、腳本和軟件示例組成的一套開發(fā)環(huán)境。HBird-E-SDK 基于 Linux 平臺(tái),使用標(biāo)準(zhǔn)的 RISC-V GNU

工具鏈對(duì)程序進(jìn)行編譯,使用 OpenOCD+GDB 將程序下載到硬件平臺(tái)中并進(jìn)行調(diào)試。

HBird-E-SDK 代碼結(jié)構(gòu)

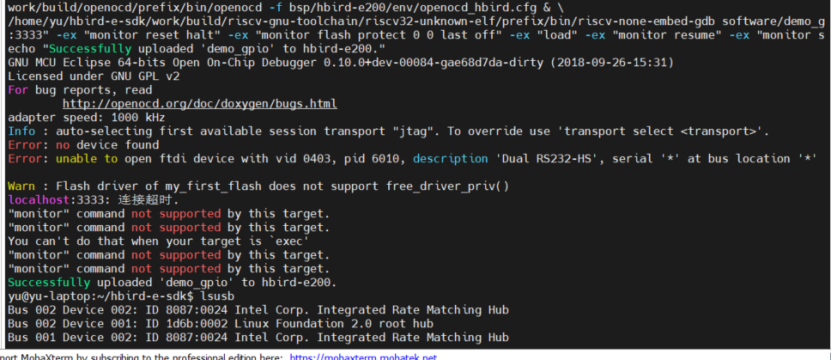

編譯 demo_gpio 示例程序,使用如下命令: cd // 進(jìn)入 hbird-e-sdk 目錄文件夾 make dasm PROGRAM=demo_gpio NANO_PFLOAT=0 //注意:由于 Demo_GPIO 程序的 printf 函數(shù)不需要輸出浮點(diǎn)數(shù),上述選項(xiàng) NANO_PFLOAT=0 指明 newlib-nano 的 printf 函數(shù)無需支持浮點(diǎn)數(shù),請(qǐng)參見《RISC-V 架構(gòu)與嵌入式開發(fā)快速入門》第 11 章了解相關(guān)信 息。

將編譯好的

demo_gpio 程序下載至 FPGA 原型開發(fā)板中,使用如下命令:

很遺憾,我這里因?yàn)槭褂玫南螺d器有問題,最終還是沒有成功下載MCU bin文件。

但是基本的流程走通了。時(shí)間有限試用期已經(jīng)結(jié)束了。期待下一次還會(huì)有繼續(xù)!

-

高云半導(dǎo)體

+關(guān)注

關(guān)注

20文章

127瀏覽量

50478 -

RISC-V

+關(guān)注

關(guān)注

45文章

2270瀏覽量

46130 -

E203

+關(guān)注

關(guān)注

0文章

8瀏覽量

122

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

《RISC-V能否復(fù)制Linux 的成功?》

精彩回顧 : 向新而行 云啟未來——2024高云FPGA線上技術(shù)研討會(huì)

2024高云FPGA線上技術(shù)研討會(huì)成功舉辦

JH-7110 RISC-V開發(fā)套件正式開源

國內(nèi)首家!德國萊茵TüV為高云半導(dǎo)體頒發(fā)產(chǎn)品認(rèn)證證書

高云半導(dǎo)體與香港理工大學(xué)共探FPGA技術(shù)在智能電網(wǎng)領(lǐng)域的應(yīng)用

回顧:高云半導(dǎo)體成功舉辦22nm產(chǎn)品及方案研討會(huì)

【高云半導(dǎo)體Combat開發(fā)套件試用體驗(yàn)】RISC-V處理器蜂鳥E203在高云FPGA平臺(tái)上的移植實(shí)踐

【高云半導(dǎo)體Combat開發(fā)套件試用體驗(yàn)】RISC-V處理器蜂鳥E203在高云FPGA平臺(tái)上的移植實(shí)踐

評(píng)論