本篇故事性可能沒那么強(qiáng)^^, 我們來講講低功耗。其實(shí)低功耗這個(gè)話題前面我寫文章講過,今天我們從芯片設(shè)計(jì)的全流程重新總結(jié)一下如何壓低芯片的功耗。

1 為什么要壓低芯片功耗

這事兒其實(shí)好理解,原因很多,比如電源網(wǎng)絡(luò)不好設(shè)計(jì),芯片容易失效等等。但是最重要的我認(rèn)為就兩點(diǎn)(敲黑板):

續(xù)航太短,散熱太大。

對(duì)于移動(dòng)設(shè)備,比如手機(jī),電池供電的,功耗太大會(huì)縮短續(xù)航,你肯定不樂意充電一整天,電話三分鐘。

那要是插電設(shè)備呢?你肯定不樂意用個(gè)核顯還非要上個(gè)水冷。所以綜上所述,功耗要盡量做小就是了。

2 集成電路的功耗來源

既然要優(yōu)化功耗,我們先看看功耗是怎么造成的。現(xiàn)代大規(guī)模集成電路里面廣泛用的是CMOS, Complementary Mosfet, 互補(bǔ)的晶體管。原理上上下兩個(gè)晶體管不同時(shí)導(dǎo)通,應(yīng)該沒有功耗,妥妥的永動(dòng)機(jī)(狗頭)。但實(shí)際上有非理想因素在,功耗就是這么產(chǎn)生的。

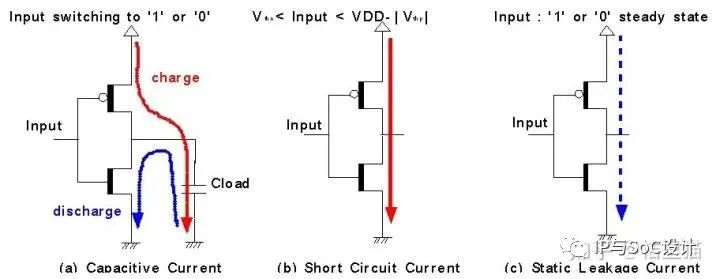

·電容充放電電流。看圖a, 實(shí)際上晶體管與地之間是有點(diǎn)容的。所以輸入從0到1變化的時(shí)候會(huì)導(dǎo)致這個(gè)電容充放電。當(dāng)input為0的時(shí)候能量從VDD沖到了電容, input 為1的時(shí)候能量直接流到地。

·短路電流。由于晶體管非理想,存在某個(gè)電壓,NMOS和PMOS都導(dǎo)通,導(dǎo)致直接有VDD到VSS的通路。產(chǎn)生電流。

·漏電流。漏電流是input穩(wěn)定的時(shí)候,其實(shí)vdd和vss之間也有細(xì)微的電流流過產(chǎn)生功耗。

電容充放電和短路電流是動(dòng)態(tài)功耗,漏電流是靜態(tài)功耗。動(dòng)態(tài)功耗一般來講遠(yuǎn)大于靜態(tài)功耗。抓大放小,我們這個(gè)地方主要記住大頭充放電功耗怎么算的。

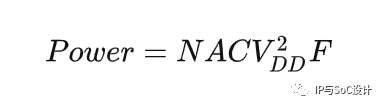

N是晶體管數(shù)量。

A是翻轉(zhuǎn)因子。

C是寄生電容。

V是電源電壓

F是頻率。

所以power和VDD二次方成正比,和頻率一次方成正比。主要降低功耗也就是圍繞這幾個(gè)因子來轉(zhuǎn)。

為了后面看著方便,這五個(gè)變量,代表了什么,再復(fù)習(xí)一遍。

3 功耗優(yōu)化全流程

此處我們給出一個(gè)功耗優(yōu)化全流程中各個(gè)時(shí)間點(diǎn)需要注意的功耗優(yōu)化方法。圖似乎有點(diǎn)小。看詳細(xì)說明。

需要注意兩點(diǎn):

1.下圖列的并不是全部的低功耗手段,只是一些我們?nèi)菀赘深A(yù)的低功耗手段,比如在第四步流片制造中代工廠顯然可以優(yōu)化工藝,降低漏電流,不過對(duì)芯片設(shè)計(jì)來講這已經(jīng)屬于環(huán)境因素了。

2.下圖只列了芯片功耗的優(yōu)化,在5步驟封裝測(cè)試中還有板級(jí)功耗的優(yōu)化,不在芯片設(shè)計(jì)討論范圍內(nèi)。

3.1 概念計(jì)劃階段

降低N:限制規(guī)格。概念計(jì)劃階段優(yōu)化功耗的手段雖然不多,但是效果其實(shí)是最明顯的。盛傳一句話,上面一張嘴,下面跑斷腿。概念計(jì)劃就處于這么一個(gè)上面的位置。后面操作只能說是功耗優(yōu)化,概念階段確定的規(guī)格可以直接框定功耗的大致范圍。此處團(tuán)隊(duì)需要深入了解市場(chǎng),確定什么功能要解決市場(chǎng)的痛點(diǎn),必須做進(jìn)去,什么東西是個(gè)偽需求,不要做進(jìn)芯片徒增功耗。比如人臉識(shí)別的芯片你非要加入一個(gè)GPS導(dǎo)航,這功耗不就上去了。再比如給筆記本的芯片,你強(qiáng)行造出一個(gè)臺(tái)式的功耗,肯定也是不行的。

識(shí)別什么特性是必須的,什么特性可以砍掉,是功耗重要,還是性能重要。在概念計(jì)劃階段就要搞明白。

比如下面這兩個(gè)東西,功耗肯定是差異巨大的。

3.2 設(shè)計(jì)驗(yàn)證階段

功耗優(yōu)化的大部分手段出在設(shè)計(jì)驗(yàn)證階段。我們一個(gè)一個(gè)來講。

3.2.1 算法

算法階段優(yōu)化此處介紹三個(gè)常用的。

降低A和N:減少計(jì)算復(fù)雜度。算法最有效的做法是直接減少算法的復(fù)雜度。比如同樣一個(gè)人臉識(shí)別的AI芯片,在識(shí)別精度相同的情況下,使用VGG明顯比使用ResNet甚至MobileNet這些輕量化網(wǎng)絡(luò)費(fèi)功耗的多。所以算法部門一個(gè)永恒的目標(biāo)是如何在不太損失精度的前提下降低計(jì)算復(fù)雜度。有時(shí)候同樣一個(gè)任務(wù)精度一樣計(jì)算復(fù)雜度可能會(huì)降低十倍不止。

降低A:算法優(yōu)化翻轉(zhuǎn)概率。這個(gè)事情比較玄學(xué)。比如訓(xùn)練一個(gè)神經(jīng)網(wǎng)絡(luò),盡量讓網(wǎng)絡(luò)推理的過程中翻轉(zhuǎn)概率最低。再比如算法來個(gè)自適應(yīng),在信號(hào)比較好的時(shí)候采用一個(gè)比較弱的信道估計(jì),在信號(hào)不好的時(shí)候啟動(dòng)比較強(qiáng)的信道估計(jì)等等。

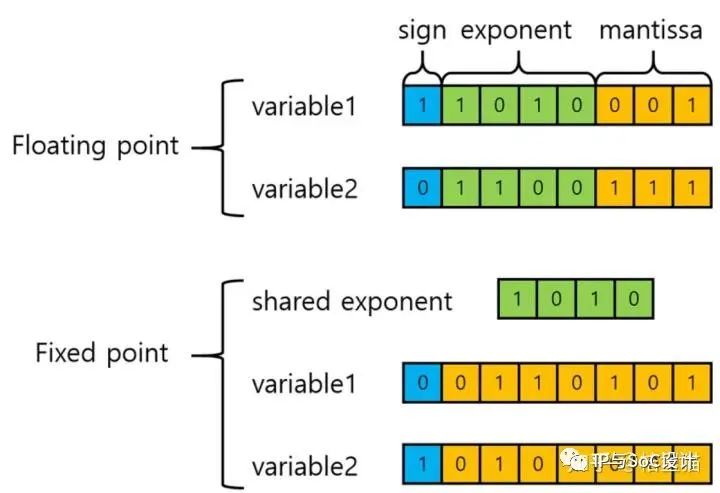

降低N:降低計(jì)算精度。對(duì)于芯片來講,除了特殊需求,大多數(shù)計(jì)算都是定點(diǎn)的。那采用什么精度的定點(diǎn)就很容易影響功耗。比如計(jì)算神經(jīng)網(wǎng)絡(luò)的時(shí)候,由于網(wǎng)絡(luò)自身就可以容錯(cuò),算法可以不斷壓縮定點(diǎn)。比如用個(gè)8bit, 4bit看看結(jié)果如何。這部分大量運(yùn)用于各類芯片。尤其神經(jīng)網(wǎng)絡(luò),通信等等。如何降低精度有一系列的辦法。采用指數(shù)壓縮,分組定點(diǎn)化等等。舉個(gè)簡單的例子,可以讓神經(jīng)網(wǎng)絡(luò)不通層有不同的定點(diǎn)化來降低計(jì)算精度。

舉個(gè)簡單的例子,把兩個(gè)浮點(diǎn)的指數(shù)為共享,這樣相同精度下節(jié)省存儲(chǔ)量,或者相同比特位寬下提高精度。

3.2.2 概設(shè)

概設(shè)階段主要是從模塊級(jí)對(duì)芯片的功耗進(jìn)行控制。

降低A:Clock Gating。一般模塊級(jí)的clock gating信號(hào)都要我們手動(dòng)根據(jù)設(shè)計(jì)功能加入的。比如在CPU核沒有任務(wù)的時(shí)候要把CPU的clock直接關(guān)掉,節(jié)省時(shí)鐘網(wǎng)絡(luò)的功耗。

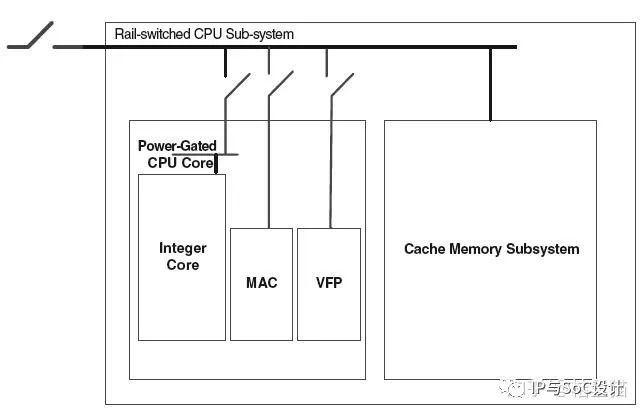

降低V:Power Gating。對(duì)于能預(yù)測(cè)長時(shí)間不用的模塊,要設(shè)計(jì)power gating, 將不用的模塊直接關(guān)掉。如下圖所示,一個(gè)CPU系統(tǒng),其實(shí)Memory可能不能掉電,Core和MAC什么的如果不用都可以power gating。

power gating有一定成本(功耗和面積上都有),所以一個(gè)模塊要不要做power gating要逐個(gè)分析。

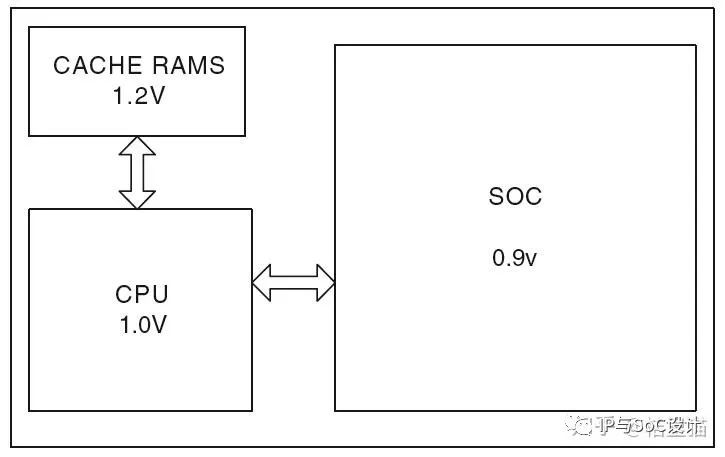

降低V:Multi-VDD。現(xiàn)在的芯片都比較大,沒必要所有模塊都跑在一個(gè)電壓下。比如下面這樣,CACHE RAMS電壓高一點(diǎn),SOC部分電壓可以低一點(diǎn)。

降低F: Multi-Clock Domain。和上一條往往有聯(lián)動(dòng)關(guān)系,這個(gè)地方還附帶有另一個(gè)效果,降低F。可以根據(jù)電壓域講芯片分為若干的時(shí)鐘域,有些部分時(shí)鐘慢一些來減小功耗。

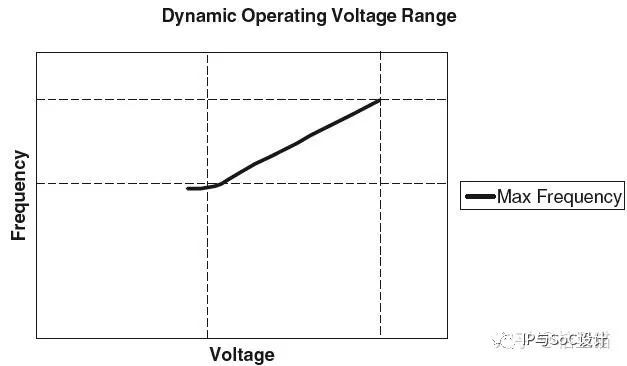

降低V和F:DVFS。Dynamic Voltage and Frequency Scaling。這個(gè)是現(xiàn)代芯片中非常常用的手段。根據(jù)業(yè)務(wù)負(fù)載自動(dòng)的調(diào)整電壓和頻率。如下圖所示,一般來講,電壓越高芯片能跑的頻率也就越高。DVFS就是反其道行之。比如手機(jī)只有2G網(wǎng),手機(jī)芯片就顯然不用跑在最高頻率。從而可以大量減少功耗。

3.2.2 編碼

接下來就到了最喜聞樂見的編碼階段。

個(gè)人認(rèn)為這個(gè)部分功耗的優(yōu)化有用,但有的明顯,有的不明顯,和i++與++i有異曲同工之妙,比如常見的FSM狀態(tài)機(jī)要用格雷編碼這事兒,就只能說節(jié)省了,但仿佛又沒有節(jié)省。但由于編碼自帶炫技屬性,所以寫代碼的時(shí)候還是要在意一下,此處講講我覺得最重要的三點(diǎn)。

降低A或者V:Memory Cell的低功耗使用。這個(gè)在編碼階段是絕對(duì)要注意到的。SRAM對(duì)于數(shù)據(jù)處理類的芯片來講功耗開銷非常大。這個(gè)我們重點(diǎn)講講。

·存儲(chǔ)量大的情況下盡量使用Memory。采用SRAM cell實(shí)現(xiàn)的讀寫比使用寄存器堆使用的讀寫省功耗。所以如果存儲(chǔ)量夠大,建議使用SRAM。

·選用低功耗的SRAM Cell。SRAM cell一般都是由memory compiler生成的。比如購買ARM的compier. 一般來講會(huì)提供各種類型的SRAM cell。盡量選擇低功耗的SRAM cell。

·SRAM Cell要盡量使用低功耗mode。SRAM一般會(huì)留出power gating, deep sleeping, retention, clock gating等等端口,這些端口要根據(jù)實(shí)際情況用起來,SRAM不用的時(shí)候要把它低功耗起來。

·避免無意義的讀寫。SRAM的讀寫都是有功耗的。比如訪問嫌麻煩,降rd_en一直拉有效這種做法是要避免的。同時(shí),即使沒有wen, 數(shù)據(jù)端口信號(hào)變化也會(huì)產(chǎn)生功耗,能不變盡量不變。

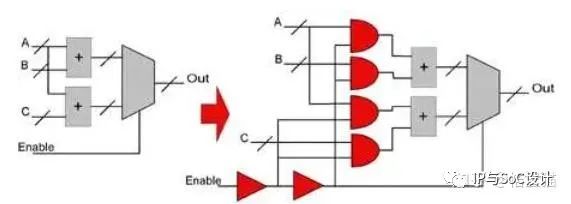

降低A:操作數(shù)隔離。比如加法器,乘法器這些部件,組合邏輯,只要操作數(shù)有變化就會(huì)產(chǎn)生功耗。所以采用操作數(shù)隔離,將不用的操作數(shù)直接置0可以省功耗。

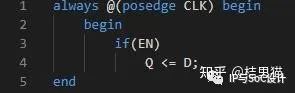

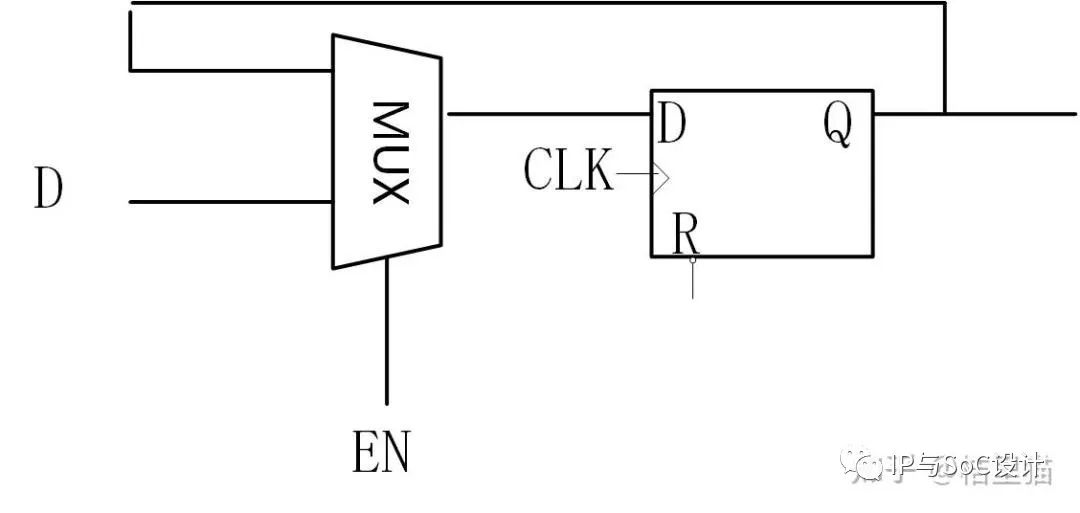

降低A:自動(dòng)門控。這個(gè)非常好實(shí)現(xiàn),節(jié)省功耗效果還算明顯。綜合工具可以直接幫忙加入。如下圖所示,只要代碼風(fēng)格寫的好,綜合工具就能自動(dòng)幫你門控。

如果不開低功耗的綜合,綜合出的電路是這樣的

如果開了低功耗的綜合,綜合出來就是這樣的

如果Q就1兩個(gè)bit,那其實(shí)使用mux更省一些。如果Q比較寬,例如Q為32bit的話插入ICG就收益非常明顯。

既節(jié)省了功耗,1個(gè)ICG肯定是小于32個(gè)mux。所以自動(dòng)門控可以既節(jié)省功耗,又節(jié)省面積。

降低A:無復(fù)位寄存器。數(shù)據(jù)通路上往往還有辦法。。。比如大量使用寄存器的地方,其實(shí)可以不用復(fù)位,采用無復(fù)位的寄存器,既可以節(jié)省面積,防止擁塞,又可以節(jié)省功耗。

3.2.3 實(shí)現(xiàn)

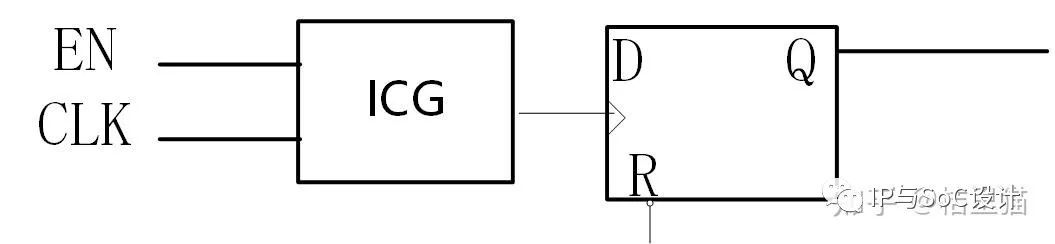

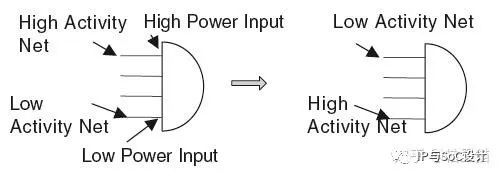

這個(gè)步驟主要是由DC搞邏輯門優(yōu)化的騷操作。不需要我們干預(yù)什么,比如下面這樣。

對(duì)于上面這種,對(duì)于一個(gè)門有可能各個(gè)Pin的功耗其實(shí)不一樣的。把變化率低的信號(hào)mapping到低功耗的pin上就有好處。

3.2.4 較為激進(jìn)的新技術(shù)

這部分可能目前的芯片不一定用的上。先提一嘴。等著技術(shù)發(fā)展。后面也可以專門寫寫這些新技術(shù)。

·Process In Memory,存內(nèi)計(jì)算。能節(jié)省Memory到計(jì)算單元的搬運(yùn)功耗。

·Nonvolatile Memory, 非易失存儲(chǔ)。用非易失的存儲(chǔ),一方面,讀功耗比SRAM小,二方面,不用就關(guān)電壓。

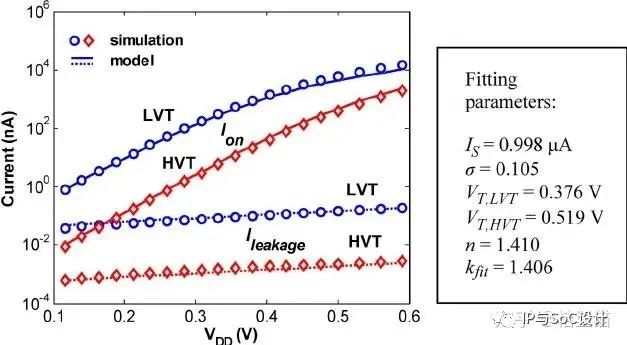

·亞閾值/近閾值技術(shù)。設(shè)計(jì)電路,降電壓降到閾值附近甚至低于閾值。增大靜態(tài)功耗的代價(jià)換取小的動(dòng)態(tài)功耗。

3.3 流片制造階段

這個(gè)階段其實(shí)對(duì)于設(shè)計(jì)者來說大多數(shù)不可見的。我們講講兩個(gè)可見的。主要是std_cell可以選擇。理論上,隨著工藝的演進(jìn),電壓會(huì)降低,但是由于工藝越先進(jìn),一般芯片做出來頻率越快,單位面積上的晶體管也更大,所以工藝演進(jìn)對(duì)功耗的影響其實(shí)不好說。

3.3.1 Multi-bit Cell

比如寄存器,這個(gè)東西版圖一般是由代工廠來給的。單個(gè)寄存器版圖如下圖。

如果這個(gè)東西不定制,DC會(huì)搞出兩個(gè)一毛一樣的cell,這時(shí)候提供這樣一個(gè)2bit cell

或者這樣提供一個(gè)4bit cell,功耗就能小。

能降功耗主要?dú)w功于clock pin電容降低了,時(shí)鐘樹buffer減小了。繞線也變短了。

3.3.2 提供不同閾值的晶體管

一般來講,代工廠會(huì)提供好多種閾值電壓的cell. HVT和LVT就是兩種典型cell。HVT晶體管不容易switch, 功耗低LVT速度更快,但功耗更大。

3.4 封裝測(cè)試階段

封裝測(cè)試階段芯片其實(shí)已經(jīng)都定型了,芯片本身的功耗優(yōu)化還剩最后一個(gè)手段。AVS。AVS指的是Adaptive Voltage Scaling。基本原理是芯片做出來后篩選一波。有些芯片正好就造的比較好,那就降低點(diǎn)電壓,有的芯片造的不行,只能提電壓。由于工藝誤差等等各方面因素,芯片就是有體質(zhì)的不同。。。比如intel的CPU,有的能超頻,有的超不動(dòng)。這個(gè)階段就在瘋轉(zhuǎn)測(cè)試階段來做。篩片降功耗。

4 總結(jié)

本文是這個(gè)系列的一篇彩蛋,講講從全流程如何優(yōu)化芯片的功耗,只能講個(gè)大概,實(shí)際情況還需要在項(xiàng)目中摸索。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

455文章

50732瀏覽量

423262 -

集成電路

+關(guān)注

關(guān)注

5387文章

11536瀏覽量

361664 -

CMOS

+關(guān)注

關(guān)注

58文章

5710瀏覽量

235427

原文標(biāo)題:一顆芯片的前世今生:何為低功耗

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ADS1292工作電壓低于2.7V是否可以正常工作?

DMD芯片的功耗與效率優(yōu)化方法

低功耗SOC芯片的優(yōu)勢(shì)

Orin芯片功耗分析

物聯(lián)網(wǎng)系統(tǒng)中常用的低功耗自組網(wǎng)無線傳輸方案(三)_藍(lán)牙芯片篇

柵極驅(qū)動(dòng)芯片選型低功耗原因

一款4644芯片低功耗設(shè)計(jì)思路解析

低功耗芯片的市場(chǎng)發(fā)展前景怎么樣?

不間斷電源輸出電壓低怎么維修

LMV65x 12MHz低電壓低功耗放大器數(shù)據(jù)表

LMV721 LMV722 10MHz低噪聲低壓低功耗運(yùn)算放大器數(shù)據(jù)表

PC93XX高耐壓低功耗線性穩(wěn)壓器/LDO數(shù)據(jù)手冊(cè)

OTP低功耗語音芯片的工作原理與產(chǎn)品特性

如何壓低芯片的功耗

如何壓低芯片的功耗

評(píng)論