高性能計(jì)算(HPC)市場進(jìn)入超預(yù)期的高速發(fā)展階段,先進(jìn)封裝Advanced Packaging成為高性能運(yùn)算芯片成功與否的關(guān)鍵技術(shù)。在第十四屆中國集成電路封測產(chǎn)業(yè)鏈創(chuàng)新發(fā)展高峰論壇(CIPA 2022)“高峰論壇”上,矽品研發(fā)中心副總經(jīng)理王愉博博士與產(chǎn)業(yè)探討未來高性能計(jì)算的先進(jìn)封裝發(fā)展趨勢。

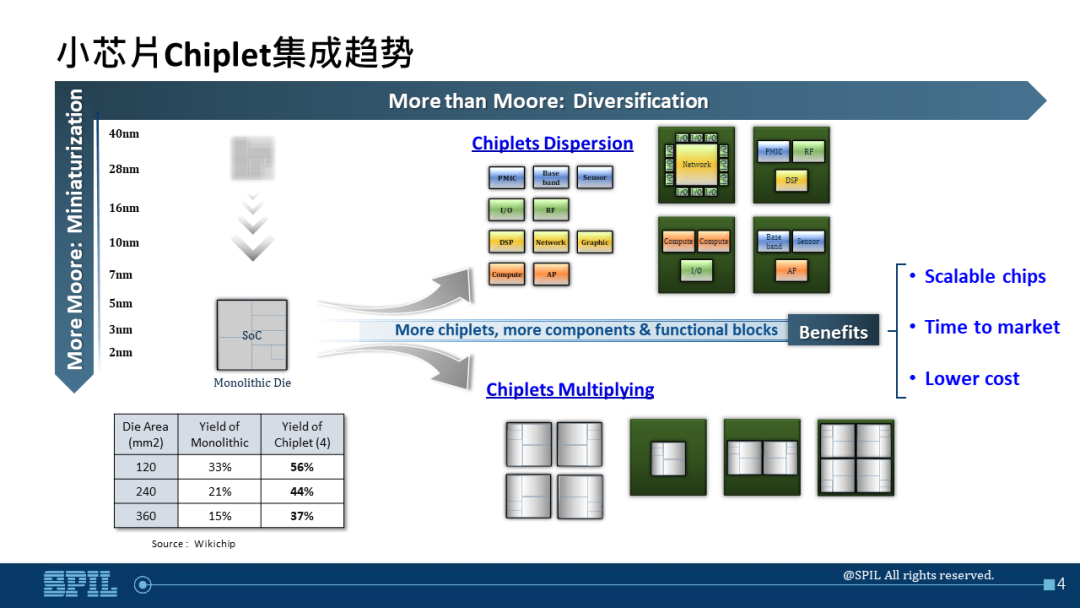

數(shù)據(jù)處理需求激增,AI算力對于高性能計(jì)算GPU的需求日趨增長,芯片上的晶體管數(shù)量也以十倍的成長率迅速增長。為了滿足晶體管的數(shù)量,芯片的尺寸越來越大,但同時受限于radicle size而造成發(fā)展瓶頸。在摩爾定律趨緩,芯片的價格越來越高,良率因?yàn)樾酒某叽缭龃蠖找嫦陆担⌒酒珻hiplet已成為先進(jìn)封裝發(fā)展的重要趨勢。

王博士說明在最新一代Chiplet,依照不同的功能做區(qū)隔,使整體的速度效益達(dá)到明顯的提升。或是利用封裝體的形態(tài)把兩個相同的芯片相互串聯(lián),發(fā)揮更高的效能,這種Chiplet表現(xiàn)方式可避免芯片因尺寸太大而造成晶圓廠制作的良率損失。無論Foundry或OSAT,都可以運(yùn)用多種封裝相結(jié)合的方式整合,包含2.5D/3D IC封裝,以及FO-EB及FO-MCM封裝等,王博士詳細(xì)分析封裝形態(tài)如何把Chiplet運(yùn)用在未來高性能運(yùn)算。

UCLe產(chǎn)業(yè)聯(lián)盟

由日月光、AMD、Arm、Google Cloud、Intel、Meta、微軟(Microsoft)、高通(Qualcomm)、三星(Samsung)和臺積電(TSMC)等半導(dǎo)體業(yè)者共同組成UCIe(Universal Chiplet Interconnect Express)產(chǎn)業(yè)聯(lián)盟持續(xù)推動芯片互連(die-to-die interconnect)技術(shù)標(biāo)準(zhǔn)化和促進(jìn)開放式Chiplet生態(tài)系統(tǒng),目前已有超過40家公司加入聯(lián)盟,透過UCIe制定協(xié)定標(biāo)準(zhǔn)將可有效提高Chiplet生態(tài)系統(tǒng)整體效率,降低開發(fā)時間和成本。

日月光在封裝和互連平臺技術(shù)的專業(yè)知識,有助于確保UCIe提出的標(biāo)準(zhǔn)切實(shí)可行,并且在封裝制造具有商業(yè)可行性和成本效益。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

456文章

50886瀏覽量

424162 -

日月光

+關(guān)注

關(guān)注

0文章

146瀏覽量

19069 -

chiplet

+關(guān)注

關(guān)注

6文章

433瀏覽量

12603

原文標(biāo)題:Chiplet 小芯片的時代機(jī)遇與趨勢

文章出處:【微信號:ASE_GROUP,微信公眾號:ASE日月光】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Chiplet在先進(jìn)封裝中的重要性

Chiplet技術(shù)有哪些優(yōu)勢

IMEC組建汽車Chiplet聯(lián)盟

全球視野下的海外爬蟲IP:趨勢、機(jī)遇與風(fēng)險

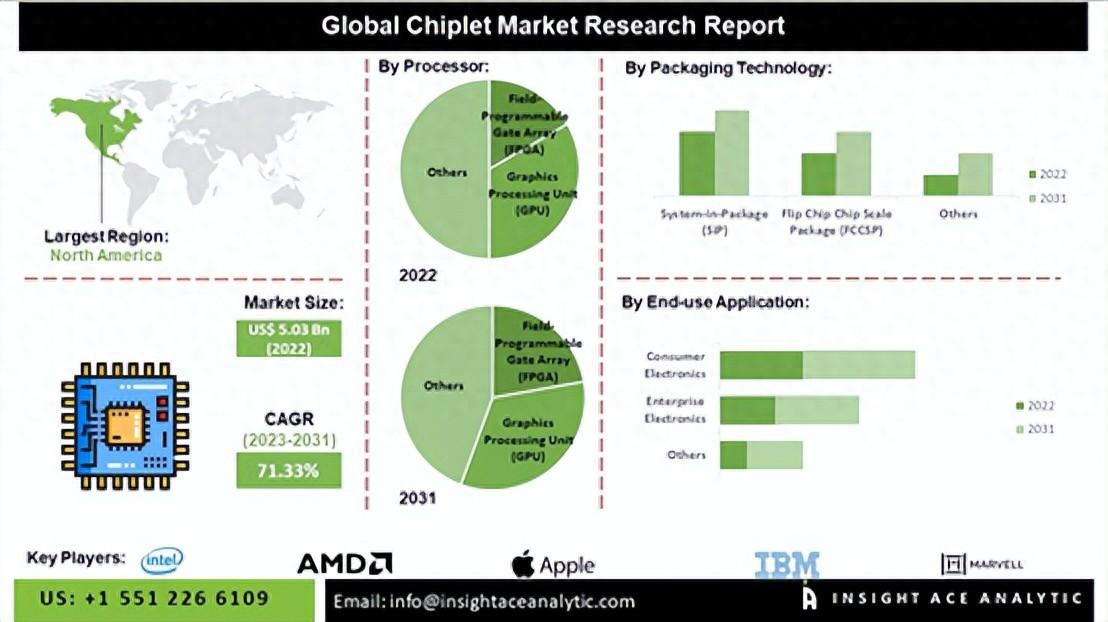

2031年全球Chiplet市場預(yù)測

國產(chǎn)半導(dǎo)體新希望:Chiplet技術(shù)助力“彎道超車”!

剖析 Chiplet 時代的布局規(guī)劃演進(jìn)

西門子EDA創(chuàng)新解決方案確保Chiplet設(shè)計(jì)的成功應(yīng)用

Chiplet是否也走上了集成競賽的道路?

什么是Chiplet技術(shù)?

Chiplet技術(shù)對英特爾和臺積電有哪些影響呢?

芯礪智能Chiplet Die-to-Die互連IP芯片成功回片

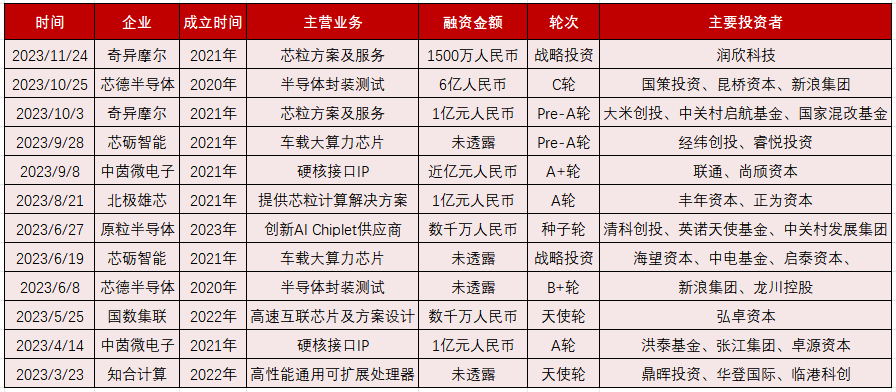

2023年Chiplet發(fā)展進(jìn)入新階段,半導(dǎo)體封測、IP企業(yè)多次融資

Chiplet小芯片的時代機(jī)遇與趨勢

Chiplet小芯片的時代機(jī)遇與趨勢

評論