默認情況下,VitisHLS會對待綜合的C函數使用ap_ctrl_hs接口,這其實是一種握手方式。在這個接口中,我們會看到ap_start、ap_idle、ap_ready和ap_done等信號(這些信號被稱為Block-level輸入/輸出信號)。其中ap_start是輸入信號,而其余三個信號是輸出信號。那么我們如何根據這些信號管理輸入數據呢?這就要理解這些信號之間的時序關系。為便于說明,我們以一個簡單的算法為例。

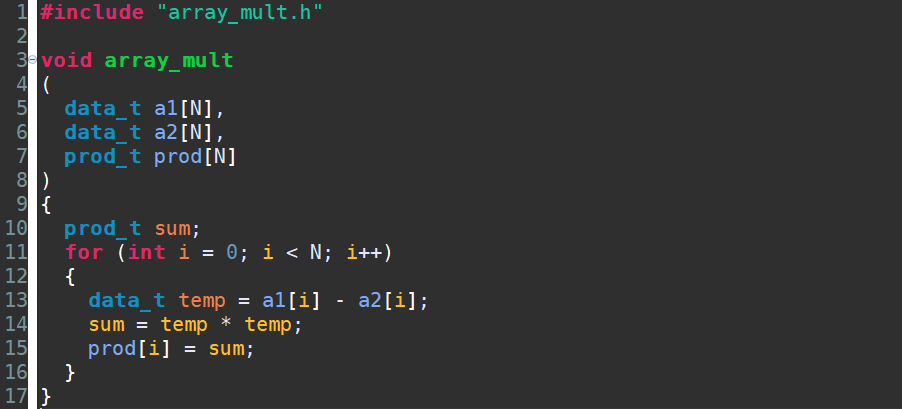

如下圖所示代碼片段。函數array_mult有3個形參。其中a1和a2是長度為N的一維數組,兩者對應元素相減再平方即為另一形參prod。顯然,prod也是長度為N的一維數組。

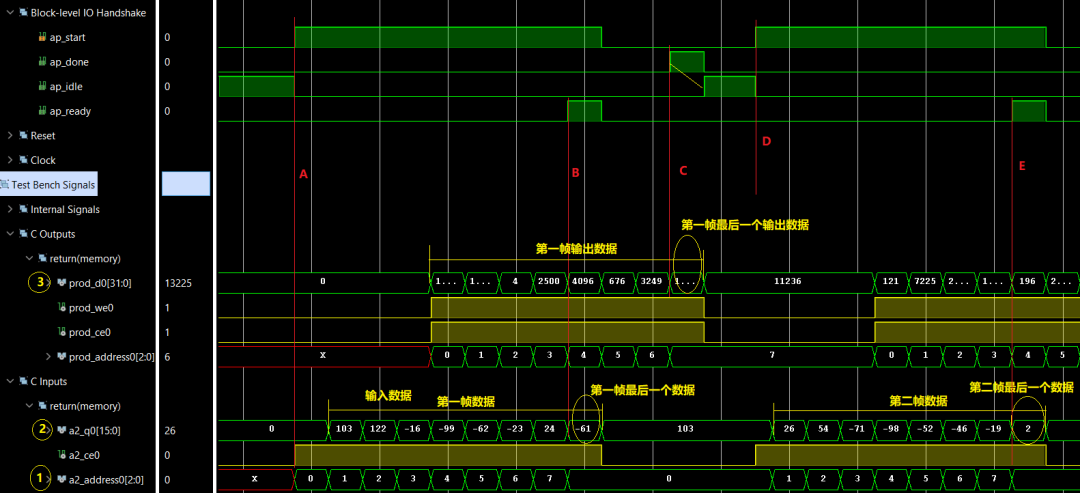

為了觀察這些Block-level信號之間的時序關系,我們在仿真時將多次調用函數array_mult。為此,在描述測試激勵時,輸入激勵以兩個二維數組形式給出,這兩個二維數組對應的每一列作為array_mult的輸入。假定這兩個二維數組是8行4列的數組,C/RTLco-sim仿真結果波形如下圖所示。

標記1為數組a2對應存儲單元的讀地址a2_address,共8個數據;標記2顯示了讀書的數據數值a2_q0,可以看到兩者相差一個時鐘周期。那么什么時候a2_address可以發生變化呢?我們從標記A可以看到,在標記A左邊,ap_idle為高電平,表明該模塊處于空閑狀態,標記A之后,ap_start為高電平,同時ap_idle變為低電平。一旦ap_start為高,a2_ce0即為高,表明可以開始讀取a2對應的數據。當第一幀8個數據讀取完畢,即讀取到第一幀最后一個數據時,ap_ready為由低電平變為高電平且持續一個時鐘周期,表明第一幀輸入數據已讀取完畢,如圖中標記B。緊接著ap_start也由高電平變為低電平。當第一幀計算完畢,輸出對應的8個數據后,ap_done由低電平變為高電平并持續一個時鐘周期,如圖中標記C。當ap_done由高變低時,ap_idle則由低變高,表明可以再次啟動該模塊。因此,我們可以看到標記D處ap_start為高,之后a2_ce0由低變高開始讀取第二幀輸入數據。讀取到第二幀輸入數據的最后一個數據后,ap_ready由低電平變為高電平。

由此我們可以得出如下結論:

ap_start受ap_idle影響,只有當ap_idle為高時,才可以啟動ap_start,將其由低電平變為高電平;

ap_ready為高電平時,表明已完成一幀的輸入數據讀取任務;

ap_done為高電平時,表明已完成一幀的輸出數據寫入任務;

ap_done持續一個時鐘周期由高變低后,ap_idle會由低變高。

審核編輯:湯梓紅

-

函數

+關注

關注

3文章

4371瀏覽量

64203 -

HLS

+關注

關注

1文章

131瀏覽量

24648

原文標題:如何理解HLS Block-level輸入輸出信號之間的時序關系

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

TLV320AIC3106有10個模擬輸入和7個模擬輸出,這些模擬輸入輸出如何理解?

HLS系列 – High LevelSynthesis(HLS) 的端口綜合1

HLS系列–High Level Synthesis(HLS)的端口綜合6

什么是輸入輸出模塊_輸入輸出模塊有什么作用

GPIO通用輸入輸出

boost升壓電路輸入輸出關系

plc帶模擬量輸入輸出和不帶模擬量輸入輸出有什么區別啊?

輸入輸出電壓差與效率的關系

評論