最近經(jīng)常聽到Chiplet的概念,據(jù)說AMD的銳龍系列就是利用chiplet技術(shù)逆襲Intel的。那么chiplet和SoC,SiP,IP核等有什么關(guān)系呢?找了不少資料,特來總結(jié)一番。其實(shí)這些概念的出現(xiàn)有一個(gè)共同的主線,讓IC設(shè)計(jì)和制造越來越容易。

一、IP

早期的復(fù)制電路都是全定制,比如Intel的4004cpu,這種設(shè)計(jì)非常耗時(shí)。考慮到cpu的很多模塊有相似的地方,能不能把這些東西模塊化?于是就有了IP核的概念,Intelligent Property,即知識(shí)產(chǎn)權(quán)核。

IP核在EDA上有非常重要的地位,我們熟知的Synopsys公司就是IP巨頭,它將一些復(fù)雜的功能模塊,如FIR濾波器、SDRAM控制器、PLL鎖相環(huán)等封裝好,供開發(fā)者直接調(diào)用,避免重復(fù)勞動(dòng),他們會(huì)收取相應(yīng)的專利費(fèi)。ARM公司本質(zhì)上就是買IP核。

IP核分成三類:軟核、固核與硬核。軟核就是我們通常寫的verilog行為描述代碼,靈活性與適應(yīng)性較強(qiáng);固核是門級(jí)網(wǎng)表形式的代碼,是IP的主流形式之一;硬核是GDSII版圖文件,不能修改。

二、SoC

SoC(system on chip)片上系統(tǒng)。我們臺(tái)式機(jī)的存儲(chǔ)器、電源模塊、功耗管理模塊等都是分開的,而SoC是將這些圍繞CPU的關(guān)鍵模塊集成在一個(gè)芯片上,這樣才會(huì)有我們的筆記本、手機(jī)等小巧強(qiáng)大電子設(shè)備。

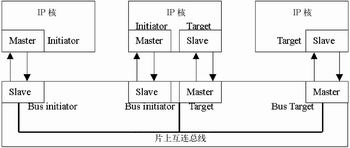

SoC強(qiáng)調(diào)整體設(shè)計(jì),包含總線架構(gòu)、IP核復(fù)用、軟硬件協(xié)同設(shè)計(jì)、低功耗等技術(shù),將CPU、存儲(chǔ)器、各種接口控制模塊、互聯(lián)總線等集成在一起,達(dá)到減小面積、提高速度、降低功耗、節(jié)約成本等目的。

三、SiP

SiP(System-in Package)系統(tǒng)級(jí)封裝。將處理器、存儲(chǔ)器、FPGA等功能芯片集成在一個(gè)封裝內(nèi)。粗粗一看,似乎和SoC一樣,但區(qū)別還是挺大的。

SoC是在同一芯片、同一種工藝下完成的;SiP則可以將不同工藝器件,如MEM、光學(xué)器件、射頻器件等不同材質(zhì)、不同工藝節(jié)點(diǎn)的設(shè)備垂直堆疊或水平排列,做園片級(jí)別的封裝。這是超越摩爾定律的重要實(shí)現(xiàn)路徑。

SiP的實(shí)現(xiàn)需要多種封裝技術(shù),如引線鍵合、倒裝芯片、芯片堆疊、基板腔體、基板集成RF器件、埋入式電阻電容電感、硅通孔TSV等。

四、Chiplet

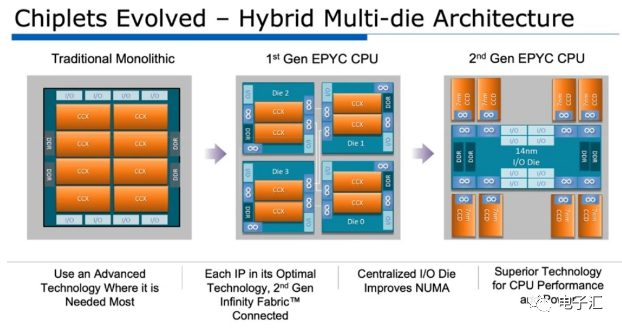

Chiplet即小芯片,相當(dāng)于將硬核IP再制造成芯片。還是回到SoC,隨著工藝節(jié)點(diǎn)的推進(jìn),成本越來越昂貴,SoC會(huì)增大芯片面積,導(dǎo)致良品率下降,成本很高。這時(shí)候,AMD給了新方案Chiplet。

7nm工藝時(shí),模擬電路無法獲益于晶體管或?qū)Ь€間距的微縮,傳遞信號(hào)的I/O本身凸塊間距微縮進(jìn)展緩慢,用14nm工藝還更加穩(wěn)定。

cpu也進(jìn)入多核時(shí)代,將這些核獨(dú)立制造可以大大提高良率。

如圖,這是AMD的CPU設(shè)計(jì)演進(jìn)圖,從單芯片到小芯片組合,到模擬、I/O采用14nm工藝,整個(gè)成本節(jié)省了41%。

能達(dá)到這樣的效果,要?dú)w功于SiP先進(jìn)的封裝技術(shù)。

審核編輯:劉清

-

SiP

+關(guān)注

關(guān)注

5文章

501瀏覽量

105314 -

SoC芯片

+關(guān)注

關(guān)注

1文章

610瀏覽量

34905 -

SDRAM控制器

+關(guān)注

關(guān)注

0文章

28瀏覽量

8138

原文標(biāo)題:IP,SoC,SiP和Chiplet的區(qū)別

文章出處:【微信號(hào):電子匯,微信公眾號(hào):電子匯】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

簡單介紹SoC與SiP中芯片解密的應(yīng)用

開放核協(xié)議:IP核在SoC設(shè)計(jì)中的接口技術(shù)

基于IP核的SoC接口技術(shù)

MCU、DSP和FPGA有什么關(guān)系

基于IP核復(fù)用的SoC設(shè)計(jì)技術(shù)探討

SoC中IP核互連的不同策略

開放核協(xié)議—IP核在SoC設(shè)計(jì)中的接口技術(shù)

chiplet和SoC、SiP及其IP核等有什么關(guān)系呢?

chiplet和SoC、SiP及其IP核等有什么關(guān)系呢?

評(píng)論