AXI4S視頻IP介紹及系統設計指南(一)

本文主要介紹使用AXI4S(AXI4-Stream)接口的視頻IP細節。

介紹

本文總結了AXI4S接口視頻協議,該協議在視頻IP中的應用,其中AXI協議參考:

對于做過BT.1120總線的,這部分學習起來一點問題沒有,只不過信號名稱稍微修改了一下。

1.1 AXI4-Stream 信號接口

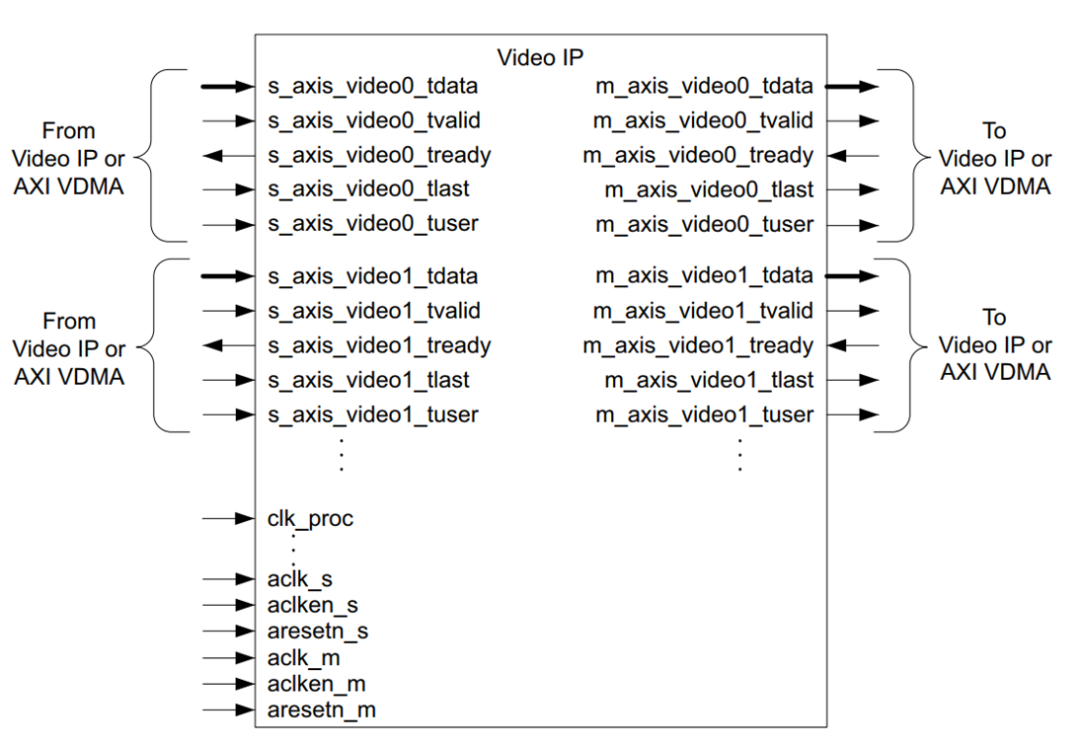

AXI4S攜帶實際的視頻數據(無行場消隱),由主機和從機接口驅動,如Figure 1-1所示。

Figure 1‐1:具有多個AXI4S從(輸入)和主(輸出)接口的視頻IP

空白時段(行場消隱)、音頻數據和輔助數據包不會通過AXI4-Stream上的視頻協議傳輸。Table 1-1 和Table 1-2 中列出AXI4S接口視頻IP需要的所有信號。

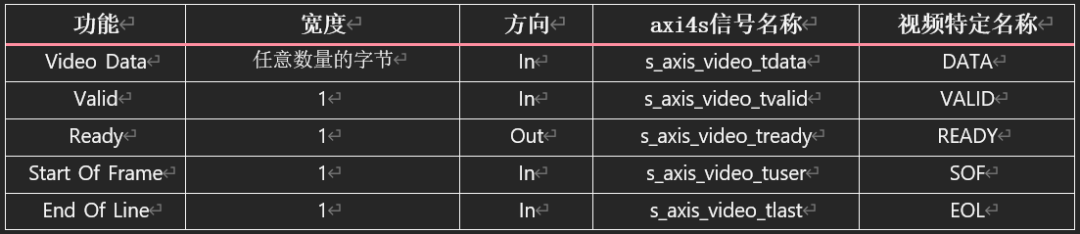

Table 1-1 顯示了輸入(從)側連接器的接口信號名稱和功能。為了避免命名沖突,對于具有多個AXI4S輸入接口的IP,信號前綴s_axis_video應該附加到s_axis_videok,其中k是各個輸入AXI4S的索引;例如,對于流0,axis_video_tvalid變為s_axis_video0_tvalid,對于流1,變為s_axis_video1_tvalid。

Table 1‐1:AXI4S視頻協議輸入(從機)接口信號

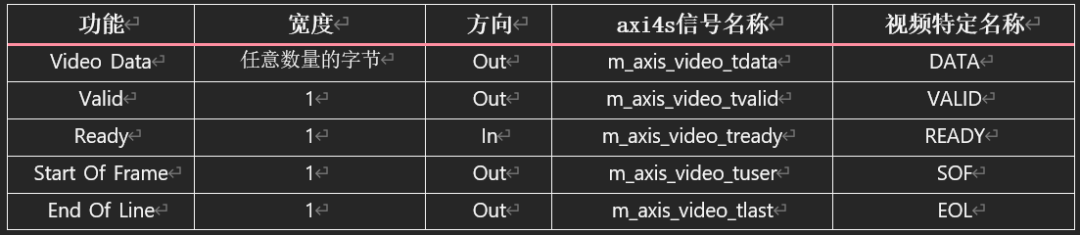

Table 1-2 顯示了輸出(主)側的接口信號名稱和功能。類似地,對于具有多個AXI4-Stream輸出接口的IP,信號前綴m_axis_video應該附加到m_axis_videok 之后,其中k是各個輸出AXI4-Stream的索引;例如,對于流0,axis_video_tvalid變為m_axis_video0_tvalid,對于流1,變為m_axis_video1_tvalid。

Table 1‐2:AXI4S視頻協議輸出(主機)接口信號

1.1.1 READY/VALID 握手

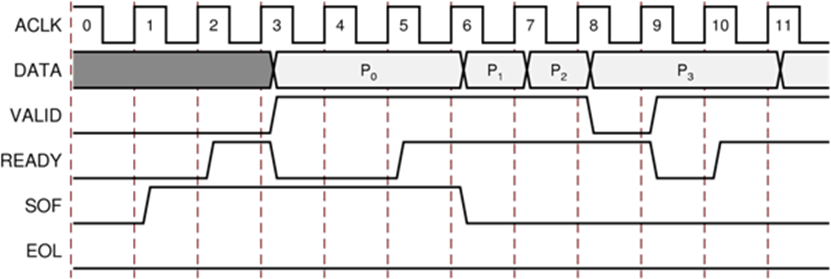

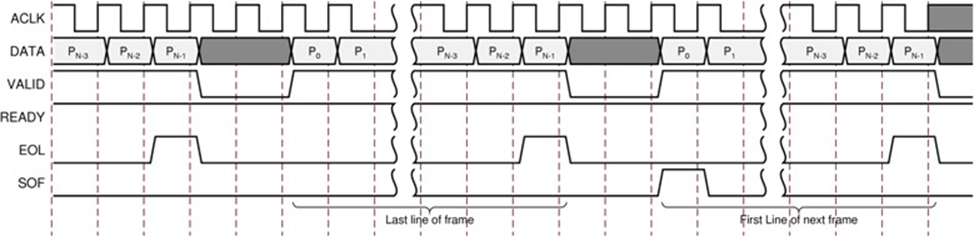

每當就緒(READY)、有效(VALID)、ACLKEN和ARESETn信號在ACLK的上升沿為高電平時,就會發生有效傳輸,如Figure 1-2所示。

Figure 1‐2:就緒/有效握手示例,新幀開始

在有效傳輸期間,數據僅攜帶有效視頻數據。AXI4S上的視頻不會傳輸空白時段(行場消隱)和輔助數據包。

1.1.2 幀開始信號(start of frame (SOF))

幀開始(SOF)信號通過AXI4S TUSER0信號進行物理傳輸,表示視頻場或幀的第一個像素。SOF脈沖是一個有效的事務寬度,并且必須與場或幀的第一個像素一致(Figure 1-2).SOF充當幀同步信號,允許下游內核重新初始化,并檢測場或幀的第一個像素。

1.1.3 行尾信號(End of Line Signal)

行尾(The end of line,EOL)信號通過AXI4S TLAST信號進行物理傳輸,表示一行的最后一個像素。EOL脈沖是一個有效的事務寬度,并且必須與掃描線的最后一個像素一致(Figure 1-3).

Figure 1‐3:EOL和SOF信號的使用

1.2 數據格式

為了傳輸視頻數據,數據格式對物理數據信號的邏輯信道子集進行編碼。視頻模塊之間的AXI4S接口可以有助于使用不同精度(例如,每個顏色通道8、10或12位)和/或不同格式(例如,RGB或YUV 420)以及每個數據拍不同數量的像素來傳輸視頻。

總結就是,數據格式通過AXIS接口的TDATA信號線傳輸,根據傳輸的視頻格式改變信號線的寬度。

1.2.1 AXI4-Stream 特定參數化

視頻IP配置參數在第3章的IP參數化中描述。AXI4S接口視頻協議的具體參數在Table 1-3中列出。

Table 1‐3:AXI4-Stream 特定參數化

C_tk_AXIS_TDATA_WIDTH參數確定AXI4S接口tk上可變寬度接口信號TDATA的寬度,其中接口類型t可以具有指定主或從接口的值[m,s],而可選整數k指定接口ID。通常,C_tk_AXIS_TDATA_WIDTH是分量數據寬度、每個數據拍的像素/樣本數以及實際視頻格式使用的分量數的函數。

組件數據寬度的推薦參數名稱是C_tk_DATA_WIDTH。可選的格式參數C_tk_VIDEO_FORMAT可以幫助IP使用HDL函數確定數據中存在的顏色成分的數量。視頻IP通常在輸入接口上需要特定的格式,并且可以在IP中硬編碼顏色分量通道的數量。然而,當C_tk_VIDEO_FORMAT(由主接口上的默認值設置)在HDL設計中傳播到從接口時,IP源代碼可以使用斷言執行DRC,以確保AXI4S視頻接口由以預期格式編碼的視頻驅動。

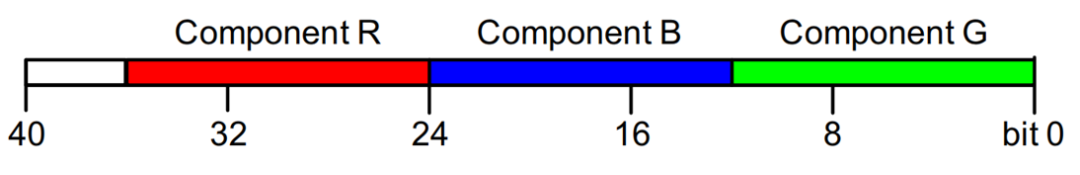

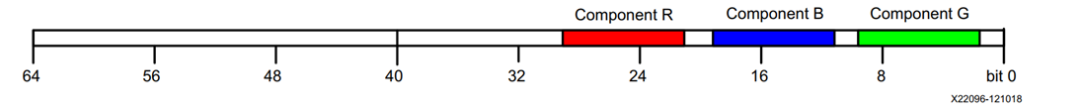

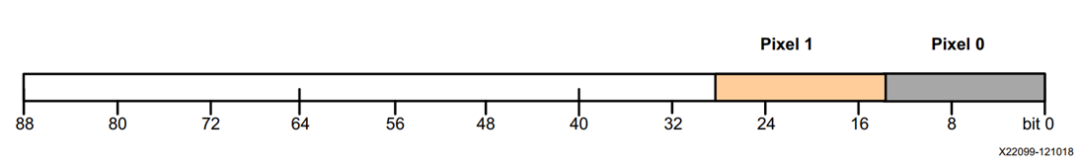

1.2.1 編碼

數據位使用[N-1:0]位編號慣例(N-1至0)表示。數據的隱式子字段的組成部分應該緊密地打包在一起;例如,DW=10位RGB數據打包成30位。如有必要,打包后的數據字應使用最高有效位(msb)進行零填充,使數據寬度使是8的倍數整數,如Figure 1-4所示。

Figure 1‐4:多像素TDATA的視頻數據填充

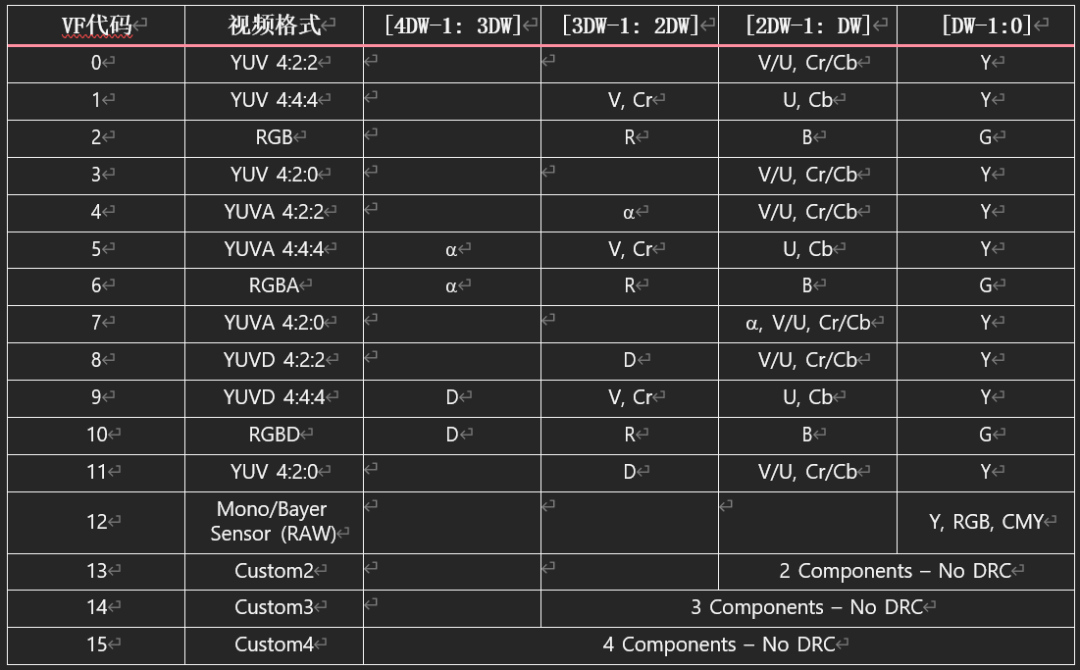

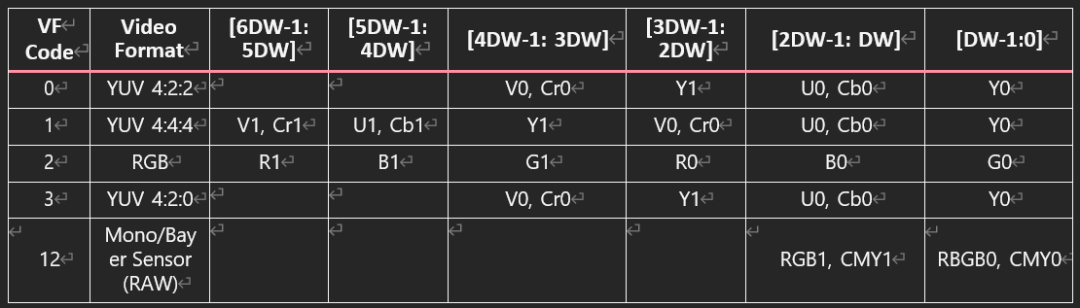

不同格式的詳細表示在Table 1-4中列出,其中DW = C_DATA_WIDTH,VF = C_VIDEO_FORMAT。

Table 1‐4:C_tk_MAX_SAMPLES_PER_CLOCK =1的視頻格式代碼和數據表示

注:對于42和40格式中的任何一種,Cb(或U)和Cr(或V)樣本被分割到兩個數據拍上,但只能在每個時鐘一個樣本的模式下進行。第一個數據拍保持Cb(或U);第二個數據拍保持Cr(或V)。換句話說,幀的第一個有效像素包含[Cb0:Y0],下一個像素包含[Cr0:Y1]。40格式在42格式的基礎上增加了垂直子采樣,這是通過省略每隔一行的色度數據在AXI4-Stream上的視頻中實現的(和BT.1120完全類似)。

注:拜耳傳感器數據也稱為原始數據,一般為RAW8/RAW10/RAW12/RAW14/RAW16等格式。

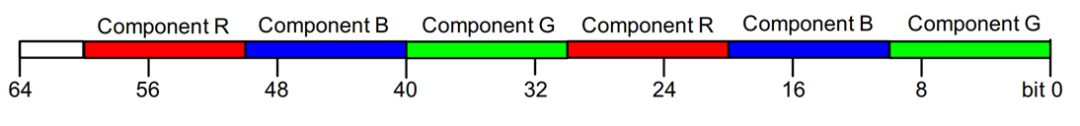

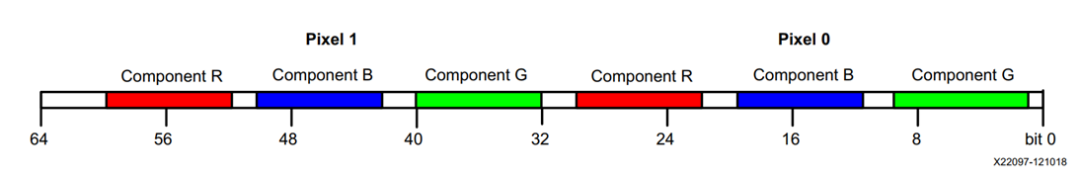

1.2.1.1 多個像素編碼-靜態TDATA配置

當AXI4S攜帶多個樣本/像素時,像素應該從最低有效位(LSB)打包到MSB,例如,最低有效像素應該對應于掃描線中最左邊的像素,或者對應于時間上最早捕獲的像素。例如,如果每個數據拍發送4個樣本/像素,則第一個樣本位于最低有效位,第四個樣本位于最高有效位。

當使用AXI4-Stream上的視頻協議傳輸多個像素或樣本時,與各個像素相關的顏色分量按照下式排列,Table 1-5給出了用于傳輸視頻模式0、1、2、3、12的兩個像素的例子。像素數據被連續打包,像素之間沒有任何填充。當N*DW不是8的倍數整數時,視頻數據在msb上補零,如Figure 1-5所示。

如果行大小不能被每個數據拍的像素/樣本數整除,則行的最后一拍應使用LSB。然后,該行最后一個數據拍的msb中未使用的像素應補零。

Figure 1‐5:TDATA的視頻數據填充 Table 1‐5:視頻格式代碼和數據表示

1.2.1.2 多像素編碼動態TDATA配置

對于視頻IP可以動態改變顏色分量寬度、視頻格式或每個數據拍的像素/樣本數量的應用,像素和分量應該保持在由用于實例化的通用參數確定的靜態位置。例如,如果只有一個像素通過支持每個數據拍最多兩個像素的接口傳輸,則樣本/像素應該與最低有效像素位置對齊。同樣,如果每個器件只有8位通過為每個器件產生的10位接口傳輸,則有效位應MSB對齊,LSB用零填充。

Figure 1-6 和 Figure 1-9中顯示了三個示例。

重要提示:盡管本規范支持動態更改每個數據拍的像素/樣本數,但不建議這樣做,因為并非所有IP都支持此功能。

Figure 1‐6:每個數據拍一個像素,每個器件8位,每個數據拍兩個像素,每個器件總線10位

Figure 1‐7:每個數據拍2個像素,每個器件8位,每個數據拍2個像素,每個器件總線10位

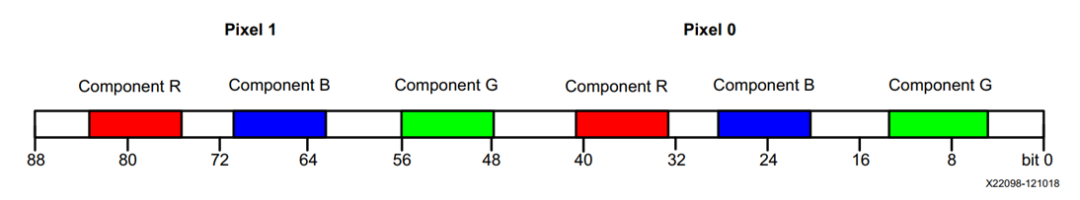

Figure 1-8.捕獲RGB888(具有三個分量的像素,分量寬度為8)。

Figure 1‐8:每個數據拍兩個像素,每個分量八位(RGB888,VF碼2),每個數據拍兩個像素,每個分量總線14位

注意事項:

每個G、B、R元件位于14位空間,MSB對齊。

Figure 1-9.捕獲RAW14(具有單個組件的像素,組件寬度為14)。

Figure 1‐9:每個數據拍兩個像素,每個元件14位(RAW14,VF代碼12),每個數據拍兩個像素,每個元件總線14位

注意事項:

雖然RAW14可能僅使用較低的28位,但完整的AXI4S接口仍然是88位,因為在處理動態TDATA時,如果需要,它必須能夠以每種顏色完整的14位切換到RGB。下游邏輯必須意識到這一點,并應提供適當的總線接口,然后在內部丟棄不使用的位。

比較Figure 1-8 和Figure 1-9中的兩種數據類型組件寬度,RAW14,VF Code 2數據類型具有14位組件和RGB888 (VF Code 2) 8位組件。

因此,RGB888元件在14位元件總線上以MSB對齊、LSB補零的方式放置。此外,RAW14像素緊密地封裝在一起。

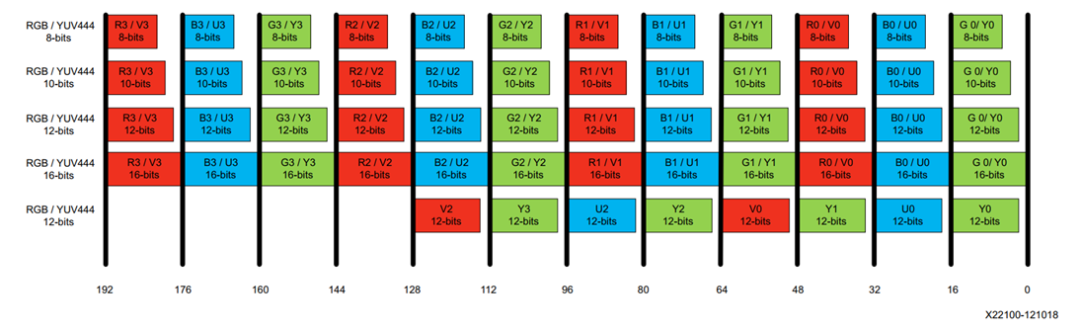

1.2.2 多像素編碼示例

AXI4S視頻接口支持每時鐘雙像素或四像素,對于RGB、YUV444和YUV420色彩空間,每個分量有8位、10位、12位和16位。當參數“每個組件的最大位數”設置為16時,Figure 1-10 顯示了完全符合AXI4S視頻協議的每時鐘四像素數據格式。

Figure 1‐10:四像素數據格式(每個分量的最大位數= 16)

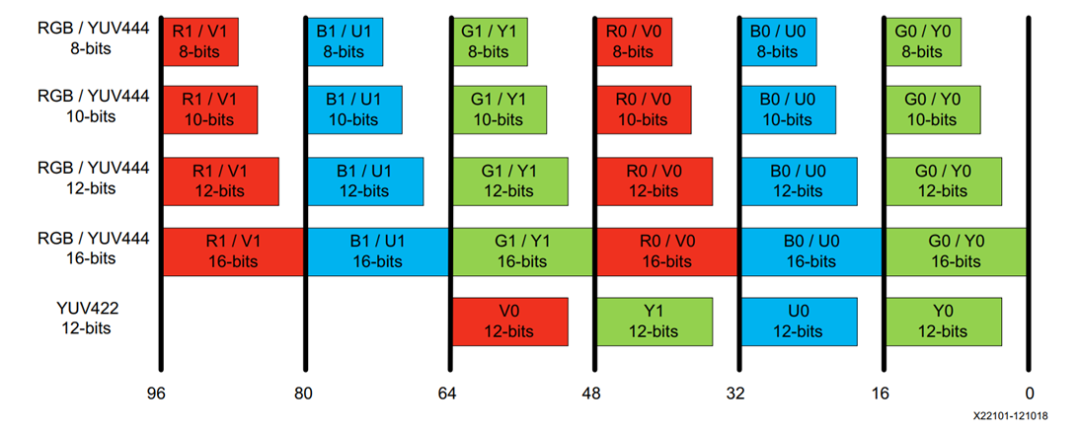

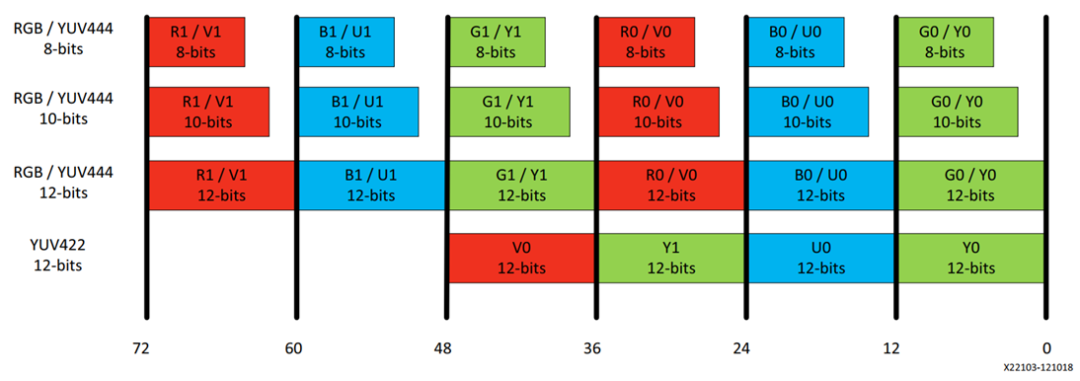

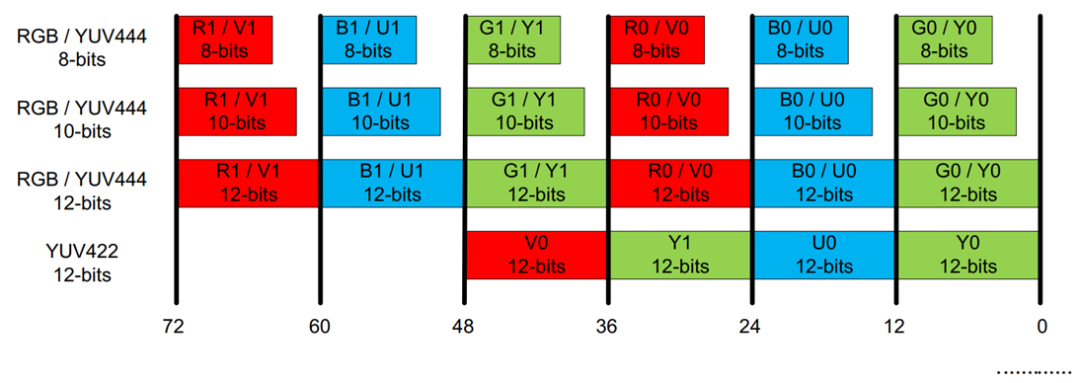

每時鐘雙像素的數據格式完全兼容AXI4S視頻協議,如Figure 1-11所示。

Figure 1‐11:雙像素數據格式(每個組件的最大位數= 16)

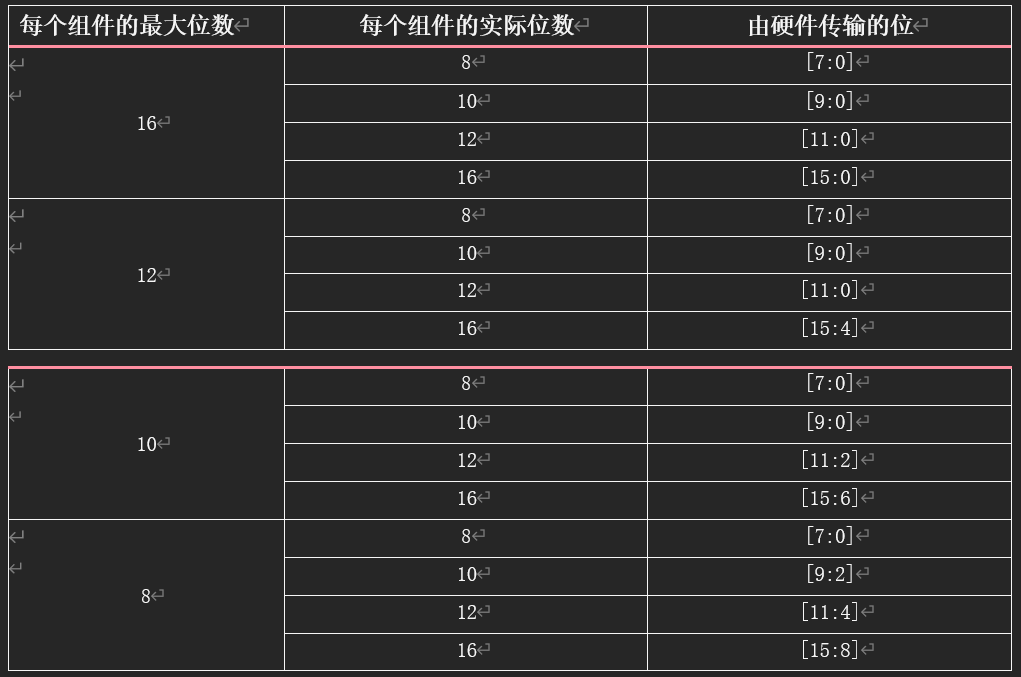

當參數“每個分量的最大比特數”設置為12時,每個分量的實際比特數大于12的視頻格式將被截斷為每個分量的最大比特數。剩余的最低有效位被丟棄。如果每個器件的實際位數小于Vivado IDE中設置的每個器件的最大位數,則所有位都以MSB對齊方式傳輸,其余LSB位以0填充。這適用于所有每個組件的最大位數設置。

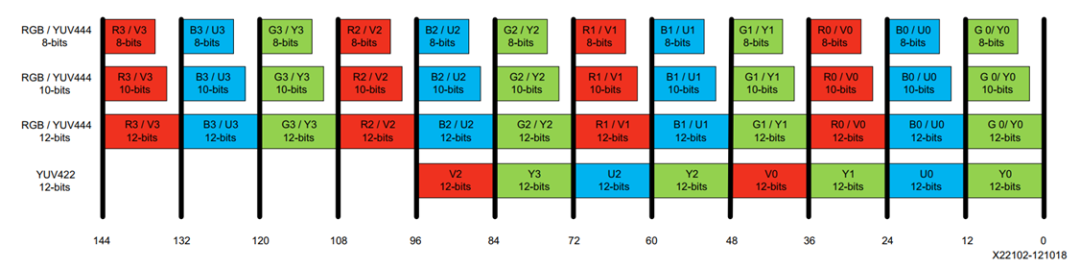

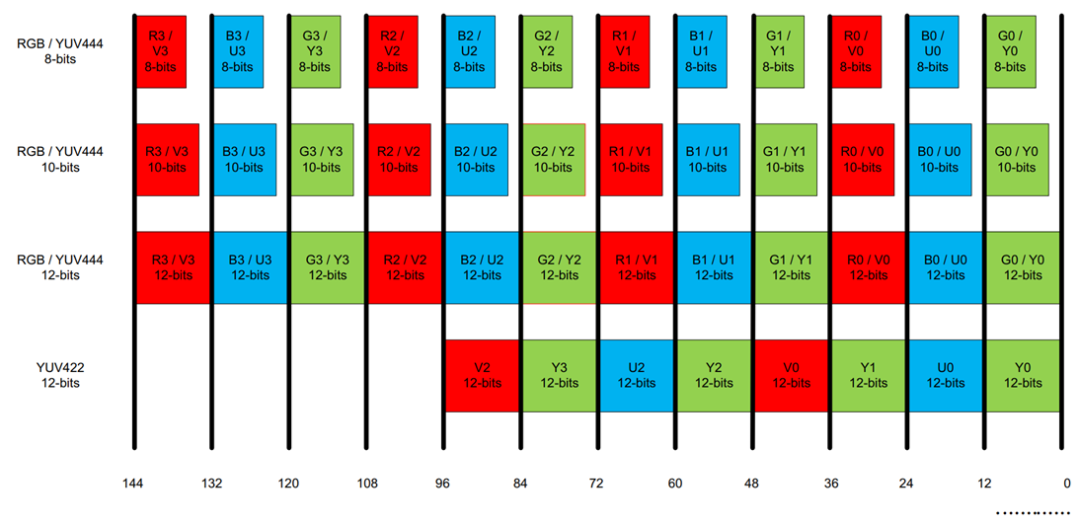

舉例來說,當每個組件的最大比特數被設置為12時,Figure 1-12 顯示了完全符合AXI4S視頻協議的每時鐘四像素數據格式。

完全兼容的每時鐘雙像素AXI4S視頻協議的數據格式如Figure 1-13所示。

Figure 1‐12: 四像素數據格式(每個分量的最大位數= 12)

Figure 1‐13:雙像素數據格式(每個組件的最大位數= 12)

當參數“每個分量的最大比特數”設置為12時,每個分量的實際比特數大于12的視頻格式將被截斷為每個分量的最大比特數。剩余的最低有效位被丟棄。如果每個器件的實際位數小于Vivado IDE中設置的每個器件的最大位數,則所有位都以MSB對齊方式傳輸,其余LSB位以0填充。這適用于所有每個組件的最大位數設置。

Table 1‐6:每個組件支持的最大位數

舉例來說,當每個組件的最大比特數被設置為12時,Figure 1-14 顯示了完全符合AXI4S視頻協議的每時鐘四像素數據格式。完全兼容的每時鐘雙像素AXI4S視頻協議的數據格式如Figure 1-15所示。

Figure 1‐14: 四像素數據格式(每個分量的最大位數= 12)

Figure 1‐15:雙像素數據格式(每個組件的最大位數= 12)

視頻接口還可以傳輸YUV420色彩空間中的四像素和雙像素。

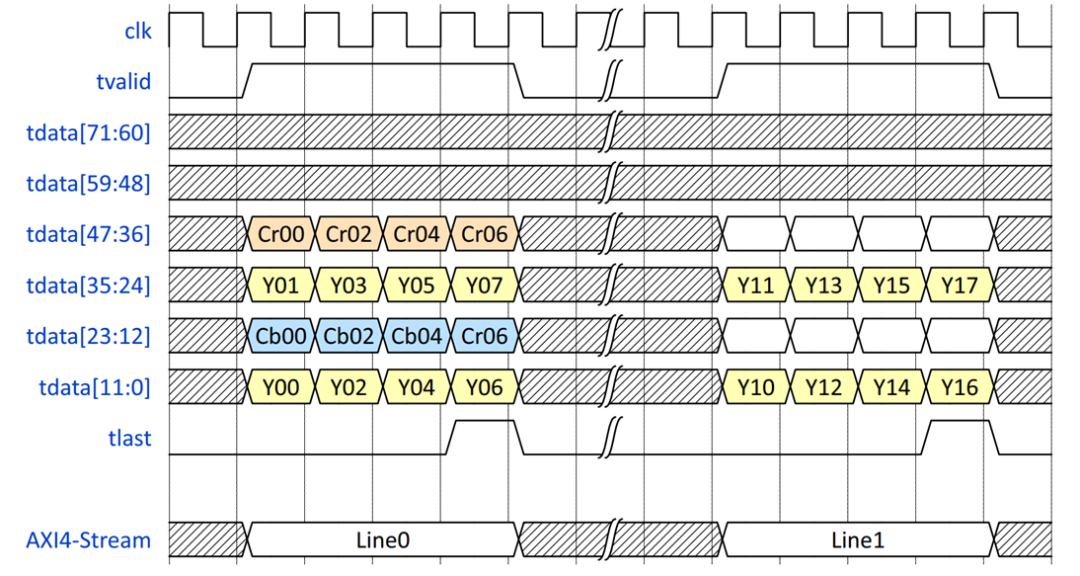

類似地,對于YUV 40深色(10、12或16位),數據表示是相同的。唯一的區別是每個組件攜帶更多的位(10、12和16)。當使用AXI4-Stream傳輸時,數據表示需要符合UG934中定義的協議。借助重新映射功能,相同的原生視頻數據將被轉換為AXI4S格式,如Figure 1-16所示。40格式在42格式的基礎上增加了垂直子采樣,這是通過省略每隔一行的色度數據在AXI4-Stream上的視頻中實現的。

Figure 1‐16: YUV 40 AXIS流視頻數據(每時鐘雙像素)

注意:對于RGB/YUV444/YUV422,視頻數據直接從AXI4S映射到原生視頻接口,沒有任何行緩沖。因此,Figure 1-12 到Figure 1-15 通常表示AXI4S和本地視頻的數據接口。圖中省略了控制信號。

該子系統利用配置參數、每個元件的最大位數和每個時鐘的像素數,提供了構建系統的充分靈活性。設置這些參數,以便目標設備支持視頻時鐘和鏈路時鐘。例如,當選擇每時鐘雙像素時,與每時鐘四像素設計相比,AXI4S視頻需要以更高的時鐘速率運行。在這種情況下,系統更難滿足定時要求。因此,對于旨在發送更高視頻分辨率的設計,建議使用每時鐘四像素數據映射。

某些視頻分辨率(例如720p60)的水平定時參數(1650)不是4的倍數。在這種情況下,必須選擇每時鐘雙像素數據映射。

審核編輯:郭婷

-

連接器

+關注

關注

98文章

14493瀏覽量

136468 -

接口

+關注

關注

33文章

8582瀏覽量

151075

原文標題:1.2 數據格式

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HDMI接口如何實現4K視頻傳輸

芯驛電子 ALINX 推出全新 IP 核產品線,覆蓋 TCP/UDP/NVMe AXI IP 核

使用dp接口播放4K視頻的技巧

AMBA AXI4接口協議概述

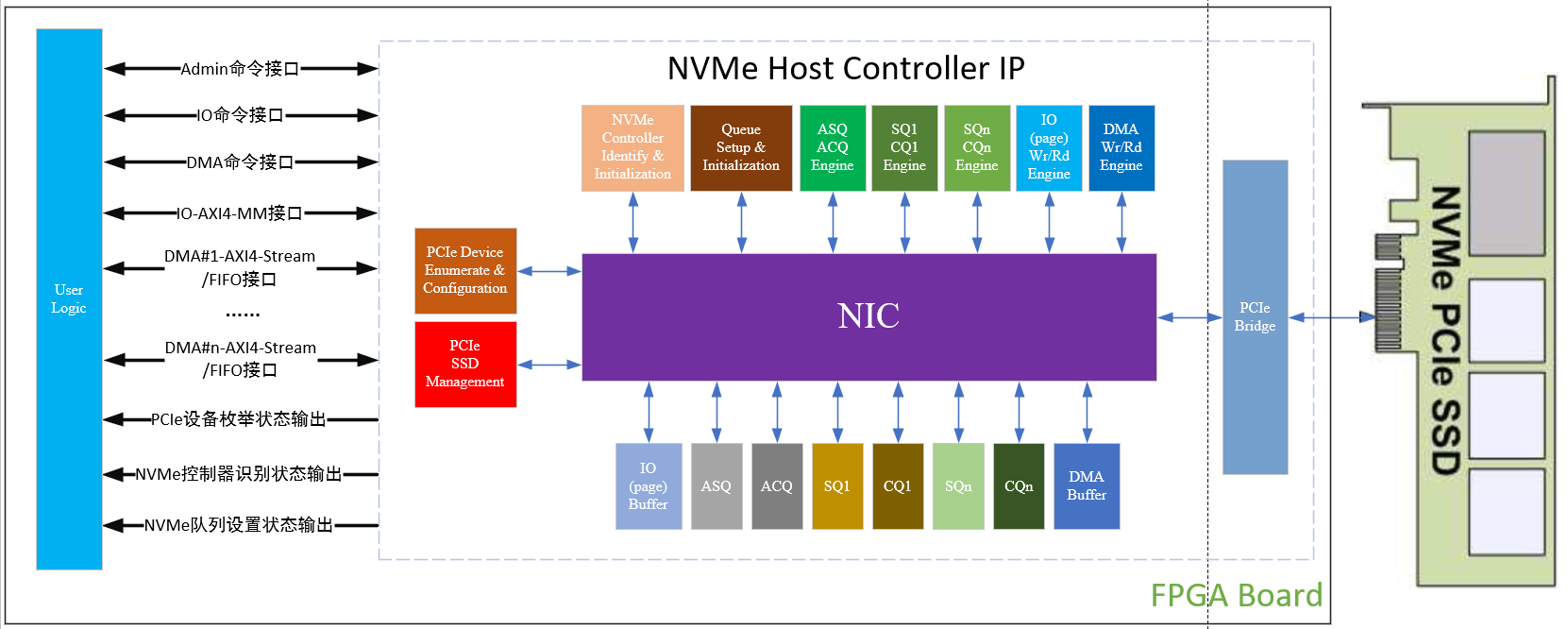

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

基于TI Sitara系列AM5728工業開發板——FPGA視頻開發案例分享

SoC設計中總線協議AXI4與AXI3的主要區別詳解

8路SDI/HDMI/MIPI/PCIe-DMA音視頻采集,V4L2驅動應用介紹

Xilinx FPGA NVMe主機控制器IP,高性能版本介紹應用

Xilinx FPGA 1/4/8通道PCIe-DMA控制器IP,高性能應用介紹

PCIe-AXI-Cont用戶手冊

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

漫談AMBA總線-AXI4協議的基本介紹

使用AXI4S接口的視頻IP細節介紹

使用AXI4S接口的視頻IP細節介紹

評論