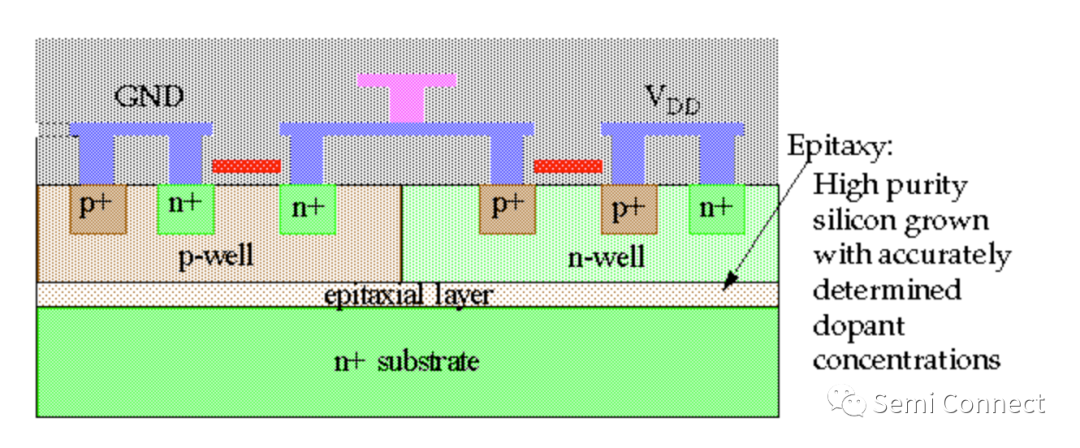

CMOS集成電路的基礎工藝之一就是雙阱工藝,它包括兩個區域,即n-MOS和p-MOS 有源區,分別對應p阱和N阱,如圖所示。

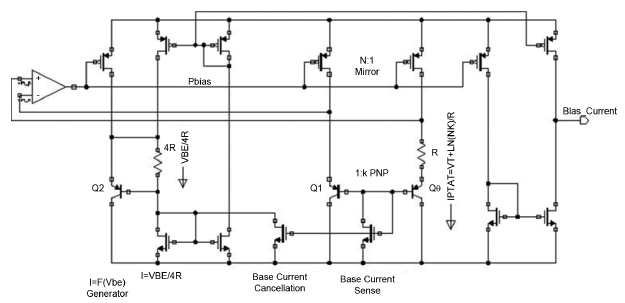

在進行阱注入時,產業內的主流技術多數采用倒摻雜技術來調節晶體管的電學特性,即首先采用高能量、大劑量的離子注入,注入的深度約為 1um,注入區域與阱相同,隨后通過大幅降低注入能量及劑量,控制注入深度和摻雜剖面。阱的注入摻雜不僅可以調節晶體管的閾值電壓,也可以解決CMOS 電路常見的一些問題,如閂鎖效應和其他可靠性問題。

雙阱 CMOS 工藝是當前集成電路的標準工藝之一,它最初是在 n-MOS工藝和 p-MOS 工藝的基礎上發展起來的。

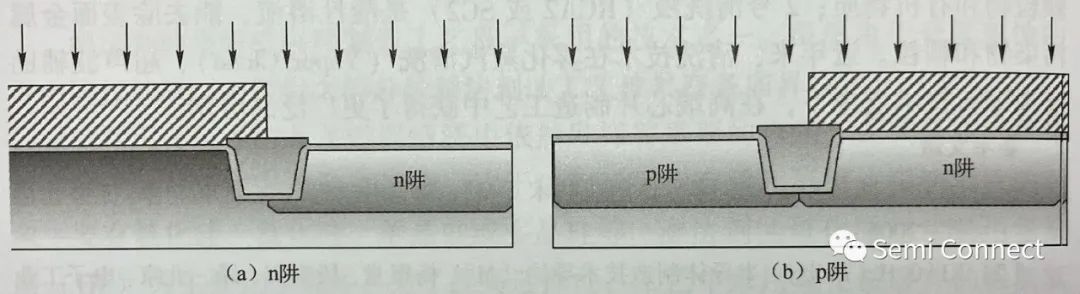

早期的雙阱 CMOS 工藝沒有高能量大劑量的注入,只是用中能量和中劑量離子注入n阱和p阱的區域,然后熱退火形成獨立的n阱和p阱。

隨著離子注入技術的發展,高能量大劑量的注入不再成為離子注入的難題,并且高能量大劑量的注入形成的倒置阱效果很明顯,所以才逐步形成現在的標準雙阱工藝。

雙阱工藝常見的基本制造步驟是先制作n阱,包括犧牲氧化層生長,n阱區域光刻,n阱注入,然后退火;p阱的形成與其類似。

確定雙阱工藝的基本條件是確保器件電學特性滿足要求,包括阱之間的擊穿電壓、有效的電學隔離、避免閂鎖效應、合適的閾值電壓等。

另外,襯底材料的摻雜情況也對阱的形成條件有很大影響。

審核編輯:劉清

-

集成電路

+關注

關注

5409文章

11771瀏覽量

365303 -

CMOS

+關注

關注

58文章

5844瀏覽量

237049 -

晶體管

+關注

關注

77文章

9875瀏覽量

139744

原文標題:模塊工藝——雙阱工藝(Twin-well or Dual-Well)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CMOS集成電路的基本制造工藝

CMOS集成電路使用時的技術要求

怎么采用標準CMOS工藝設計RF集成電路?

集成電路與MCU簡析

混合集成電路CMOS工藝中LowDose率對寄生雙極結構的影響分析概述

評論