大多數FPGA技術都無法滿足關鍵任務設計要求,但基于防熔斷器的架構取得了成功,提供了抗輻射性和設計安全性等基本屬性。

當今的高密度 FPGA 為設計人員提供了快速創建定制組件的機會,以實現最佳性能和任務關鍵型系統的快速部署。但對于軍事和航空航天應用,眾所周知,基于存儲器的FPGA技術無法滿足幾個重要要求,包括抗輻射性和設計安全性。防熔斷器FPGA技術成功地滿足了這些要求,將可編程邏輯的優勢帶到關鍵任務系統設計中。

許多開發人員明白,任務關鍵型系統必須設計為在極端環境條件下可靠運行,但發現大多數FPGA技術都難以滿足這些需求。此外,在確定設備是否適合大多數FPGA技術不足的關鍵任務服務時,還有其他要求同樣重要。我們的討論將集中在其他三個關鍵要求上:非易失性配置、輻射環境中的可靠運行和設計安全性(表1)。

表1

影響關鍵應用的三個因素

對非易失性配置的要求源于關鍵任務軍用航空應用中電源中斷的高概率。在維護或維修期間更換帶電系統組件、從線路電源切換到電池電源時的失誤以及掉電都可能觸發系統從電源中斷中恢復的需要。非易失性系統配置簡化了恢復過程,無需重新加載系統設置和參數。這使得系統恢復比必須重新加載配置時更快、更不容易出錯,從而提高了系統可用性以執行其任務。

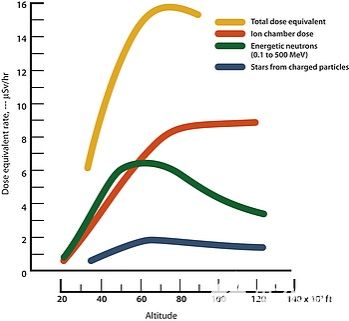

此外,隨著冷戰的結束,對軍用航空系統在輻射環境中運行的需求已經從普遍意識中消失了。然而,這一要求不僅僅來自在核事件中幸存下來的需要。即使在日常操作中,關鍵任務系統也可能暴露在高輻射水平下。輻射以宇宙射線和太陽風的形式出現,以及這些來源在高海拔地區產生的高能二次粒子(見圖1[1])。

圖1

雖然輻射通量通常不足以損壞半導體器件,但它確實會對系統運行產生影響。輻射的典型效應是單事件翻轉(SEU):一種能夠改變存儲單元位值的局部能量尖峰。如果這種變化發生在FPGA內的關鍵位置,可能會對系統運行造成嚴重破壞。

設計安全性是關鍵任務系統設計的第三個要求,特別是軍事系統。如果設計不安全,敵人可以通過逆向工程和克隆捕獲的設備供自己使用來迅速消除此類設計提供的任何技術優勢。系統還可能嵌入敏感信息,例如密碼、加密密鑰和跳頻算法。從捕獲的系統中提取此類信息將允許敵人制造能夠攔截和解釋編碼通信或生成模仿信號以混淆指揮和控制活動的設備。進行逆向工程困難、昂貴且耗時的設計可以通過延遲結果直到它們不再有用來防止這種妥協。

比較 FPGA 技術

在利用FPGA技術開發關鍵任務系統時,這些被忽視的設計要求尤為重要。使用 FPGA 器件可為開發人員提供與使用 ASIC 相當的設計靈活性和集成度,但成本要低得多,并且可用性更即時。然而,并非每種FPGA技術都適合任務關鍵型設計的需求。

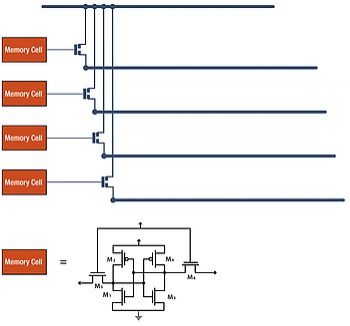

例如,許多FPGA未能滿足非易失性要求,因為它們以SRAM為基礎。這些 FPGA 中的內部邏輯連接依賴于 SRAM 單元來保持開關晶體管的打開或關閉(圖 2)。因此,存儲在存儲器中的數據決定了FPGA的配置,但SRAM單元在斷電時將丟失其數據。

圖2

基于 SRAM 的 FPGA 需要在上電時接收配置數據,以便為系統運行做好準備。典型的方法是采用小型外部非易失性存儲器源(如串行EEPROM)來保存配置數據。上電后,FPGA從EEPROM檢索數據并自行配置工作。根據存儲器的大小和FPGA可以檢索數據的時鐘速率,FPGA可能需要上電后幾百毫秒才能準備好使用。系統的其余部分必須等到FPGA準備就緒才能完全運行。

可編程邏輯的SRAM方法也有幾個不幸的設計屬性。一是每個連接點所需的電路相當大,需要多個晶體管來形成SRAM單元,導致互連密度降低。開關晶體管的互連電容增加了FPGA的動態功耗,增加了結溫并降低了器件可靠性,即使不計時,大存儲單元的漏電流也會浪費功率。

一種非易失性可編程邏輯方法具有類似的開關結構,但使用EEPROM單元而不是SRAM來保持配置。這種方法解決了波動性問題,但仍與基于SRAM的FPGA共享許多其他屬性。該架構仍然要求在每個連接點安裝一個開關晶體管,從而限制了通過連接的互連密度和信號速度。

EEPROM單元的工作原理是在浮動柵極上保持電荷,以保持開關晶體管的打開或關閉。當高壓編程信號通過穿過氧化層將電子驅動到柵極上或離開柵極時,浮動柵極接收或失去其電荷。在正常工作中,柵極沒有可用的放電路徑,因此使得FPGA配置是非易失性的。

提供非易失性的另一種方法是使用防熔斷技術。防保險絲是FPGA中每個可配置電路結處的非晶硅過孔。未經編程,過孔是絕緣體,在該站點沒有連接。通過對其施加高壓來編程過孔,將其狀態更改為導體,從而在該站點進行連接。因此,過孔的物理狀態與FPGA的配置保持一致。狀態變化是永久性的,使防熔斷器FPGA非易失性。由于沒有晶體管參與維持邏輯連接,因此互連密度高且沒有漏電流。互連電容低,降低了動態功耗。

解決輻射問題

除了波動性問題之外,在輻射環境中工作的需求是對基于存儲器的FPGA技術的第二次打擊。通過有源半導體器件的高能粒子在硅中產生臨時電離路徑。這些通路可以短暫地短路晶體管,產生稱為SEU的瞬態脈沖。

在SRAM中,SEU可以反轉單個位的狀態,然后存儲器電路將保持該狀態。在EEPROM中,SEU可能會對浮動柵極放電,從而導致永久性的位變化。雖然處理器應用中使用的存儲器通常包括糾錯和檢測來處理此類事件,但FPGA的配置存儲器沒有這種保護。因此,SEU 可以在基于存儲器的 FPGA 中引入持久的邏輯更改。

反保險絲FPGA沒有這樣的漏洞。SEU的能量不足以對過孔進行編程,瞬態脈沖對邏輯沒有顯著影響。在NASA/戈達德進行的測試表明,在輻射能量高達193 MeV的反保險絲FPGA操作中沒有錯誤,而存儲設備開始出現低至100 MeV的位錯誤。

防熔絲 FPGA 還比基于存儲器的 FPGA 更有效地解決設計安全性問題。要完整表征編程的FPGA,需要兩條信息:配置細節和底層結構。配置細節在基于存儲器的FPGA中最容易捕獲。對于實時系統,無源探測可以在配置期間移動到基于 SRAM 的 FPGA 時捕獲編程數據。電子探測可以確定電路處于活動狀態時EEPROM構型電池的電荷狀態。這兩種方法的執行速度都相對較快,實施成本也很低。

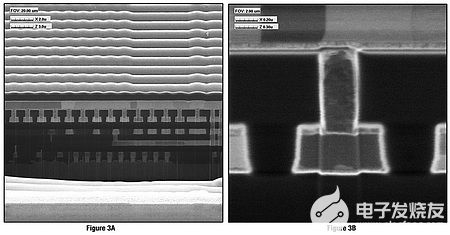

確定FPGA的邏輯結構需要更多的努力,但逆向工程方法可以提取器件的設計細節,價格低于10萬美元。方法是使用等離子體(用于鈍化和氧化層)或化學(用于金屬層)蝕刻剝離邏輯器件的每一層,一次一層,然后在顯示每一層時拍攝高分辨率照片(圖 3)。這些照片可以重建用于制造設備的掩模組。然后,這允許分析甚至克隆設備。

圖 3:3A 和 3B

然而,研究反熔斷器FPGA的編程需要更精細的措施。這部分是因為可編程元件位于多層結構中,因此表面掃描無效。此外,沒有信號或存儲電荷進行探測;程序存儲是影響電阻的結構變化,而不是電荷的積累。

只有體檢才能顯示反引信的編程狀態,剝層法不會有效工作。反引信中改變區域的橫截面太小,無法從上方觀察,因此可靠地看到結構的唯一方法是從側面(再次參見圖 3)。獲得此視圖需要使用聚焦離子束 (FIB) 在設備中創建溝槽,然后銑削邊緣以逐步擴展溝槽。在每一步拍攝照片可以創建電路的3D圖像。然而,這個過程需要昂貴的設備,而且在不知道去哪里尋找的情況下非常耗時。即使有先見之明,需要檢查的反引信數量也使這項任務變得不切實際。對編程反熔絲FPGA(如QuickLogic的QL1P075和QL1P100‘?ì)進行逆向工程所需的時間實際上使它們絕對安全。

防熔斷器滿足關鍵任務需求

軍用航空應用的設計安全需求,以及耐輻射性和非易失性,在文獻中經常被忽視,但設計人員也不容忽視。在尋求FPGA在設計中的優勢時,開發人員習慣性地尋找能夠解決mil temp操作的器件,但他們也應該考慮基礎技術滿足上述需求的能力。在FPGA技術中,反熔斷器可編程性是唯一滿足關鍵任務設計所有要求的技術。

審核編輯:郭婷

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603049 -

存儲器

+關注

關注

38文章

7484瀏覽量

163776 -

sram

+關注

關注

6文章

767瀏覽量

114677

發布評論請先 登錄

相關推薦

FPGA如何消除時鐘抖動

FPGA設計面臨的挑戰和解決方案

FPGA學習筆記-電源電壓

羅德與施瓦茨測試解決方案助力向寬帶關鍵任務通信成功遷移

鴻蒙OS開發實例:【ArkTS類庫多線程CPU密集型任務TaskPool】

鴻蒙OS開發實例:【ArkTS類庫多線程I/O密集型任務開發】

面向任務關鍵型應用的FPGA

面向任務關鍵型應用的FPGA

評論