低噪聲儀表放大器AD8428提供2000 精確增益,具備解決這些問題所必須的一切特性。AD8428 具有5 ppm/°C最大增益漂移、0.3 μV/°C最大失調電壓漂移、140 dB最小CMRR至60 Hz(120 dB最小值至50 kHz)、130 dB最小PSRR和3.5 MHz帶寬,適合低電平測量系統。引人注目的是該器件的1.3 nV/ Hz電壓噪聲(1 kHz)和40 nV p-p噪聲(0.1 Hz至10 Hz)性能,在極小信號下具有高信噪比。兩個額外的引腳可讓設計人員改變增益或增加濾波器來降低噪聲帶寬。這些濾波器引腳還提供了降低噪聲的獨特方法。

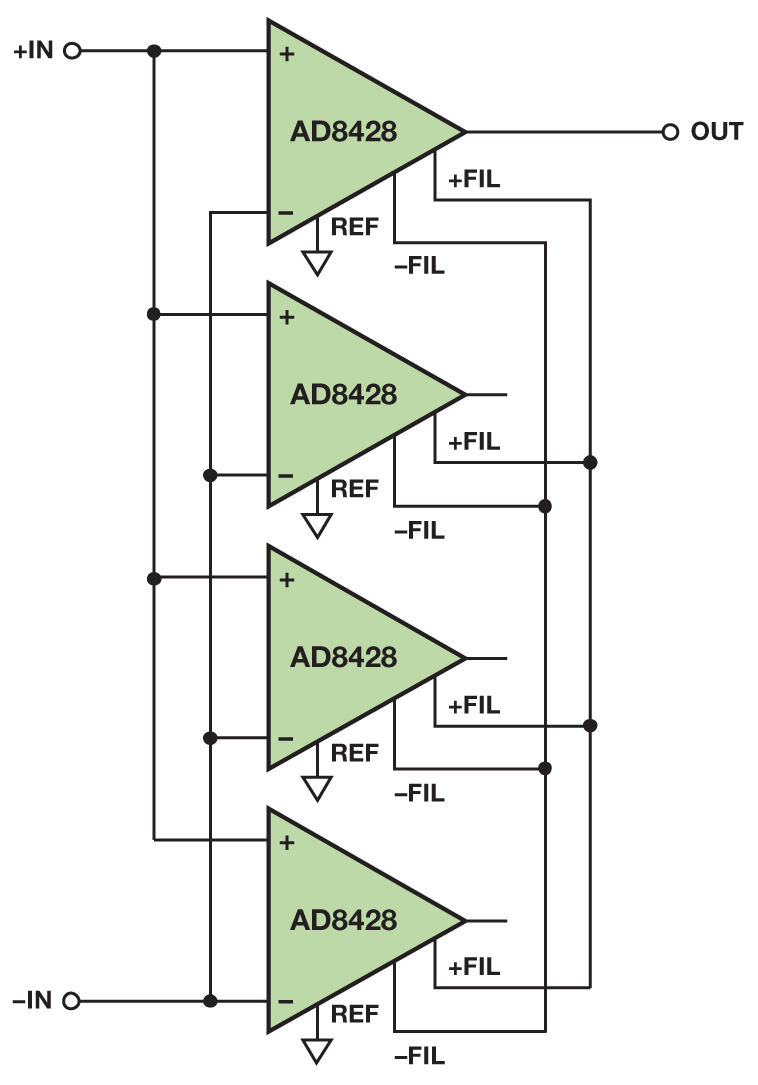

圖1 顯示的電路配置可進一步降低系統噪聲。四個AD8428 的輸入和濾波引腳互相短接,降低噪聲至原來的二分之一。可以使用任意一個儀表放大器的輸出來保持低輸出阻抗。此電路可以擴展從而降低噪聲,降低的倍數為所用放大器數的平方根。

圖1. 使用四個AD8428 儀表放大器的降噪電路

每一個AD8428 產生1.3 nV/ Hz折合到輸入(RTI)的典型頻譜噪聲,該噪聲與其他放大器產生的噪聲不相關。不相關的噪聲源以方和根(RSS)的方式疊加到濾波器引腳。另一方面,輸入信號為正相關。每一個AD8428 都響應信號在濾波器引腳上生成相同的電壓,因此連接多個AD8428 不會改變電壓,增益保持為2000。

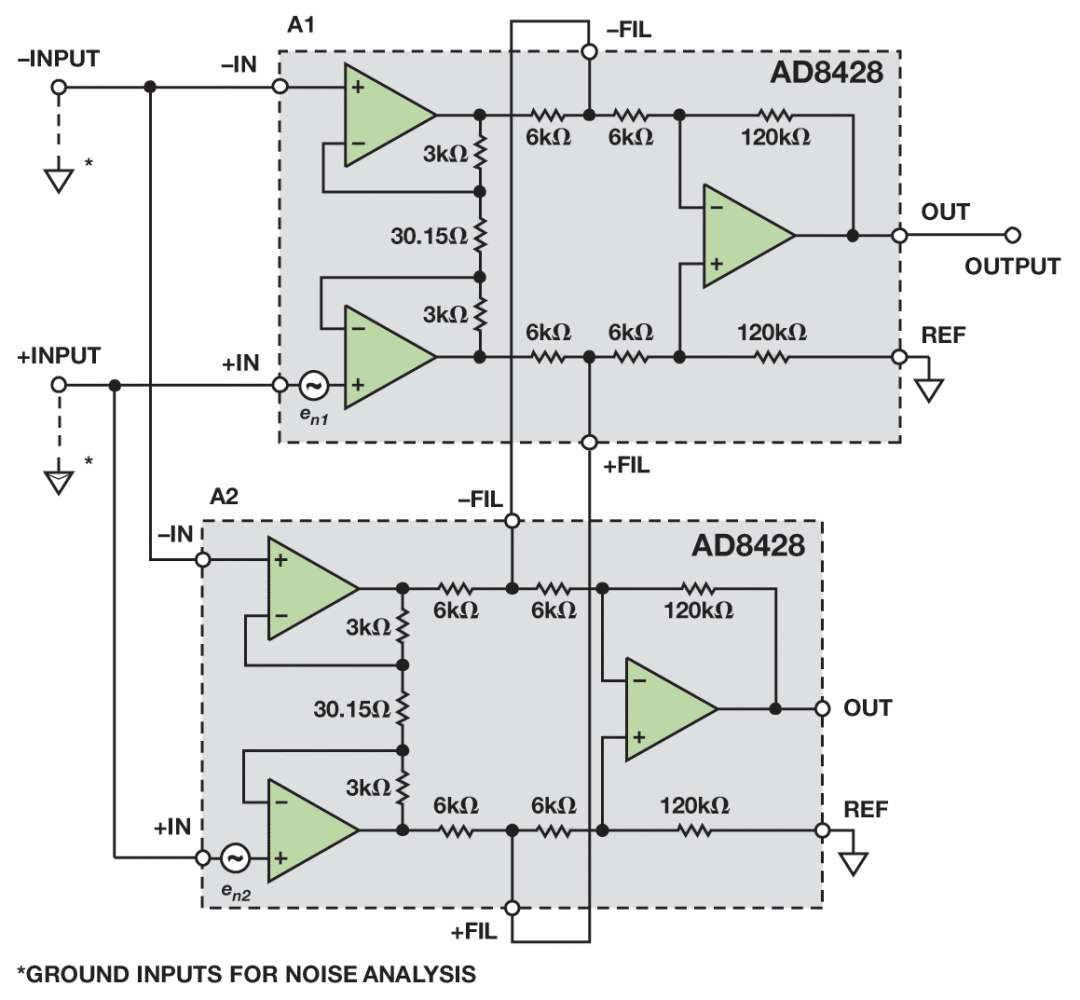

針對圖2電路簡化版本的分析表明,將兩個AD8428以此方式連接可以降低噪聲,降低的倍數為2。每一個AD8428的噪聲都可以在+IN引腳上建模。為了確定總噪聲,可以將輸入接地,并使用疊加來組合噪聲源。

噪聲源en1經200差分增益放大,并到達前置放大器A1的輸出端。就這部分的分析而言,輸入接地時,前置放大器A2的輸出端無噪聲。前置放大器A1每個輸出端與相應前置放大器A2輸出端之間的6 kΩ/6 kΩ電阻分頻器可以采用戴維寧等效電路替代:前置放大器A1輸出端噪聲電壓的一半以及一個3 kΩ串聯電阻。這部分就是降低噪聲的機制。完整的節點分析表明,響應en1的輸出電壓為1000 × en1。由于對稱,因此響應噪聲電壓en2的輸出電壓為1000 × en2。en1和en2幅度都等于en,并且將作為RSS疊加,導致總輸出噪聲為1414 × en。

圖2. 噪聲分析簡化電路模型

為了將其折合回輸入端,就必須驗證增益。假設在+INPUT和–INPUT之間施加差分信號VIN。A1第一級輸出端的差分電壓等于VIN × 200。同樣的電壓出現在前置放大器A2的輸出端,因此沒有分頻信號進入6 kΩ/6 kΩ分頻器,并且節點分析表明輸出為VIN × 2000。因此,總電壓噪聲RTI為en× 1414/2000,等效于en/2。使用AD8428的1.3 nV/Hz典型噪聲密度,則兩個放大器配置所產生的噪聲密度約為0.92 nV/Hz。

使用額外的放大器之后,濾波器引腳處的阻抗發生改變,進一步降低噪聲。例如,如圖1所示使用四個AD8428,則前置放大器輸出端到濾波器引腳之間的6 kΩ電阻后接三個6 kΩ電阻,分別連接每一個無噪聲前置放大器的輸出端。這樣便有效地創建了6 kΩ/2 kΩ電阻分頻器,將噪聲進行四分頻處理。因此,正如預測的那樣,四個放大器的總噪聲便等于en/2。

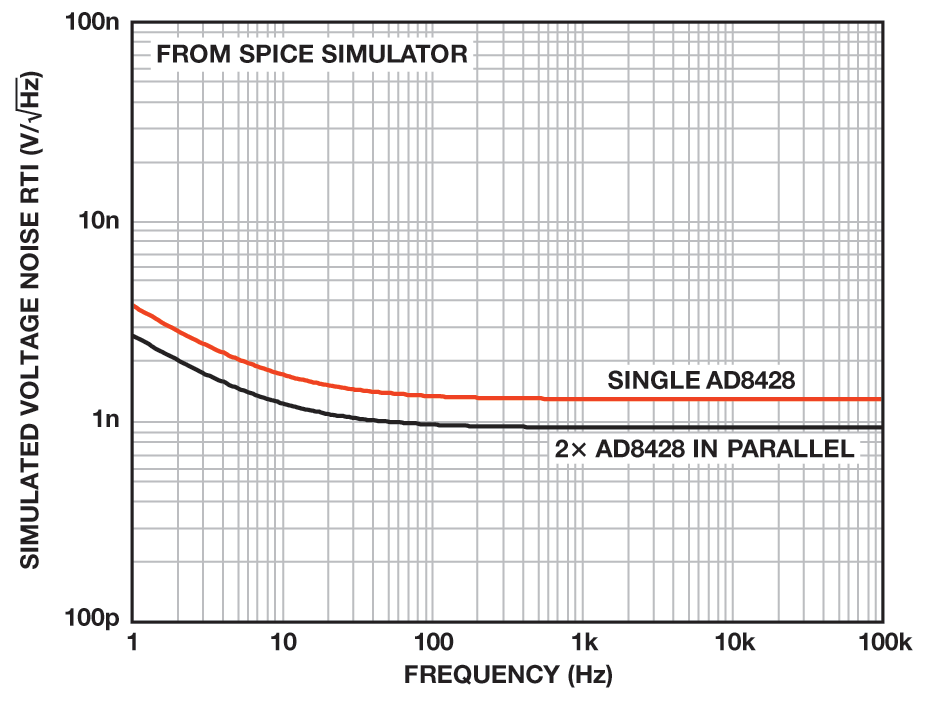

SPICE電路仿真雖然不能代替原型制作,但作為驗證此類電路構想的第一步很有用。若要驗證此電路,可以使用ADIsimPE仿真器和AD8428 SPICE宏模型仿真兩個器件并聯時的電路性能。圖3中的仿真結果表明該電路的表現與預期一致:增益為2000,噪聲降低30%。

圖3. SPICE仿真結果

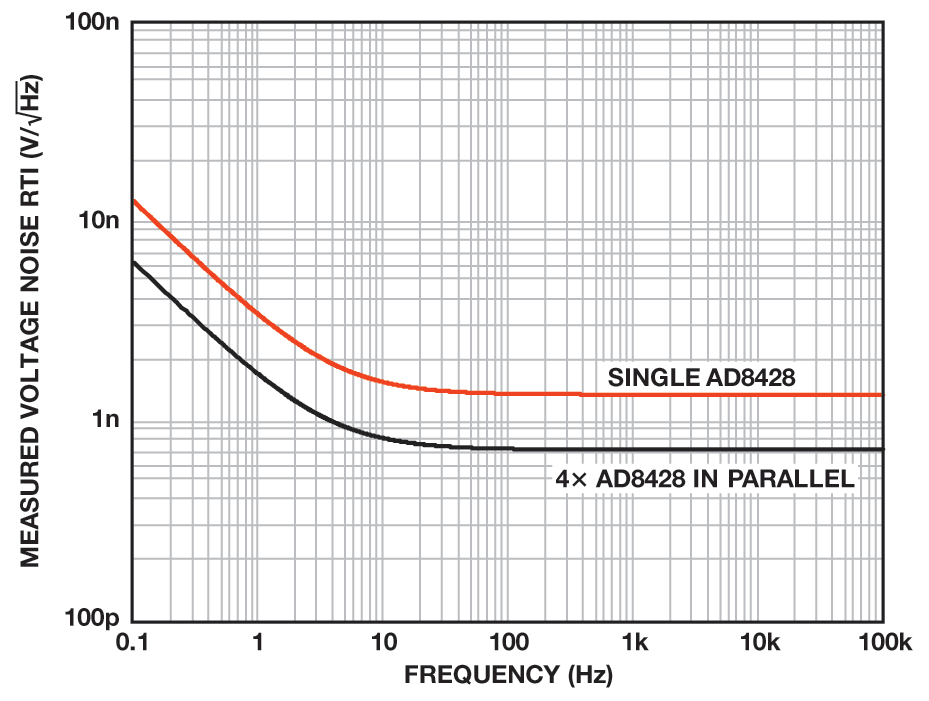

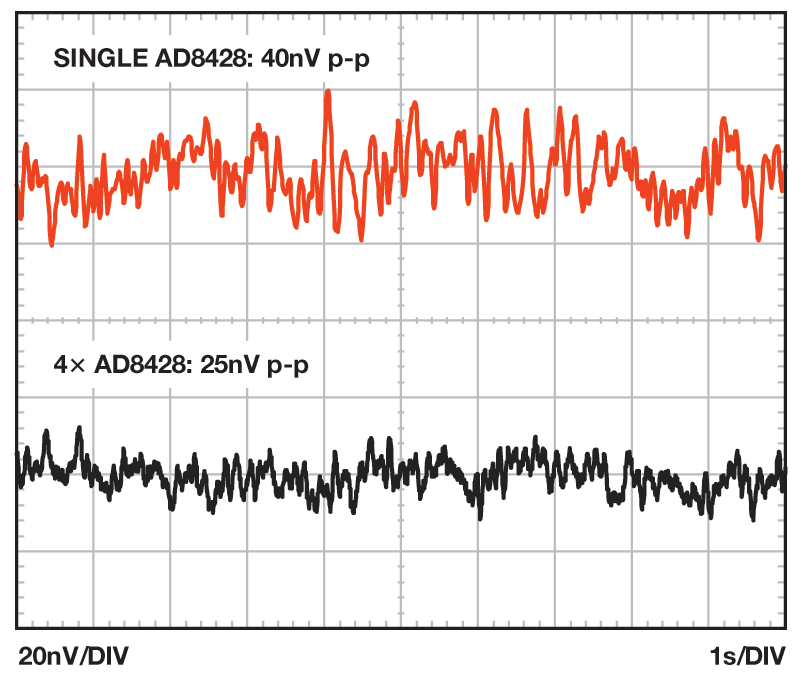

在工作臺上測量四個AD8428組成的完整電路。測得的RTI噪聲頻譜密度為0.7 nV/Hz (1 kHz),0.1 Hz至10 Hz范圍內具有25 nV p-p。這比很多納伏電壓表的噪聲都要更低。測得的噪聲頻譜和峰峰值噪聲分別如圖4和圖5所示。

圖4. 圖1中電路的電壓噪聲頻譜測量值

圖5. 圖1中電路測得的0.1 Hz至10 Hz RTI噪聲

原文標題:納伏級靈敏度的低噪聲儀表放大器這樣構建!

文章出處:【微信公眾號:亞德諾半導體】歡迎添加關注!文章轉載請注明出處。

-

亞德諾

+關注

關注

6文章

4680瀏覽量

16199

原文標題:納伏級靈敏度的低噪聲儀表放大器這樣構建!

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ALN4000-10-3530毫米波低噪聲放大器WENTEQ

CHA3218-99F低噪聲放大器適合5G通信嗎?

儀表放大器原理和作用

儀表放大器型號和功能有哪些

低噪聲放大器的原理和參數是什么 前置微小信號放大器

評論