時(shí)序分析是FPGA設(shè)計(jì)中永恒的話(huà)題,也是FPGA開(kāi)發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來(lái),先介紹時(shí)序分析中的一些基本概念。

時(shí)鐘的時(shí)序特性主要分為抖動(dòng)(Jitter)、偏移(Skew)、占空比失真(Duty Cycle Distortion)3點(diǎn)。對(duì)于低速設(shè)計(jì),基本不用考慮這些特征;對(duì)于高速設(shè)計(jì),由于時(shí)鐘本身的原因造成的時(shí)序問(wèn)題很普遍,因此必須關(guān)注。

時(shí)鐘抖動(dòng) (clock jitter)

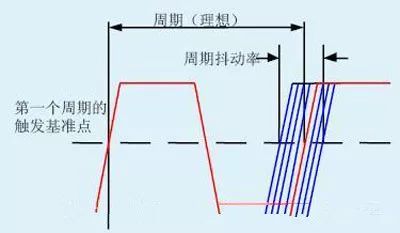

理想的時(shí)鐘信號(hào)應(yīng)該是理想的方波,但是現(xiàn)實(shí)中的時(shí)鐘的邊沿變化不可能是瞬變的,它有個(gè)從低到高 / 從高到低的變化過(guò)程,如下圖所示。

常見(jiàn)的抖動(dòng)參數(shù)有3種:

周期抖動(dòng)(Period Jitter):周期抖動(dòng)率(Period Jitter)測(cè)量時(shí)鐘輸出傳輸偏離其理想位置的最大偏離。Period Jitter代表周期差抖動(dòng)的上下邊界。

周期差抖動(dòng)(cycle-to-cycle Jitter):周期差抖動(dòng)率(cycle-to-cycle jitter)是兩個(gè)相鄰周期的時(shí)間偏差。它總是小于周期抖動(dòng)(period jitter)

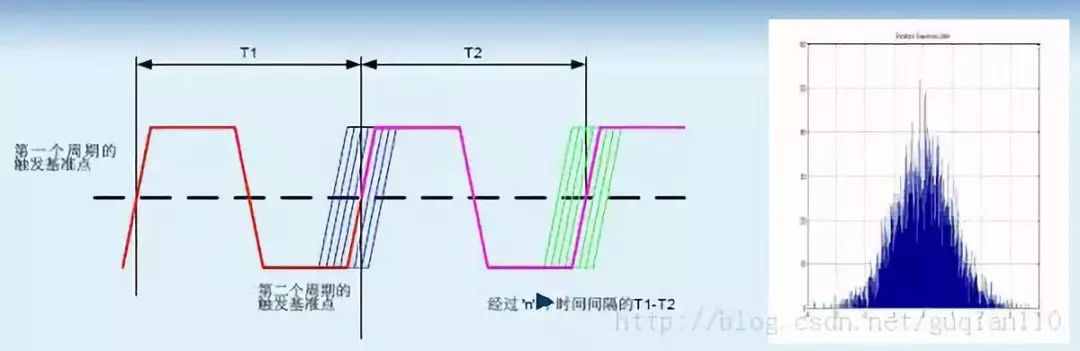

長(zhǎng)期抖動(dòng)(Long-term Jitter):長(zhǎng)期抖動(dòng)率如下圖(Long-Term Jitter)定義為一個(gè)時(shí)鐘沿相對(duì)于基準(zhǔn)周期時(shí)鐘沿經(jīng)過(guò)一段時(shí)間的延時(shí)之后,與其理想位置的偏離。此測(cè)量可以捕獲鎖相環(huán)低頻周期變化(緩慢的,頻率很低的)。長(zhǎng)期抖動(dòng)對(duì)圖形、串行連接通訊系統(tǒng)、打印機(jī)和任何光柵掃描操作非常重要。

時(shí)鐘抖動(dòng)的原因就是噪聲。時(shí)鐘抖動(dòng)是永遠(yuǎn)存在的,當(dāng)其大到可以和時(shí)鐘周期相比擬的時(shí)候,會(huì)影響到設(shè)計(jì),這樣的抖動(dòng)是不可接受的。

時(shí)鐘偏斜 (clock skew)

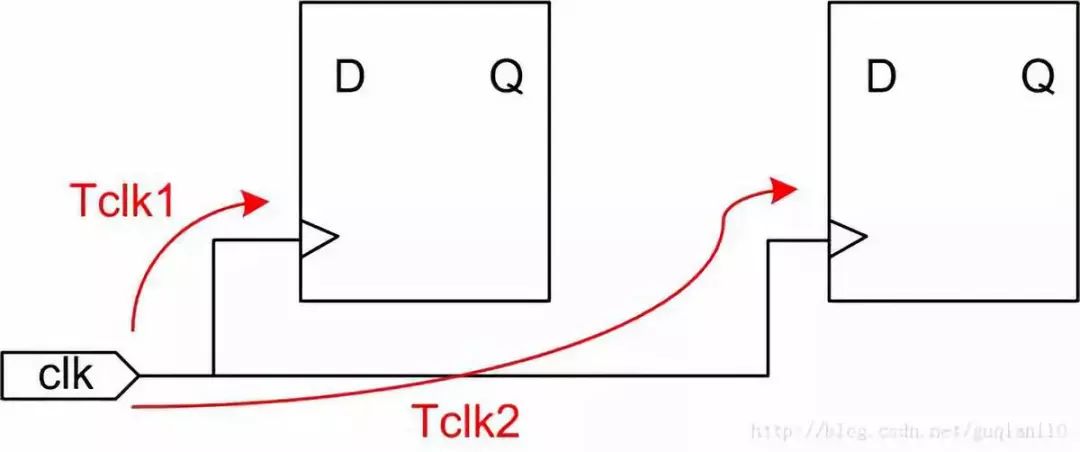

時(shí)鐘信號(hào)要提供給整個(gè)電路的時(shí)序單元,所以時(shí)鐘信號(hào)線(xiàn)非常長(zhǎng),并構(gòu)成分布式的RC網(wǎng)路。它的延時(shí)與時(shí)鐘線(xiàn)的長(zhǎng)度、時(shí)序單元的負(fù)載電容、個(gè)數(shù)有關(guān),所以產(chǎn)生所謂的時(shí)鐘偏移。時(shí)鐘偏移是指同一個(gè)時(shí)鐘信號(hào)到達(dá)兩個(gè)不同的寄存器之間的時(shí)間差值,根據(jù)差值可以分為正偏移和負(fù)偏移。

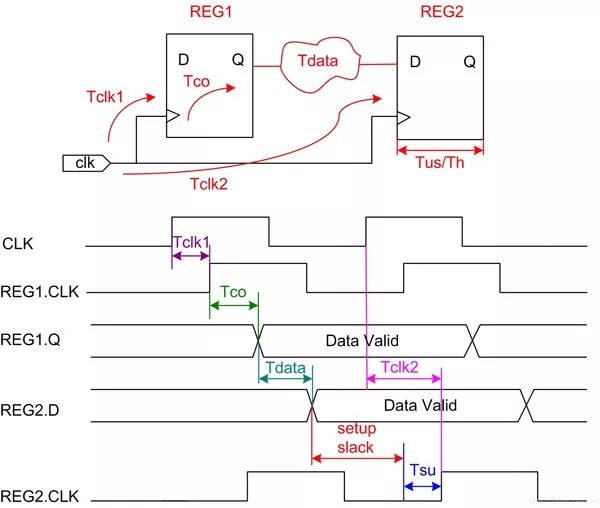

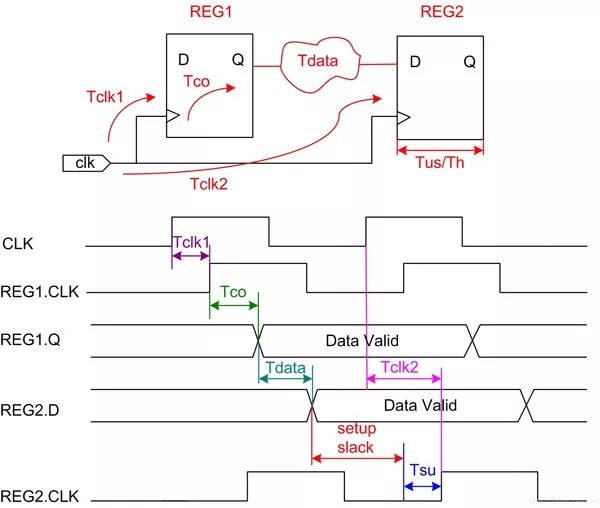

時(shí)鐘偏移的計(jì)算公式:Tskew = Tclk2 - Tclk1

時(shí)鐘偏移是永遠(yuǎn)存在的,當(dāng)其大到一定程度會(huì)影響電路的時(shí)序。解決方法就是在FPGA的設(shè)計(jì)中讓主要的時(shí)鐘信號(hào)走全局時(shí)鐘網(wǎng)絡(luò)。該網(wǎng)絡(luò)采用全銅工藝和樹(shù)狀結(jié)構(gòu),并設(shè)計(jì)了專(zhuān)用時(shí)鐘緩沖和驅(qū)動(dòng)網(wǎng)絡(luò),到所有的IO單元、CLB和塊RAM的偏移非常小,可以忽略不計(jì)。

占空比失真DCD (Duty Cycle Distortion)

即時(shí)鐘不對(duì)稱(chēng),時(shí)鐘的脈沖寬度發(fā)生了變化。DCD會(huì)吞噬大量的時(shí)序裕量,造成數(shù)字信號(hào)的失真,使過(guò)零區(qū)間偏離理想的位置。DCD通常是由信號(hào)的上升沿和下降沿之間時(shí)序不同而造成的。

信號(hào)扇入/扇出 (fan-in/fan-out)

扇出(fan-out)是定義單個(gè)邏輯門(mén)能夠驅(qū)動(dòng)的數(shù)字信號(hào)輸入最大量的術(shù)語(yǔ)。大多數(shù)TTL邏輯門(mén)能夠?yàn)?0個(gè)其他數(shù)字門(mén)或驅(qū)動(dòng)器提供信號(hào)。因而,一個(gè)典型的TTL邏輯門(mén)有10個(gè)扇出信號(hào)。

在一些數(shù)字系統(tǒng)中,必須有一個(gè)單一的TTL邏輯門(mén)來(lái)驅(qū)動(dòng)10個(gè)以上的其他門(mén)或驅(qū)動(dòng)器。這種情況下,被稱(chēng)為緩沖器(buf)的驅(qū)動(dòng)器可以用在TTL邏輯門(mén)與它必須驅(qū)動(dòng)的多重驅(qū)動(dòng)器之間。這種類(lèi)型的緩沖器有25至30個(gè)扇出信號(hào)。邏輯反向器(也被稱(chēng)為非門(mén))在大多數(shù)數(shù)字電路中能夠輔助這一功能。

模塊的扇出是指模塊的直屬下層模塊的個(gè)數(shù)。一般認(rèn)為,設(shè)計(jì)得好的系統(tǒng)平均扇出是3或4。一個(gè)模塊的扇出數(shù)過(guò)大或過(guò)小都不理想,過(guò)大比過(guò)小更嚴(yán)重。一般認(rèn)為扇出的上限不超過(guò)7。扇出過(guò)大意味著管理模塊過(guò)于復(fù)雜,需要控制和協(xié)調(diào)過(guò)多的下級(jí)。解決的辦法是適當(dāng)增加中間層次。一個(gè)模塊的扇入是指有多少個(gè)上級(jí)模塊調(diào)用它。

扇人越大,表示該模塊被更多的上級(jí)模塊共享。這當(dāng)然是我們所希望的。但是不能為了獲得高扇人而不惜代價(jià),例如把彼此無(wú)關(guān)的功能湊在一起構(gòu)成一個(gè)模塊,雖然扇人數(shù)高了,但這樣的模塊內(nèi)聚程度必然低,這是我們應(yīng)避免的。設(shè)計(jì)得好的系統(tǒng),上層模塊有較高的扇出,下層模塊有較高的扇人。其結(jié)構(gòu)圖像清真寺的塔,上面尖,中間寬,下面小。

時(shí)序分析起點(diǎn)和終點(diǎn)

時(shí)序分析起點(diǎn)(launch edge):第一級(jí)寄存器數(shù)據(jù)變化的時(shí)鐘邊沿,也是靜態(tài)時(shí)序分析的起點(diǎn)。

時(shí)序分析終點(diǎn)(latch edge):數(shù)據(jù)鎖存的時(shí)鐘邊沿,也是靜態(tài)時(shí)序分析的終點(diǎn)。

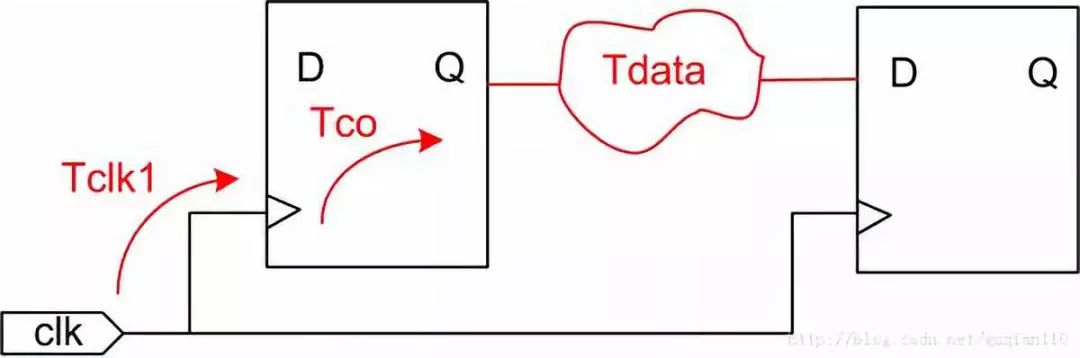

數(shù)據(jù)輸出延時(shí) (Tco)

數(shù)據(jù)輸出延時(shí)(Tco):這個(gè)時(shí)間指的是當(dāng)時(shí)鐘有效沿變化后,數(shù)據(jù)從輸入端到輸出端的最小時(shí)間間隔。

建立時(shí)間 (setup time)

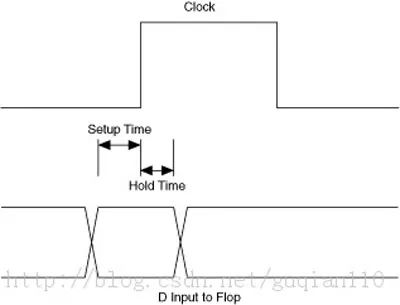

建立時(shí)間(setup time)是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的時(shí)間。輸入信號(hào)應(yīng)提前時(shí)鐘上升沿(如上升沿有效)T 時(shí)間到達(dá)芯片,這個(gè)T就是建立時(shí)間。簡(jiǎn)而言之,時(shí)鐘邊沿觸發(fā)前,要求數(shù)據(jù)必須存在一段時(shí)間,這就是器件需要的建立時(shí)間。如不滿(mǎn)足建立時(shí)間,這個(gè)數(shù)據(jù)就不能被這一時(shí)鐘打入觸發(fā)器,只有在下一個(gè)時(shí)鐘上升沿,數(shù)據(jù)才能被打入觸發(fā)器。

保持時(shí)間 (hold time)

保持時(shí)間(hold time)是指觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以后,數(shù)據(jù)穩(wěn)定不變的時(shí)間。簡(jiǎn)而言之,時(shí)鐘邊沿觸發(fā)后,數(shù)據(jù)也必須保持一段時(shí)間,以便能夠穩(wěn)定讀取,這就是器件需要的保持時(shí)間。如果hold time 不夠,數(shù)據(jù)同樣不能被打入觸發(fā)器。

如果不滿(mǎn)足建立和保持時(shí)間的話(huà),那么DFF(D type flip-flop/D類(lèi)型觸發(fā)器) 將不能正確地采樣到數(shù)據(jù),將會(huì)出現(xiàn)亞穩(wěn)態(tài)(metastability )的情況。如果數(shù)據(jù)信號(hào)在時(shí)鐘沿觸發(fā)前后持續(xù)的時(shí)間均超過(guò)建立和保持時(shí)間,那么超過(guò)量就分別被稱(chēng)為建立時(shí)間裕量和保持時(shí)間裕量。

數(shù)據(jù)到達(dá)時(shí)間 (Data Arrival Time)

輸入數(shù)據(jù)在有效時(shí)鐘沿后到達(dá)所需要的時(shí)間。主要分為三部分:時(shí)鐘到達(dá)寄存器時(shí)間(Tclk1),寄存器輸出延時(shí)(Tco)和數(shù)據(jù)傳輸延時(shí)(Tdata)。

數(shù)據(jù)到達(dá)時(shí)間的計(jì)算公式:

Data Arrival Time = Launch edge + Tclk1 +Tco + Tdata

時(shí)鐘到達(dá)時(shí)間 (Clock Arrival Time)

時(shí)鐘從latch邊沿到達(dá)鎖存寄存器時(shí)鐘輸入端所消耗的時(shí)間為時(shí)鐘到達(dá)時(shí)間。

時(shí)鐘到達(dá)時(shí)間的計(jì)算公式:

Clock Arrival Time = Lacth edge + Tclk2

建立裕量 (Setup Slack)

當(dāng)數(shù)據(jù)需求時(shí)間大于數(shù)據(jù)到達(dá)時(shí)間時(shí),就說(shuō)時(shí)間有余量,Slack是表示設(shè)計(jì)是否滿(mǎn)足時(shí)序的一個(gè)稱(chēng)謂。

建立裕量的計(jì)算公式:

Setup slack = Data Required Time - Data Arrival Time

正的slack表示數(shù)據(jù)需求時(shí)間大于數(shù)據(jù)到達(dá)時(shí)間,滿(mǎn)足時(shí)序(時(shí)序的余量),負(fù)的slack表示數(shù)據(jù)需求時(shí)間小于數(shù)據(jù)到達(dá)時(shí)間,不滿(mǎn)足時(shí)序(時(shí)序的欠缺量)。

最大時(shí)鐘頻率

時(shí)鐘最小周期:系統(tǒng)時(shí)鐘能運(yùn)行的最高頻率。

當(dāng)數(shù)據(jù)需求時(shí)間大于數(shù)據(jù)到達(dá)時(shí)間時(shí),時(shí)鐘具有余量

當(dāng)數(shù)據(jù)需求時(shí)間小于數(shù)據(jù)到達(dá)時(shí)間時(shí),不滿(mǎn)足時(shí)序要求,寄存器經(jīng)歷亞穩(wěn)態(tài)或者不能正確獲得數(shù)據(jù)

當(dāng)數(shù)據(jù)需求時(shí)間等于數(shù)據(jù)到達(dá)時(shí)間時(shí),這是最小時(shí)鐘運(yùn)行頻率,剛好滿(mǎn)足時(shí)序

最小時(shí)鐘周期為數(shù)據(jù)到達(dá)時(shí)間等于數(shù)據(jù)需求時(shí)間。

時(shí)序分析

分析上圖,數(shù)據(jù)傳播的路徑從上一級(jí)觸發(fā)器到下一級(jí)觸發(fā)器建立經(jīng)過(guò)的數(shù)據(jù)時(shí)延總和為:Tclk1 + Tco + Tdata + Tsetup - slack + Tsu。

在兩級(jí)寄存器之間,時(shí)鐘間隔為:Tclk + Tclk2。

根據(jù)建立時(shí)間要求(在下一個(gè)時(shí)鐘上升沿到來(lái)的時(shí)候,數(shù)據(jù)必須穩(wěn)定,且保持一定的時(shí)間Tsu)可以列一個(gè)不等式:數(shù)據(jù)時(shí)延時(shí)鐘間隔,即:Tclk1 + Tco + Tdata + Tsetup - slack + Tsu = Tclk + Tclk2。

同理,根據(jù)保持時(shí)間要求(時(shí)鐘上升沿到來(lái)后,寄存器鎖存數(shù)據(jù)的時(shí)候,數(shù)據(jù)要保持一定的穩(wěn)定時(shí)間Th)可以列出:Tco + Tdata = Th。

隨著系統(tǒng)時(shí)鐘 fclk 變大時(shí),Tclk變小,則要求 Tco + Tdata 也變小,當(dāng) Tco + Tdata 不滿(mǎn)足第一個(gè)不等式時(shí),不滿(mǎn)足建立時(shí)間要求;但是,Tco + Tdata 也不是越小越好,當(dāng)其太小時(shí),不滿(mǎn)足第二個(gè)不等式時(shí),觸發(fā)器不能正常鎖存數(shù)據(jù),即不滿(mǎn)足保持時(shí)間要求。從某種意義上說(shuō),Th限制了數(shù)據(jù)傳輸速率。

對(duì)于設(shè)計(jì)者來(lái)說(shuō)最大的目的是提高時(shí)序的裕量,這樣即使信號(hào)完整性上出現(xiàn)一點(diǎn)問(wèn)題,或者外界環(huán)境發(fā)生一定的變化,系統(tǒng)仍然能正常工作,這就是一個(gè)設(shè)計(jì)優(yōu)良的系統(tǒng)應(yīng)該體現(xiàn)出的超強(qiáng)的穩(wěn)定性。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603867 -

寄存器

+關(guān)注

關(guān)注

31文章

5355瀏覽量

120513

原文標(biāo)題:貨 | FPGA開(kāi)發(fā)設(shè)計(jì)必經(jīng)之路:時(shí)序分析

文章出處:【微信號(hào):FPGA研究院,微信公眾號(hào):FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TPS65950實(shí)時(shí)時(shí)鐘時(shí)序補(bǔ)償分析

使用IBIS模型進(jìn)行時(shí)序分析

FPGA設(shè)計(jì)中時(shí)序分析的概念分析

FPGA設(shè)計(jì)中時(shí)序分析的概念分析

評(píng)論