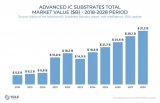

2.5D封裝

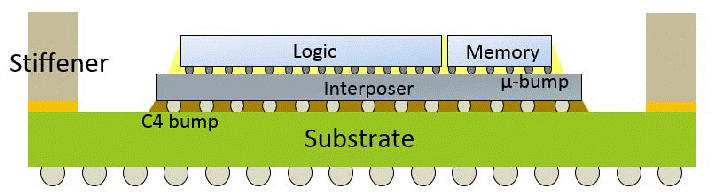

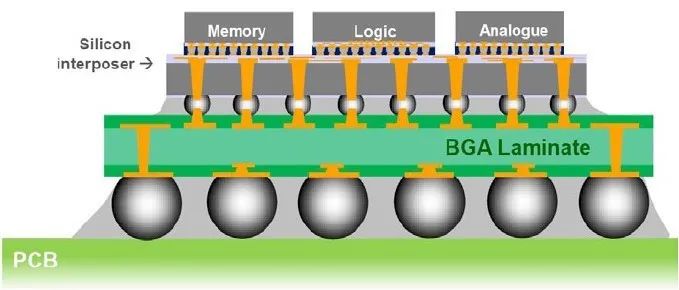

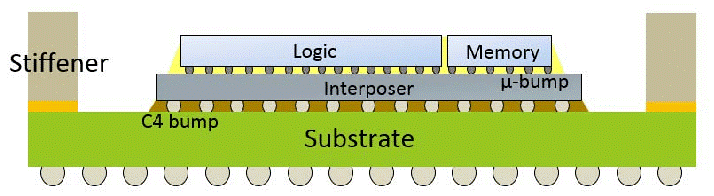

2.5D封裝是傳統(tǒng)2D IC封裝技術(shù)的進(jìn)展,可實現(xiàn)更精細(xì)的線路與空間利用。在2.5D封裝中,裸晶堆棧或并排放置在具有硅通孔(TSV)的中介層(interposer)頂部。其底座,即中介層,可提供芯片之間的連接性。

2.5D封裝通常用于高端ASIC、FPGA、GPU和內(nèi)存立方體。2008年,賽靈思(Xilinx)將其大型FPGA劃分為四個良率更高的較小芯片,并將這些芯片連接到硅中介層。2.5D封裝由此誕生,并最終廣泛用于高帶寬內(nèi)存(HBM)處理器整合。

圖1、2.5D封裝示意圖。(圖片來源:Research Gate)

3D封裝

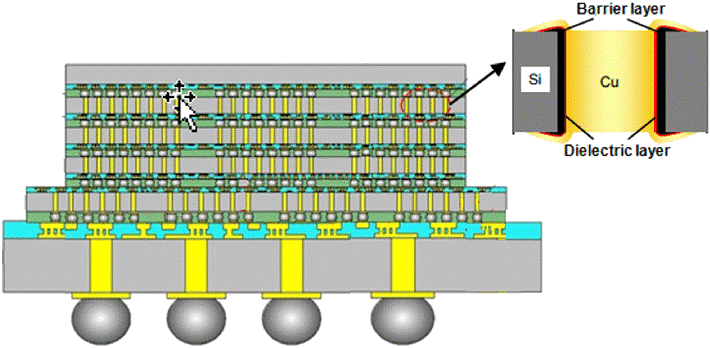

在3D IC封裝中,邏輯裸晶堆棧在一起或與儲存裸晶堆棧在一起,無需建構(gòu)大型的系統(tǒng)單芯片(SoC)。裸晶之間透過主動中介層連接,2.5D IC封裝是利用導(dǎo)電凸塊或TSV將組件堆棧在中介層上,3D IC封裝則將多層硅晶圓與采用TSV的組件連接在一起。

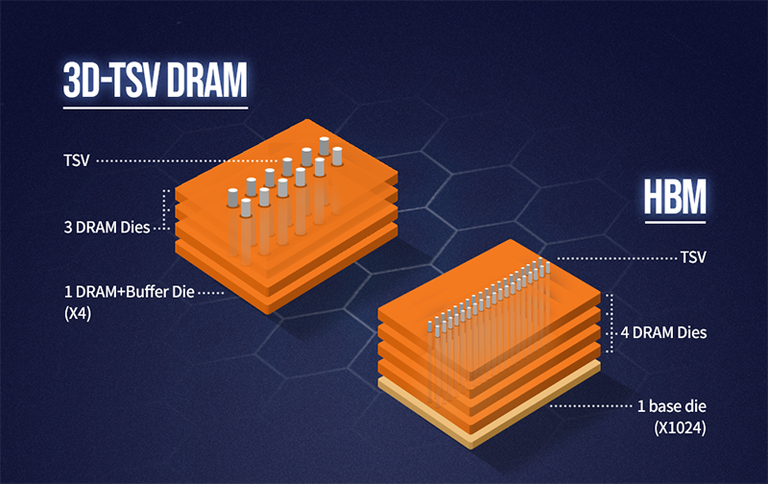

TSV技術(shù)是2.5D和3D IC封裝中的關(guān)鍵使能技術(shù),半導(dǎo)體產(chǎn)業(yè)一直使用HBM技術(shù)生產(chǎn)3D IC封裝的DRAM芯片。

圖2 、從3D封裝的截面圖可以看出,透過金屬銅TSV實現(xiàn)了硅芯片之間的垂直互連。(數(shù)據(jù)源:Research Gate)

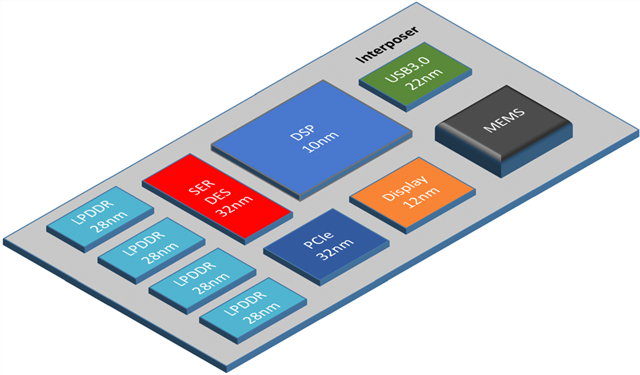

Chiplet

芯片庫中有一系列模塊化芯片可以采用裸晶到裸晶互連技術(shù)整合到封裝中。Chiplet是3D IC封裝的另一種形式,可以實現(xiàn)CMOS組件與非CMOS組件的異質(zhì)整合(Heterogeneous integration)。換句話說,它們是較小型的SoC,也叫做chiplet,而不是封裝中的大型SoC。

將大型SoC分解為較小的小芯片,與單顆裸晶相比具有更高的良率和更低的成本。Chiplet使設(shè)計人員可以充分利用各種IP,而不用考慮采用何種工藝節(jié)點,以及采用何種技術(shù)制造。他們可以采用多種材料,包括硅、玻璃和層壓板來制造芯片。

圖3、基于Chiplet的系統(tǒng)是由中介層上的多個Chiplet組成。(圖片來源:Cadence) 扇出(Fan out)

在扇出封裝中,“連結(jié)”(connection)被扇出芯片表面,從而提供更多的外部I/O。它使用環(huán)氧樹脂成型材料(EMC)完全嵌入裸晶,不需要諸如晶圓凸塊、上助焊劑、倒裝芯片、清潔、底部噴灑充膠和固化等工藝流程,因此也無需中介層,使異質(zhì)整合變得更加簡單。

扇出技術(shù)是比其他封裝類型具有更多I/O的小型封裝。2016年,蘋果(Apple)借助臺積電(TSMC)的封裝技術(shù),將其16納米應(yīng)用處理器與移動DRAM整合到iPhone 7的一個封裝中,從而將這項技術(shù)推向舞臺。

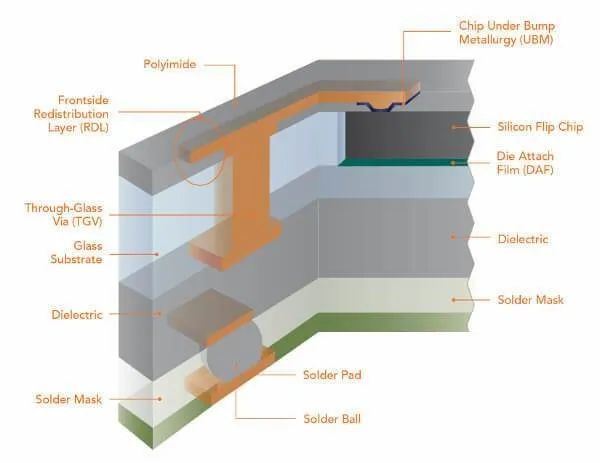

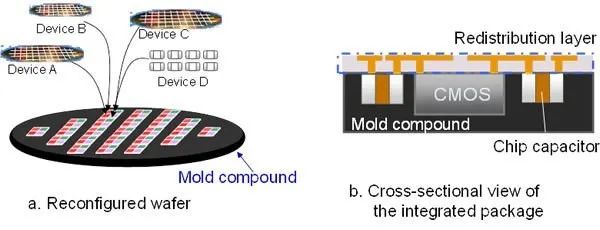

扇出晶圓級封裝(FOWLP)

FOWLP技術(shù)是針對晶圓級封裝(WLP)的改進(jìn),可以為硅芯片提供更多外部連接。它將芯片嵌入環(huán)氧樹脂成型材料中,然后在晶圓表面建構(gòu)高密度重分布層(RDL)并施加焊錫球,形成重構(gòu)晶圓(reconstituted wafer)。

它通常先將經(jīng)過處理的晶圓切成單顆裸晶,然后將裸晶分散放置在載體結(jié)構(gòu)(carrier structure)上,并填充間隙以形成重構(gòu)晶圓。FOWLP在封裝和應(yīng)用電路板之間提供了大量連接,而且由于基板比裸晶要大,裸晶的間距實際上更寬松。

圖4、在此FOWLP封裝示例中,硅倒裝芯片嵌入到玻璃基板中,重分布層透過芯片扇出至玻璃通孔。(圖片來源:Samtec)

異質(zhì)整合

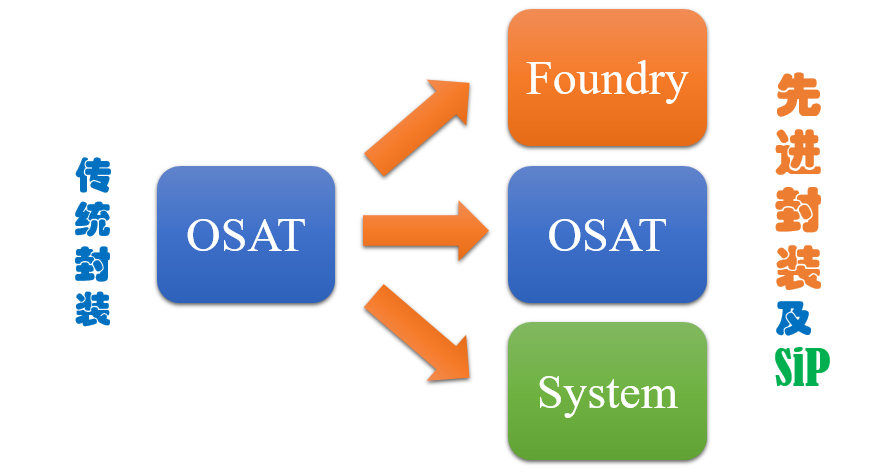

將分開制造的不同組件整合到更高級別的組件中,可以增強(qiáng)功能并改進(jìn)工作特性,因此半導(dǎo)體組件制造商能夠?qū)⒉捎貌煌に嚵鞒痰墓δ芙M件組合到一個組件中。

異質(zhì)整合類似于系統(tǒng)級封裝(SiP),但它并不是將多顆裸晶整合在單個基板上,而是將多個IP以Chiplet的形式整合在單個基板上。異質(zhì)整合的基本思想是將多個具有不同功能的組件組合在同一個封裝中。

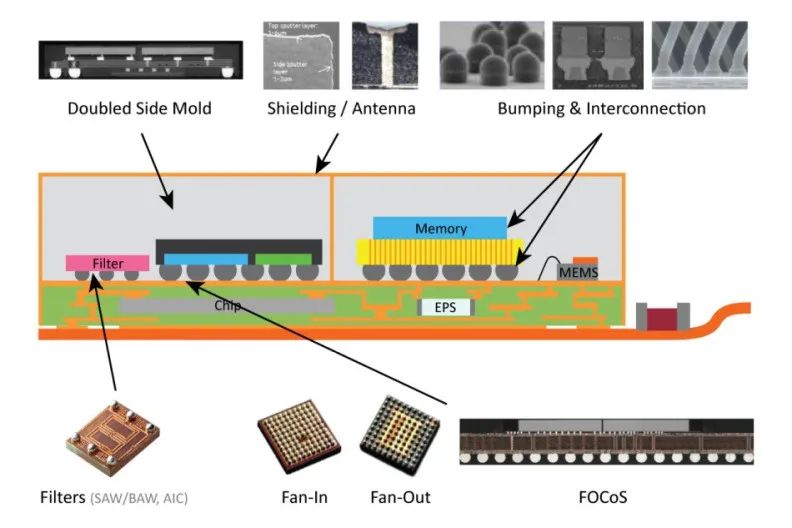

圖5、異質(zhì)整合中的一些技術(shù)建構(gòu)區(qū)塊。(圖片來源:ASE Group)

HBM

HBM是一種標(biāo)準(zhǔn)化的堆棧儲存技術(shù),可為堆棧內(nèi)部,以及內(nèi)存與邏輯組件之間的數(shù)據(jù)提供高帶寬信道。HBM封裝將內(nèi)存裸晶堆棧起來,并透過TSV將它們連接在一起,從而創(chuàng)建更多的I/O和帶寬。

HBM是一種JEDEC標(biāo)準(zhǔn),它在封裝內(nèi)垂直整合了多層DRAM組件,封裝內(nèi)還有應(yīng)用處理器、GPU和SoC。HBM主要以2.5D封裝的形式實現(xiàn),用于高端服務(wù)器和網(wǎng)絡(luò)芯片。現(xiàn)在發(fā)布的HBM2版本解決了初始HBM版本中的容量和時鐘速率限制問題。

圖6、HBM封裝將內(nèi)存裸晶彼此堆棧,并利用TSV將它們連接起來以創(chuàng)建更多I/O和帶寬。(圖片來源:SK Hynix)

中介層

中介層是封裝中多芯片裸晶或電路板傳遞電信號的管道,是插口或接頭之間的電接口,可以將信號傳播更遠(yuǎn),也可以連接到板子上的其他插口。

中介層可以由硅和有機(jī)材料制成,充當(dāng)多顆裸晶和電路板之間的橋梁。硅中介層是一種經(jīng)過驗證的技術(shù),具有較高的細(xì)間距I/O密度和TSV形成能力,在2.5D和3D IC芯片封裝中扮演著關(guān)鍵角色。

圖7、系統(tǒng)分區(qū)中介層的典型實現(xiàn)。(數(shù)據(jù)源:Yole Développement)

重分布層

重分布層包含銅連接線或走線,用于實現(xiàn)封裝各個部分之間的電氣連接。它是金屬或高分子介電材料層,裸晶可以堆棧在封裝中,從而縮小大芯片組的I/O間距。重分布層已成為2.5D和3D封裝解決方案中不可或缺的一部分,使其上的芯片可以利用中介層相互進(jìn)行通訊。

圖8、使用重分布層的整合封裝。(圖片來源:Fujitsu)

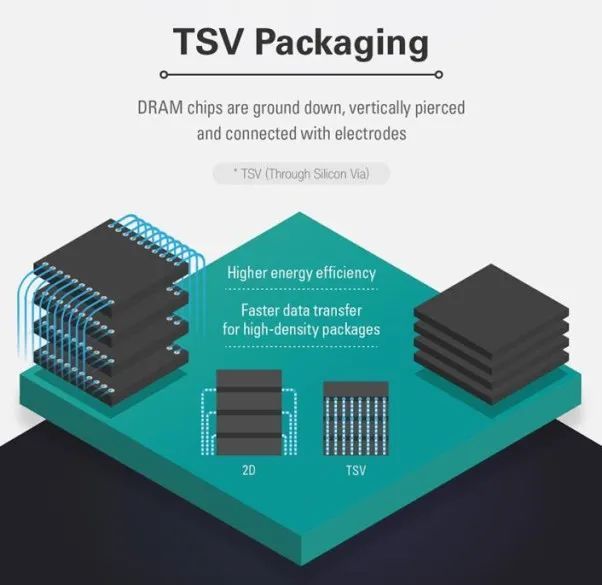

TSV

TSV是2.5D和3D封裝解決方案的關(guān)鍵實現(xiàn)技術(shù),是在晶圓中填充銅,提供貫通硅晶圓裸晶的垂直互連。它貫穿整個芯片以提供電氣連接,形成從芯片一側(cè)到另一側(cè)的最短路徑。

從晶圓的正面將通孔或孔洞蝕刻到一定深度,然后將其絕緣,并沉積導(dǎo)電材料(通常為銅)進(jìn)行填充。芯片制造完成后,從晶圓的背面將其減薄,以暴露通孔和沉積在晶圓背面的金屬,從而完成TSV互連。

圖9、在TSV封裝中,DRAM芯片接地、穿透并與電極相連。(圖片來源:Samsung Electronics)

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602997 -

IC封裝

+關(guān)注

關(guān)注

4文章

185瀏覽量

26718 -

HBM

+關(guān)注

關(guān)注

0文章

379瀏覽量

14744

原文標(biāo)題:先進(jìn)IC封裝的10個基本術(shù)語

文章出處:【微信號:項華電子DXE,微信公眾號:項華電子DXE】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

先進(jìn)IC封裝中最常用10個術(shù)語解析

淺談先進(jìn)封裝的四要素

#硬聲創(chuàng)作季 【科普向】傳統(tǒng)封裝與先進(jìn)封裝有何差異?——為什么需要先進(jìn)封裝

簡單介紹IC的高性能封裝

Mentor推出獨特端到端Xpedition高密度先進(jìn)封裝流程

10個基本的高級IC封裝術(shù)語

變則通,國內(nèi)先進(jìn)封裝大跨步走

先進(jìn)封裝演進(jìn),ic載板的種類有哪些?

什么是先進(jìn)封裝?先進(jìn)封裝技術(shù)包括哪些技術(shù)

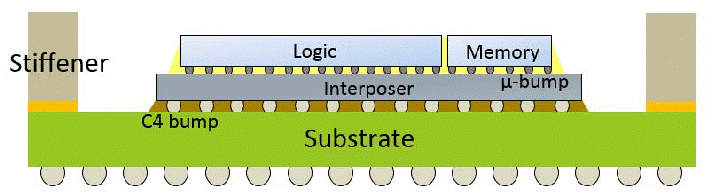

全球先進(jìn)IC載板市場分析

先進(jìn)IC載板市場的變革與機(jī)遇

分享幾個先進(jìn)IC封裝的案例

分享幾個先進(jìn)IC封裝的案例

評論