文章摘要

信息社會的迅猛發(fā)展極大推動了對高性能計算的需求。而先進互補金屬氧化物半導(dǎo)體(CMOS)制造工藝是制造高性能計算芯片的保障,因此成為世界頂尖設(shè)計公司和芯片制造企業(yè)競爭的技術(shù)高地。文章概述了鰭式場效應(yīng)晶體管(FinFET)之后技術(shù)演進到環(huán)柵場效應(yīng)晶體管(GAAFET)的必然性,以及在工藝模塊、系統(tǒng)集成和工藝無損表征上帶來的挑戰(zhàn)。在先進CMOS制造工藝技術(shù)的創(chuàng)新上,需要有從器件開發(fā)到系統(tǒng)設(shè)計的思維轉(zhuǎn)變;設(shè)計工藝協(xié)同優(yōu)化(DTCO)將會發(fā)揮越來越重要的作用。面向未來國產(chǎn)先進的CMOS制造工藝的發(fā)展,在技術(shù)開發(fā)和人才培養(yǎng)方面提出了發(fā)展建議和舉措。

文章速覽

移動智能終端之外,未來隨著智能工廠、自動駕駛,以及視頻服務(wù)的快速發(fā)展,全球數(shù)據(jù)量急劇增長,大大推動了對高性能計算芯片的需求。而先進互補金屬氧化物半導(dǎo)體(Complementary Metal-Oxide-Semiconductor, CMOS)制造工藝可以提高單位面積下的計算性能和降低所需的功耗,因此除了芯片制造企業(yè)中國臺灣積體電路制造股份有限公司(簡稱臺積電)、韓國三星和美國英特爾,頂尖的芯片設(shè)計公司如英偉達、蘋果和高通等也都爭先獲得最先進的CMOS工藝制程技術(shù),從而保持行業(yè)領(lǐng)導(dǎo)者的地位。在過去幾年中,沒有掌握最先進CMOS制造工藝,嚴(yán)重影響了中國大陸在智能手機和自動駕駛等高端領(lǐng)域的芯片發(fā)展。目前,主流的鰭式場效應(yīng)晶體管(Fin Field-Effect Transistor, FinFET)技術(shù)已經(jīng)進入3 nm節(jié)點,臺積電即將在2022年底前實現(xiàn)量產(chǎn);而三星則實現(xiàn)了從FinFET到環(huán)柵器件技術(shù)的跨越,在2022年6月底實現(xiàn)了3 nm多橋通道場效應(yīng)晶體管(Multi-Bridge Channel Field-Effect Transistor, MBCFET)的量產(chǎn)。

在過去20年中,CMOS工藝經(jīng)歷了3次重要的技術(shù)革新:①2003年的應(yīng)變硅技術(shù);②2007年的高κ金屬柵技術(shù);③2011年的FinFET技術(shù)。尤其是FinFET技術(shù)的引入,使得晶體管在提供大的驅(qū)動電流的同時大大降低了關(guān)態(tài)漏電流,極大地促進了過去10多年移動時代的發(fā)展,催生了改變?nèi)藗兩罘绞降闹悄苁謾C和智能穿戴設(shè)備。進入下一個新技術(shù)周期,高速通信和大數(shù)據(jù)是社會發(fā)展的基礎(chǔ)平臺,而這又以先進CMOS制造技術(shù)為基礎(chǔ)的高性能計算為核心。從技術(shù)發(fā)展來看,進入3 nm以下CMOS技術(shù)節(jié)點后,納米片環(huán)柵場效應(yīng)晶體管(Nanosheet Gate-All-Around Field-Effect Transistor, NS-GAAFET)將替代FinFET成為全新一代的CMOS技術(shù)架構(gòu)。本文從FinFET技術(shù)的局限性出發(fā),分析環(huán)柵場效應(yīng)晶體管(Gate-All-Around Field-Effect Transistor, GAAFET)技術(shù)發(fā)展的必然性;然后系統(tǒng)概述GAAFET帶來的關(guān)鍵工藝技術(shù)挑戰(zhàn);討論面臨這些挑戰(zhàn)時,如何抓住發(fā)展機遇,夯實國產(chǎn)先進工藝自主發(fā)展的道路。

1

從FinFET到GAAFET

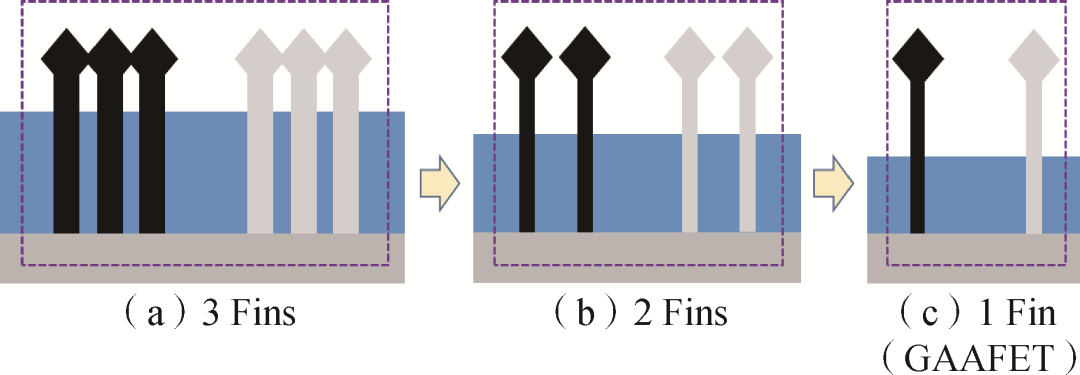

進入3 nm以下技術(shù)節(jié)點后,器件的柵長只有12~15 nm,F(xiàn)inFET沒有足夠的柵控能力來有效關(guān)斷鰭下寄生(Sub-fin)溝道,從而導(dǎo)致器件的亞閾值擺幅(Subthreshold Swing, SS)超過75 mV/dec。另外,鰭(Fin)的高寬比(Aspect-ratio)也持續(xù)增大,超過10∶1后將導(dǎo)致Fin發(fā)生彎曲甚至坍塌。更為重要的是,隨著邏輯標(biāo)準(zhǔn)單元尺寸的縮小,單個晶體管包含F(xiàn)in的數(shù)量從最初的3根減少到1根,勢必導(dǎo)致單個晶體管驅(qū)動能力的下降,如圖1所示,這就要求增加Fin的高度,但是會使得Fin的機械穩(wěn)定性變得更差。納米片環(huán)柵場效應(yīng)晶體管通過在單位面積上堆疊多層納米片溝道,可以有效提高單個晶體管的驅(qū)動能力;同時因為采用了環(huán)柵結(jié)構(gòu)大大增強了器件的柵控能力。因此,堆疊納米片GAAFET技術(shù)是FinFET演變的必然結(jié)果。在GAAFET技術(shù)中,溝道控制能力取決于納米片溝道的厚度而不是寬度,所以GAAFET的納米片寬度可以連續(xù)調(diào)節(jié)(FinFET技術(shù)中Fin寬度是固定的),這給電路設(shè)計帶來了很大的靈活性。另外,GAAFET技術(shù)中的單Fin結(jié)構(gòu)使得對外延源漏可以進行較為靈活的設(shè)計,有利于環(huán)繞接觸(Wrap-around-contact)工藝的開發(fā),從而減小器件寄生電阻/電容,提高GAAFET的器件性能。

圖1邏輯標(biāo)準(zhǔn)單元的尺寸由多Fin演變?yōu)閱蜦in的示意圖

2

環(huán)柵場效應(yīng)晶體管關(guān)鍵工藝面臨的挑戰(zhàn)

雖然環(huán)柵場效應(yīng)晶體管的制造技術(shù)仍以FinFET工藝為主體,但由于器件溝道和柵結(jié)構(gòu)的變化,給與之對應(yīng)的器件制備與工藝集成帶來了諸多全新的技術(shù)挑戰(zhàn)。

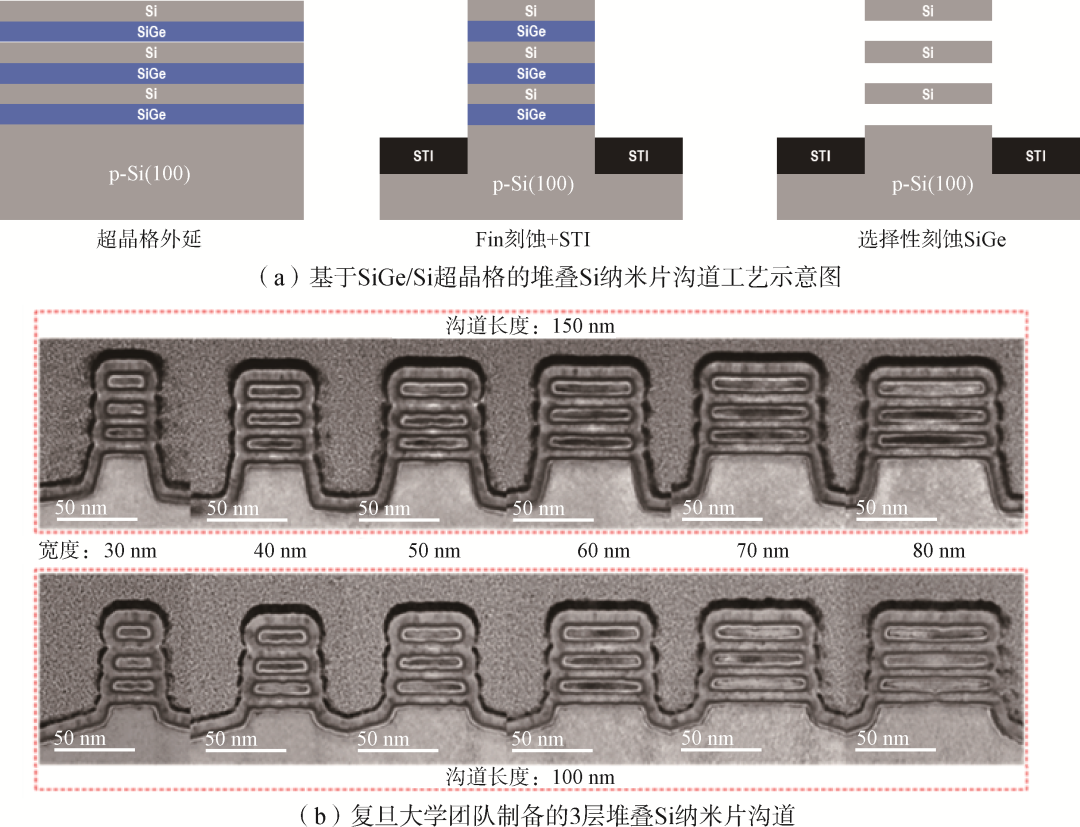

2.1溝道形成工藝

環(huán)柵器件溝道形成是在Si襯底上外延生長SiGe/Si的超晶格結(jié)構(gòu),然后進行選擇性刻蝕形成堆疊Si納米片溝道。該工藝的關(guān)鍵是:①外延高質(zhì)量的SiGe/Si超晶格結(jié)構(gòu),并在淺槽隔離(Shallow Trench Isolation, STI)工藝后保持SiGe/Si的界面處不發(fā)生Ge擴散;②SiGe對Si的高選擇比刻蝕,在刻蝕SiGe的同時保持Si納米片溝道的完整性,工藝示意圖如圖2(a)所示。另外,在選擇性刻蝕SiGe層時,Si納米片溝道中的應(yīng)力會造成納米片之間的粘連甚至坍塌,如何在保持高刻蝕選擇比的同時保證Si納米片溝道的完整性成為環(huán)柵器件溝道形成工藝的關(guān)鍵挑戰(zhàn)。復(fù)旦大學(xué)基于國產(chǎn)刻蝕裝備和自主開發(fā)的工藝,可以較好地實現(xiàn)不同納米片寬度的3層堆疊Si溝道結(jié)構(gòu),如圖2(b)所示。

圖2基于SiGe/Si超晶格結(jié)構(gòu)的堆疊Si納米片溝道的工藝制備

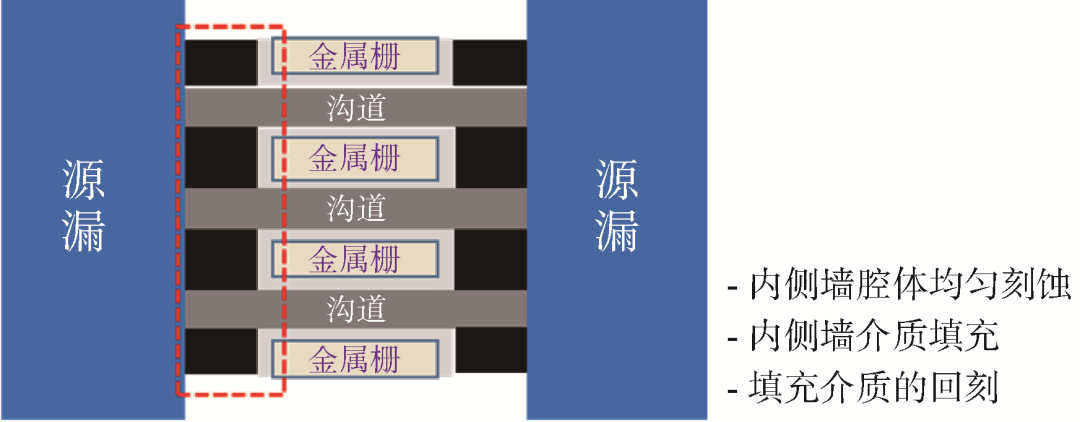

2.2內(nèi)側(cè)墻工藝

由于納米片環(huán)柵器件的溝道特殊性,需要在源漏外延之前形成內(nèi)側(cè)墻(Inner-spacer),降低源漏與柵極之間的耦合電容,從而改善器件的開關(guān)頻率,如圖3所示。2009年法國原子能委員會電子與信息技術(shù)實驗室(CEA-Leti)首次提出并開發(fā)了內(nèi)側(cè)墻工藝集成技術(shù),將寄生電容減少了30%~40%,并且不影響器件電流開關(guān)比。內(nèi)側(cè)墻的腔體(Cavity)刻蝕既要和溝道形成工藝一樣具有很高的刻蝕選擇比,更在于腔體橫向深度的精確控制,以保證堆疊溝道之間的一致性。通過原子層沉積(Atomic Layer Deposition, ALD)工藝在腔體中填充較低介電常數(shù)的介質(zhì)材料,之后進行回刻(Etch Back),從而形成均勻的內(nèi)側(cè)墻。雖然內(nèi)側(cè)墻技術(shù)很好地改善了寄生電容,但給后續(xù)的源漏選擇性外延帶來了很大的挑戰(zhàn)。

圖3環(huán)柵器件內(nèi)側(cè)墻結(jié)構(gòu)和關(guān)鍵工藝示意圖

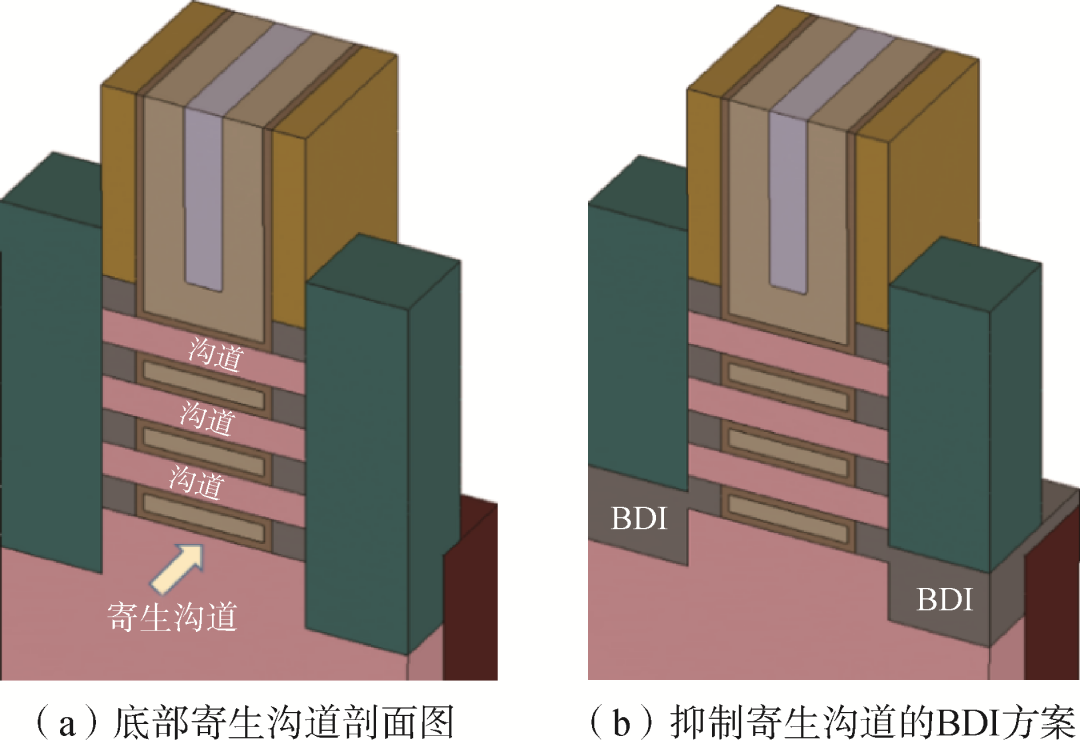

2.3底部寄生晶體管

環(huán)柵場效應(yīng)晶體管的底部天然存在一個寄生的鰭式溝道,使得實際器件為上部分環(huán)柵器件和下部分寄生晶體管的并聯(lián),這一寄生溝道對整體器件性能有不可忽視的影響,如圖4(a)所示。在寄生鰭高度較低的情況下,由于較差的溝道控制能力,使得器件的亞閾值擺幅增大和開關(guān)電流比下降;如果增加寄生鰭式溝道的高度,雖然會改善寄生溝道控制能力,但會使寄生溝道面積在整個器件溝道總面積中占比加大,失去環(huán)柵晶體管短溝道效應(yīng)抑制的主導(dǎo)優(yōu)勢。為了解決這個問題,國際商業(yè)機器公司(IBM)在2019年開發(fā)了一種創(chuàng)新的源漏隔離技術(shù):預(yù)先填埋底部介質(zhì)隔離(Bottom Dielectric Isolation, BDI),如圖4(b)所示。BDI可以阻斷寄生溝道的電流流出,從而破壞寄生晶體管的形成。這項技術(shù)需要在源漏外延前進行介質(zhì)填埋,這給后續(xù)的源漏選擇性Si和SiGe外延工藝帶來了新的問題。

圖4GAAFET底部寄生溝道的來由以及抑制方案

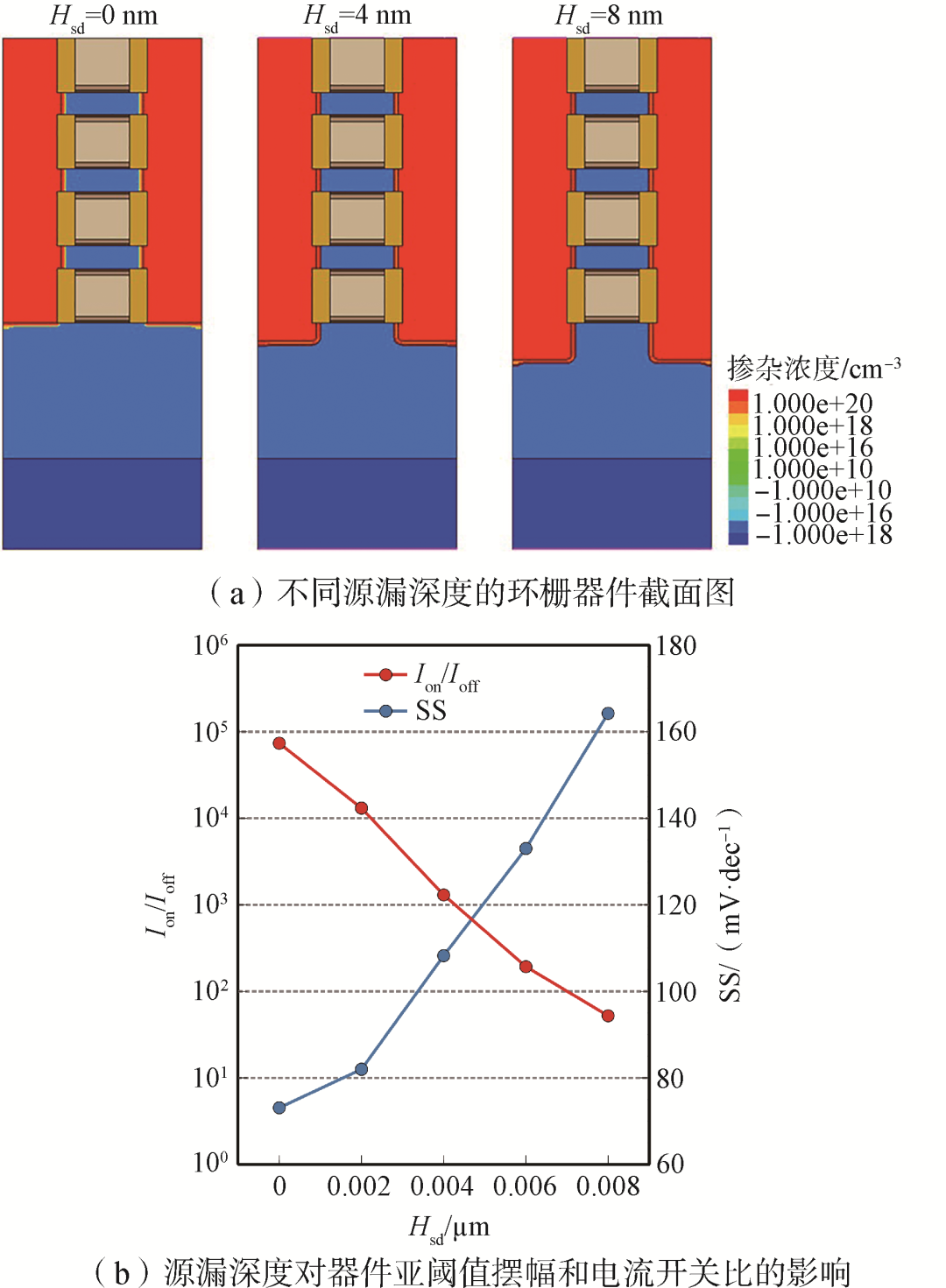

為了避免抑制寄生溝道對源漏外延造成影響,另一個思路就是精確控制源漏的刻蝕深度。研究表明,源漏深度的減小可以很好地抑制寄生溝道的電流輸出,筆者團隊的仿真研究也驗證了源漏深度(Hsd)的精確控制可以有效地改善器件的亞閾值擺幅(SS)和電流開關(guān)比(Ion/Ioff),如圖5所示。這對源漏刻蝕深度及其均勻性的控制提出了非常高的要求。

圖5GAAFET源漏深度對器件性能的影響

2.4源漏寄生電阻/電容優(yōu)化

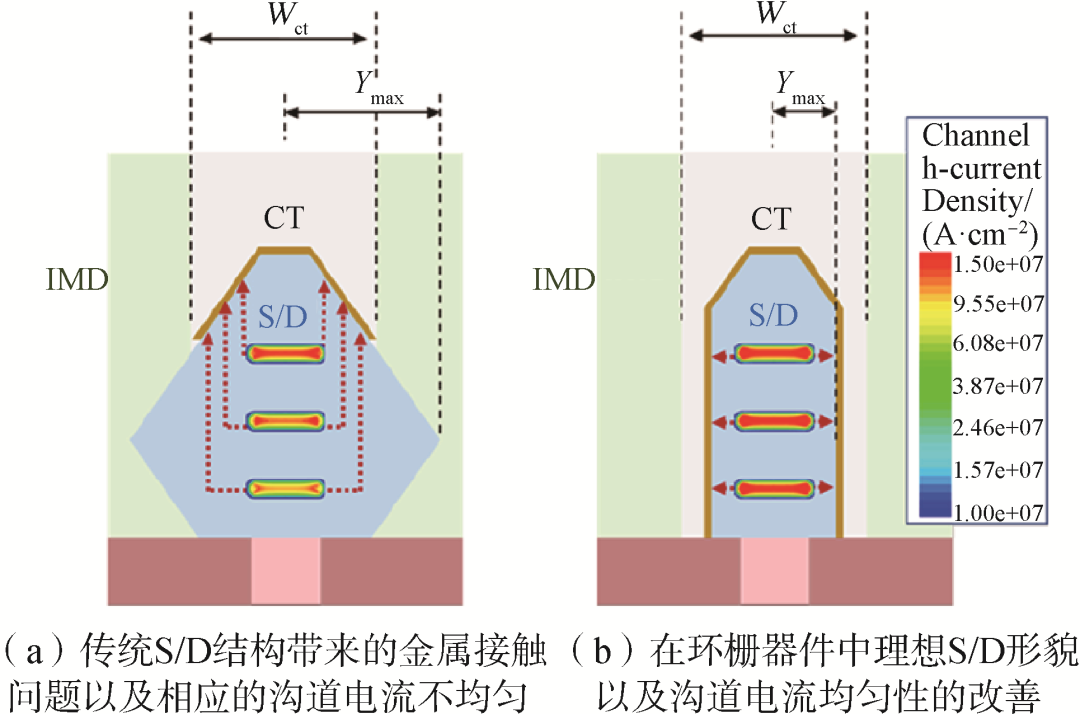

為滿足3 nm及以下節(jié)點器件驅(qū)動電流的需求,堆疊環(huán)柵器件的Fin寬和Fin高都比FinFET要大,對應(yīng)的外延源漏的體量也隨之增加,這使得:①源漏(S/D)的寄生電容顯著增加;②由于接觸工藝關(guān)鍵尺寸(Contact CD)的限制,源漏金屬接觸只能覆蓋源漏頂端一部分,大的寄生電阻大大降低了底部納米片溝道的導(dǎo)通效率,如圖6(a)所示。解決這個問題的方向是減小源漏的體積,同時形成包裹式金屬接觸(Wrap Around Contact, WAC),進而實現(xiàn)源漏寄生電阻/電容的優(yōu)化。

圖6源漏結(jié)構(gòu)對歐姆接觸及溝道電流分布的影響

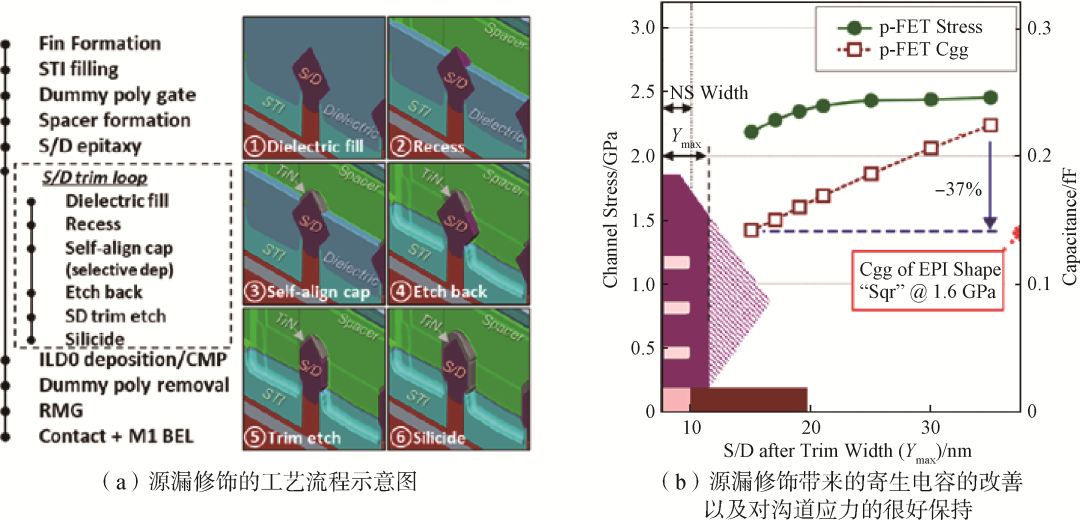

為了制備這樣的源漏結(jié)構(gòu),一種直接的工藝選擇是限制型源漏外延。但由于限制帶來的外延體量的減小可能會影響對溝道所能形成的應(yīng)力,這對于增強P型絕緣柵場效應(yīng)晶體管(P-type Metal-Oxide-Semiconductor Field-Effect Transistor, PMOSFET)的驅(qū)動能力尤為重要。復(fù)旦大學(xué)的研究團隊創(chuàng)新性地提出了另外一種實現(xiàn)方法:源漏修飾工藝(S/D Trimming Process),如圖7所示。在源漏外延工藝后,進行介質(zhì)填充并回刻以露出鉆石型源漏的頂部;然后進行選擇性的TiN沉積,形成自對準(zhǔn)的硬掩膜;之后順序進行介質(zhì)刻蝕和源漏的修飾。這種工藝在減小源漏物理尺寸后可以形成包裹式金屬接觸,同時很好地保持了溝道應(yīng)力,而且該工藝在納米片溝道堆疊層數(shù)增加的情況下改進優(yōu)勢會更顯著。

圖7源漏結(jié)構(gòu)修飾及其對寄生電容的影響

2.5N/P電流匹配的挑戰(zhàn)

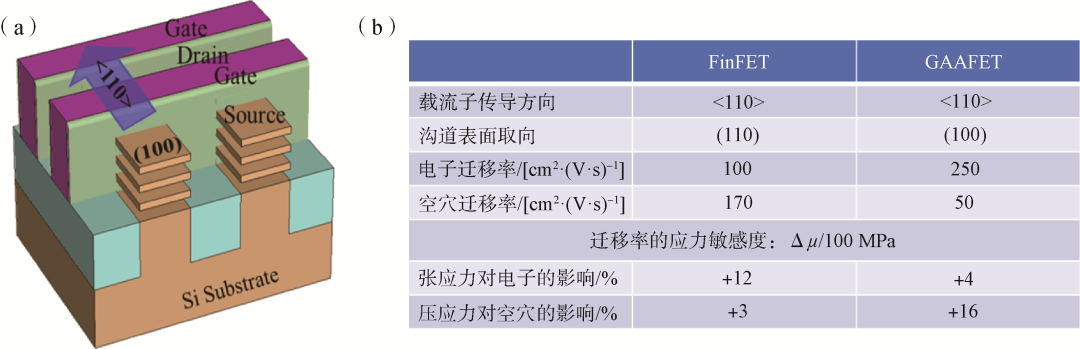

環(huán)柵器件的溝道導(dǎo)電面由FinFET中的110變成了100,如圖8所示,這意味著電子傳輸性能的增強和空穴傳輸性能的退化,造成N型絕緣柵場效應(yīng)晶體管(N-type Metal-Oxide-Semiconductor Field-Effect Transistor, NMOSFET)和PMOSFET的驅(qū)動電流不匹配,從而增加了芯片面積并降低了系統(tǒng)性能。幸運的是,空穴在100導(dǎo)電面上的應(yīng)力敏感度有很大的提升。因此,為實現(xiàn)環(huán)柵器件的N/P電流匹配,對PMOSFET的溝道應(yīng)力增強設(shè)計尤為關(guān)鍵。

圖8FinFET與GAAFET的溝道導(dǎo)電面對比

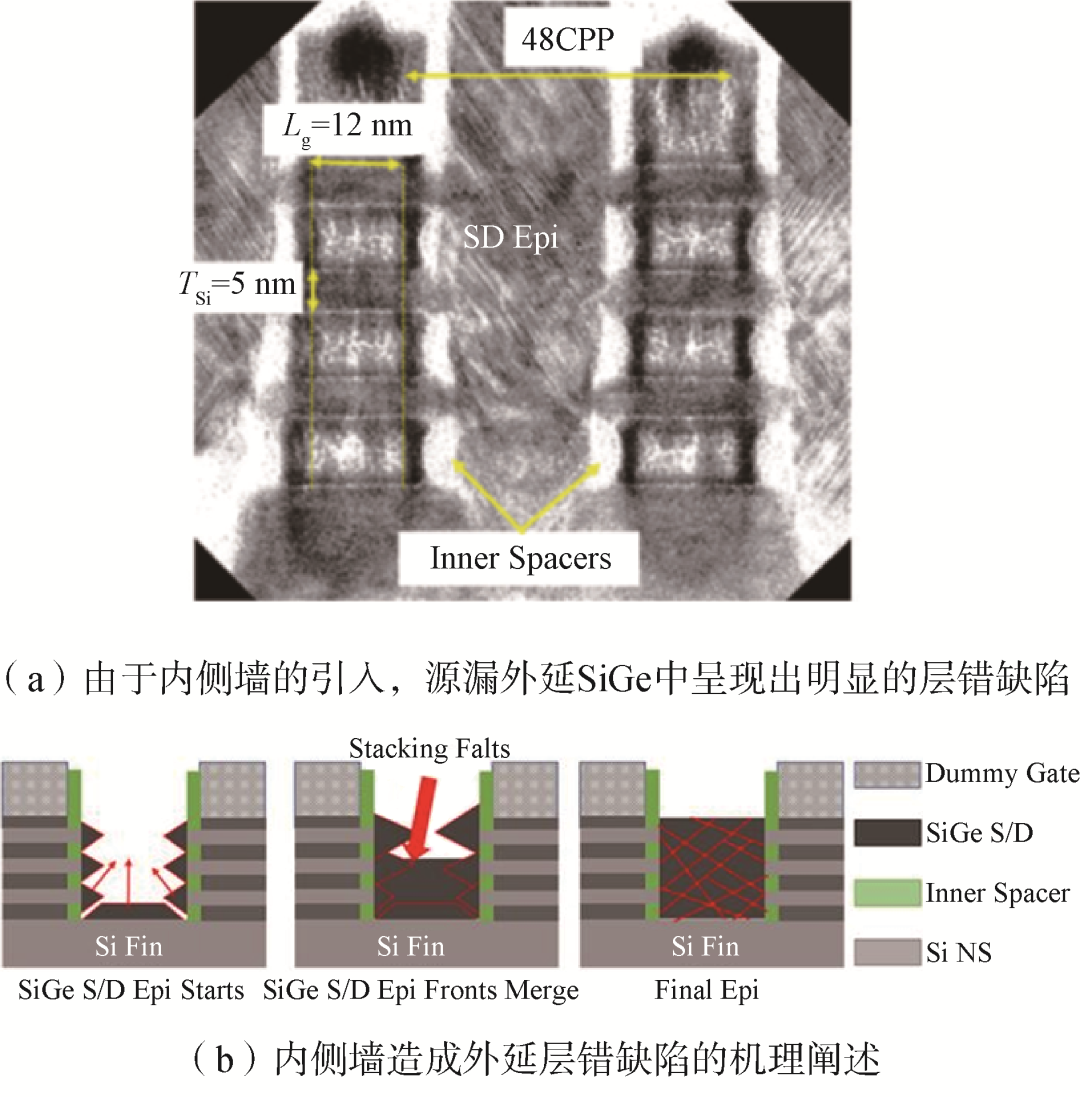

然而,如2.2節(jié)中所闡述的,內(nèi)側(cè)墻的引入打斷了外延表面的連續(xù)性,這使得常規(guī)外延工藝生長的源漏SiGe中有過高的層錯缺陷密度(圖9(a)),從而造成溝道應(yīng)力的丟失;圖9(b)給出了相關(guān)的機理闡述。因此,需要探索新的外延工藝來控制層錯缺陷密度,甚至需要在工藝整合上進行創(chuàng)新來實現(xiàn)應(yīng)力的增強,最終實現(xiàn)N/P電流匹配。

圖9內(nèi)側(cè)墻造成源漏外延缺陷及其形成機理

3

環(huán)柵場效應(yīng)晶體管關(guān)鍵工藝面臨的發(fā)展機遇

雖然三星在2022年6月已經(jīng)量產(chǎn)了3 nm環(huán)柵器件工藝,比現(xiàn)在的5 nm FinFET技術(shù)性能提升30%、功耗減少50%。但臺積電將在3 nm繼續(xù)使用更先進的FinFET技術(shù),宣稱到2025年才會量產(chǎn)2 nm環(huán)柵器件工藝,英特爾也大致會在這個時間點發(fā)布20 A節(jié)點的環(huán)柵器件技術(shù)(英特爾稱之為RibbonFET)。這在某種程度上意味著環(huán)柵器件還有諸多的工藝問題沒有得到很好的解決,或者說現(xiàn)有技術(shù)條件下引入環(huán)柵器件所能帶來的性能優(yōu)勢不夠。因此,上述分析的環(huán)柵器件的工藝挑戰(zhàn)也帶來了一個很好的發(fā)展機遇。

3.1工藝裝備

在先進CMOS制造中,極紫外(Extreme Ultra-Violet, EUV)光刻機固然起著舉足輕重的作用,但在環(huán)柵器件工藝中還有一些同樣不可或缺的關(guān)鍵工藝裝備,需要盡早布局進行研發(fā),才有可能在將來的環(huán)柵工藝中占有一席之地。

3.1.1 SiGe外延

環(huán)柵器件溝道的基礎(chǔ)是SiGe/Si超晶格結(jié)構(gòu)。為保證最終堆疊納米片溝道的均勻性,SiGe/Si界面的Ge擴散要均勻控制在5 A以內(nèi),這對SiGe外延的均勻性和溫度一致性控制都提出了極高的要求。另外內(nèi)側(cè)墻的引入,PMOSFET中的源漏外延SiGe中不可避免地存在高密度的層錯缺陷,抑制這些缺陷的形成需要創(chuàng)新的工藝技術(shù),譬如自下而上(Bottom-up)外延工藝及其裝備的開發(fā),或是高質(zhì)量非選擇性硅襯墊(Si-liner)的外延技術(shù)探索。

3.1.2 溝道選擇性刻蝕

環(huán)柵器件溝道的形成關(guān)鍵取決于高選擇比的SiGe/Si刻蝕。但在實現(xiàn)高選擇比刻蝕工藝的同時,還要保證溝道不被刻蝕損傷以及溝道不發(fā)生粘連甚至坍塌。傳統(tǒng)的電感耦合等離子體(Inductively Coupled Plasma, ICP)和電容耦合等離子體(Capacitively Coupled Plasma, CCP)刻蝕機不能滿足這個需求,應(yīng)用遠程等離子體源(Remote Plasma Source, RPS)或是氣相刻蝕技術(shù)才能解決這個問題。溝道形成后的表面處理工藝是整個CMOS器件的核心,過程中如何保持此時懸空溝道的完整性以及如何集成表面處理裝置,必須進行系統(tǒng)的考慮和設(shè)計。

3.1.3 多閾值調(diào)節(jié)的ALD工藝

受限于環(huán)柵器件溝道與溝道之間的有限空間,不同于FinFET技術(shù)中主要通過金屬柵厚度和不同柵材料的組合來實現(xiàn)多閾值調(diào)節(jié),還需要開發(fā)新型的金屬柵工藝如偶極子(Dipole)調(diào)節(jié)技術(shù)等。可以看出,先進CMOS制造流程中工藝與工藝之間的關(guān)聯(lián)越來越強,這就要求設(shè)備廠商在單步工藝之外形成工藝整合的能力,才能在開發(fā)過程中有效地進行閉環(huán)驗證,針對問題快速反應(yīng),開發(fā)出有競爭力的工藝裝備及配套工藝。

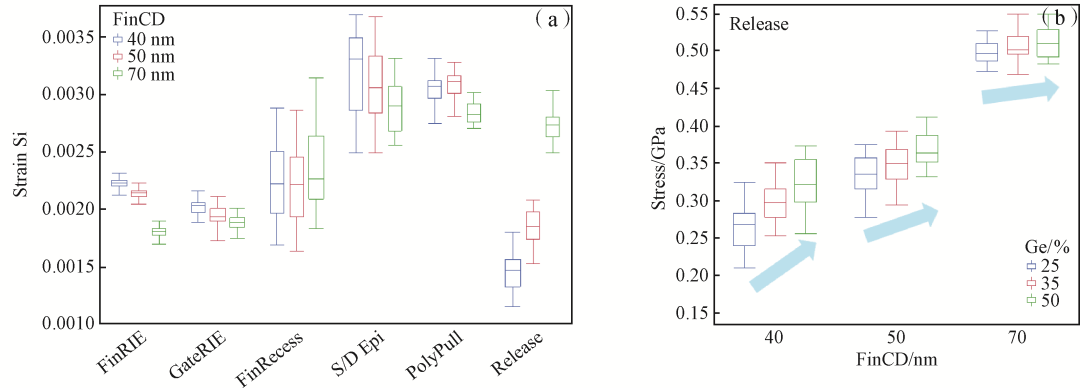

3.2工藝在線檢測技術(shù)

隨著先進制造工藝的復(fù)雜程度和精細程度越來越高,為了保證生產(chǎn)良率,對關(guān)鍵工藝步驟進行在線檢測變得越來越重要。環(huán)柵器件的溝道應(yīng)力和完整性決定了最終器件的性能,同時也可以反映出制造流程下的工藝健康程度。因此,在線無損檢測溝道應(yīng)力演變成為一個很好的選擇。最近,IBM聯(lián)合新星測量儀器(Nova Measuring Instruments)公司開發(fā)了拉曼(Raman)表征技術(shù),成功實現(xiàn)了全流程的溝道應(yīng)力演變的在線檢測,如圖10所示。圖10(a)展示了不同F(xiàn)in寬下Si溝道應(yīng)力在環(huán)柵工藝過程中的演變,而圖10(b)展示了在溝道釋放后Si溝道應(yīng)力對于不同F(xiàn)in寬和Ge組分的變化。

圖10利用在線Raman表征技術(shù)表征Si溝道應(yīng)力在環(huán)柵工藝過程中的演變(a)及其對不同F(xiàn)in寬和Ge組分的變化(b)

與此同時,復(fù)旦大學(xué)團隊也基于Raman表征技術(shù)自主開發(fā)了環(huán)柵器件的在線工藝檢測技術(shù),與工藝仿真結(jié)果有很好的吻合。該團隊還發(fā)現(xiàn)在線Raman表征技術(shù)可以用于檢測堆疊溝道是否發(fā)生了坍塌。除此之外,源漏外延的缺陷檢測也是環(huán)柵工藝中的挑戰(zhàn)。

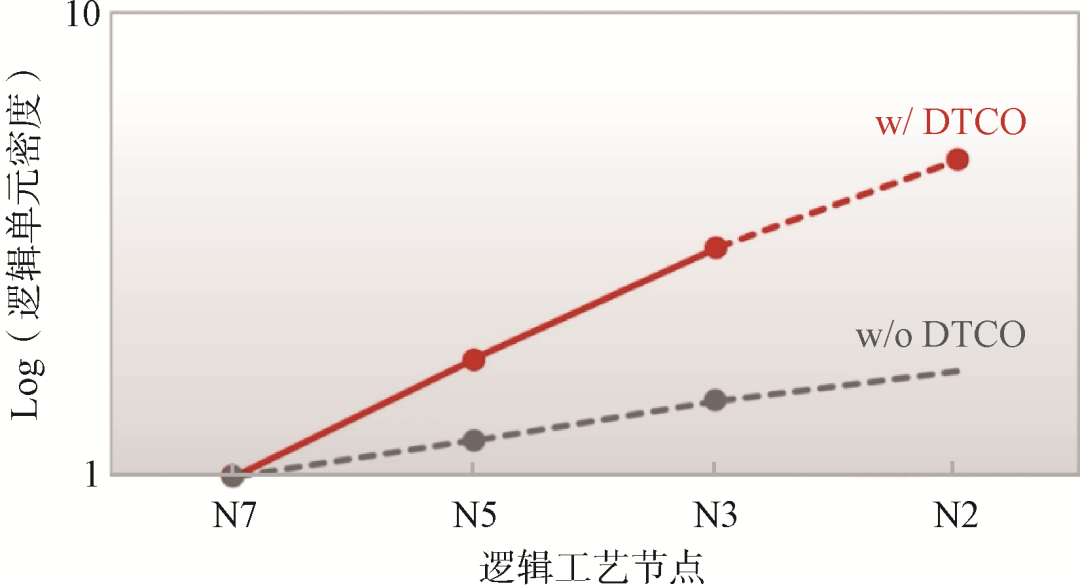

3.3設(shè)計工藝協(xié)同優(yōu)化

隨著先進技術(shù)節(jié)點工藝復(fù)雜度的持續(xù)演進,工藝之間的關(guān)聯(lián)耦合變得越來越明顯,開發(fā)工藝的思路要從單一步驟轉(zhuǎn)變到系統(tǒng)考慮。以環(huán)柵器件中的源漏外延工藝為例,因為內(nèi)側(cè)墻的存在使得外延SiGe很難做到較低的層錯缺陷,進而導(dǎo)致無法滿足PMOSFET對溝道應(yīng)力的要求。但是從工藝整合的角度出發(fā),一種后柵單擴散隔斷(Post-gate Single Diffusion Break)的工藝流程即使在源漏外延SiGe中存在一定的缺陷,溝道中的應(yīng)力卻可以得到很好地增強,從而提升PMOSFET的器件性能。在單元電路的開發(fā)上,更是不能局限于單個器件性能的提升,而要著眼于整個系統(tǒng)性能的全局優(yōu)化。在環(huán)柵器件的靜態(tài)隨機存取存儲器(SRAM)設(shè)計中,在單個器件之外,要充分利用環(huán)柵器件Fin寬可調(diào)的獨特性進行上拉(Pull-up)、下拉(Pull-down)和選擇(Select)晶體管的匹配優(yōu)化;另外選擇晶體管上的后段工藝(Back End of Line, BEOL)電阻對SRAM的噪聲容限和讀寫速度都有很顯著的影響。面向環(huán)柵器件中未來很有潛力的背面供電(Buried Power Rail)、互補場效應(yīng)晶體管(Complementary Field-Effect Transistor, CFET)技術(shù),以及3D封裝,要進行設(shè)計工藝協(xié)同優(yōu)化(Design Technology Co-Optimization, DTCO),優(yōu)化系統(tǒng)PPA(Performance,性能;Power,功耗;Area,面積),在更先進的制造工藝中提出重要的架構(gòu)創(chuàng)新。DTCO的核心目的就在于定義真正有價值的調(diào)整,超越單純的幾何微縮,進而達成提升性能、降低功耗和面積的目標(biāo)。根據(jù)臺積電提供的數(shù)據(jù),在3 nm節(jié)點及以下工藝,DTCO可以帶來超過100%的集成密度提升,如圖11所示。

圖11臺積電在先進CMOS工藝中使用DTCO對提升邏輯器件集成密度的影響

(來源:http://www.semiinsights.com/s/electronic_comonents/23/40279.shtml)

4

發(fā)展建議

先進CMOS制造工藝即將進入全新一代的環(huán)柵器件時代,在溝道形成、內(nèi)側(cè)墻、寄生溝道、源漏寄生電阻/電容,以及N/P電流匹配等關(guān)鍵技術(shù)領(lǐng)域面臨著巨大挑戰(zhàn),同時也給核心工藝裝備、在線工藝檢測技術(shù),以及DTCO平臺的自主發(fā)展帶來了機遇。

(1)裝備廠商在單一工藝開發(fā)之外一定要加快建設(shè)形成工藝整合能力(包括工藝整合技術(shù)團隊以及配套實驗線),這樣可以大大加快內(nèi)部工藝迭代的進度,更重要的是可以面對越來越復(fù)雜的工藝流程提供系統(tǒng)解決方案,在先進工藝模塊上給芯片制造企業(yè)提供更大的技術(shù)支持。

(2)芯片制造企業(yè)面向工藝裝備廠商要更加開放,和裝備企業(yè)分享芯片制造中的具體工藝?yán)щy,共同改進工藝裝備并提升工藝水平。同時加強與電子設(shè)計自動化(Electronic Design Automation, EDA)公司、設(shè)計公司的合作,加快完善DTCO平臺的建設(shè);同時要特別重視在線工藝檢測的技術(shù)和裝備開發(fā),工藝數(shù)據(jù)的積累和分析,提升先進工藝的制造水平和良率。

(3)裝備廠商和芯片制造企業(yè)要加強與高校實驗室的實質(zhì)合作,夯實基礎(chǔ)研究,開發(fā)和探索新技術(shù),在合作中培養(yǎng)人才,實現(xiàn)技術(shù)和人才的積累。

5

結(jié)束語

先進CMOS工藝技術(shù)是高性能計算芯片的保障,也是集成電路產(chǎn)業(yè)保持領(lǐng)先的關(guān)鍵點。我們要沉下心來,積累技術(shù)和經(jīng)驗,鼓勵和促進產(chǎn)業(yè)鏈上的技術(shù)合作。最重要的是要培養(yǎng)一大批踏實能干的年輕一代高端人才,努力發(fā)展并建立自主可控的核心技術(shù)和產(chǎn)業(yè)鏈,實現(xiàn)中國集成電路產(chǎn)業(yè)的高質(zhì)量發(fā)展。

審核編輯 :李倩

-

CMOS

+關(guān)注

關(guān)注

58文章

5723瀏覽量

235640 -

晶體管

+關(guān)注

關(guān)注

77文章

9701瀏覽量

138370 -

寄生電容

+關(guān)注

關(guān)注

1文章

293瀏覽量

19246

原文標(biāo)題:綜述與述評 | 張衛(wèi):先進CMOS制造工藝的技術(shù)演進及自主發(fā)展思考

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產(chǎn)工藝

《大話芯片制造》閱讀體會分享_1

最新CMOS技術(shù)發(fā)展趨勢

鋅銀電池的制造工藝

HV-CMOS工藝制程技術(shù)簡介

雙極型工藝制程技術(shù)簡介

藍牙傳輸技術(shù)的演進與發(fā)展

深圳恒興隆|制造業(yè)的新星:高光超精電主軸的崛起...

什么是BCD工藝?BCD工藝與CMOS工藝對比

旋轉(zhuǎn)花鍵的制造工藝

Nvidia芯片工藝先進封裝演進洞察

CMOS工藝技術(shù)的概念、發(fā)展歷程、優(yōu)點以及應(yīng)用場景介紹

FS6212系列是以 CMOS 工藝制造的高精度超快響應(yīng)低壓差線性穩(wěn)壓器

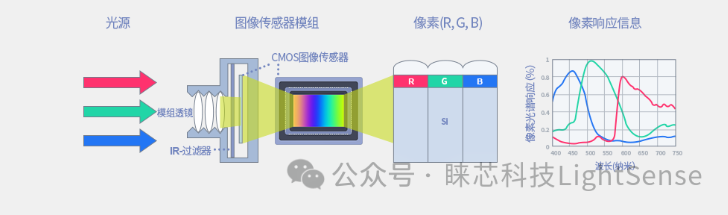

CMOS圖像傳感器的制造工藝

張衛(wèi):先進CMOS制造工藝的技術(shù)演進及自主發(fā)展思考

張衛(wèi):先進CMOS制造工藝的技術(shù)演進及自主發(fā)展思考

評論