項目背景:項目為一個云端運算的產(chǎn)品,所有的高速和低速信號都要進行信號完整性測試,其中包括高速串行信號PCI-Express Gen1( 簡稱PCIe Gen1)。PCIe Gen1信號分為CEM和base兩種情況,CEM的測試可以使用 PCI-sig協(xié)會的fixture直接進行測試;base的測試直接使用探頭探測最終端的測試點,這樣就會帶來一個問題,如何才能測試到芯片的的最終端?因為,信號的互連通道不僅僅包含了PCB走線,還包含了芯片內(nèi)部的布線,一般我們認為測量到芯片內(nèi)部的Die才算最終端。

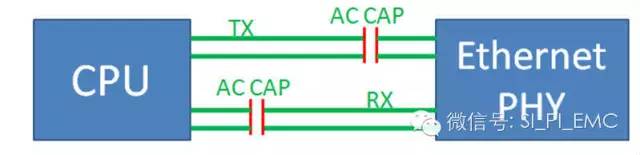

該項目的PCIE 1.0是屬于PCIe base的,互連CPU與以太網(wǎng)PHY,如下圖1所示:

圖1 原理框圖

所以測試的時候,需要將probe探測到最終端,但是對于目前示波器測試而言,都只能測試到芯片的引腳上,沒有辦法探測到最終端的Die上。

測試設備:示波器(16GHz),測試探頭(16GHz),萬用表,烙鐵,校準板,網(wǎng)絡分析儀(帶TDR選件)

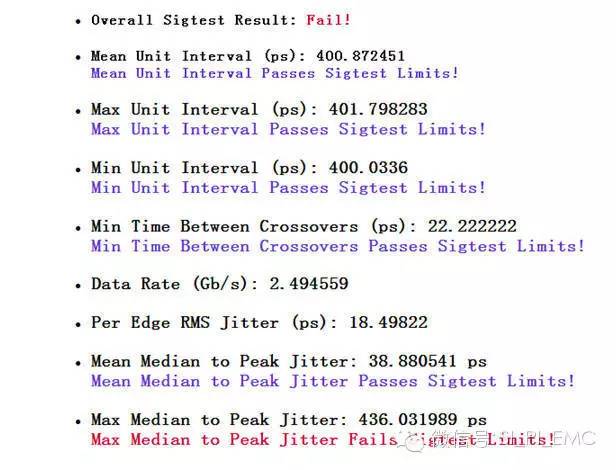

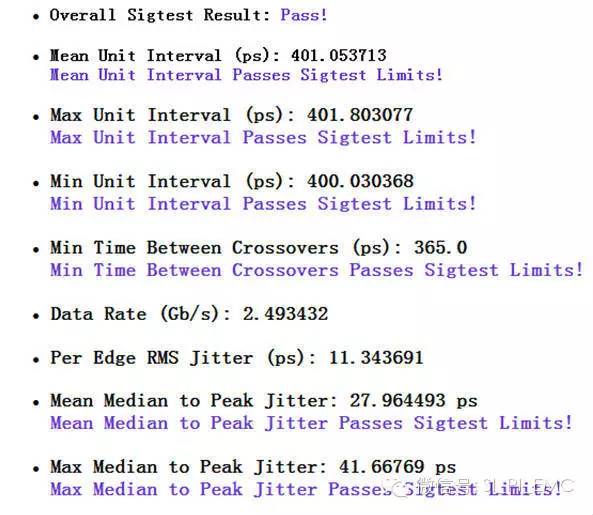

問題描述以及分析:在測試接收端(RX)的信號時,以太網(wǎng)PHY發(fā)送信號,測試點選在CPU BGA下方的過孔上,信號沒有任何問題,眼圖和jitter都能滿足PCI-sig協(xié)會規(guī)范。測試發(fā)送端(TX)時,CPU發(fā)送信號,以太網(wǎng)PHY是接收端,由于PHY芯片封裝是QFP的,所以探頭點在引腳上。得到測試波形后,在分析軟件中分析波形,能通過眼圖模板測試規(guī)范,但是發(fā)現(xiàn)jitter過不了規(guī)范,重復幾次測試都是如此。再校準示波器和測試探頭再測試,依然如此。每次得到的結果如下圖3所示:

圖3 眼圖和jitter測試

結果顯示fail,而且是jitter fail。 jitter的問題一般都是比較麻煩的。從眼圖上看,眼圖的軌跡很稀松,也不是很光滑。

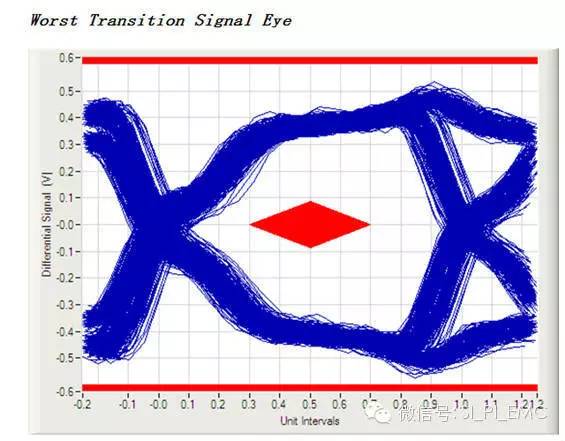

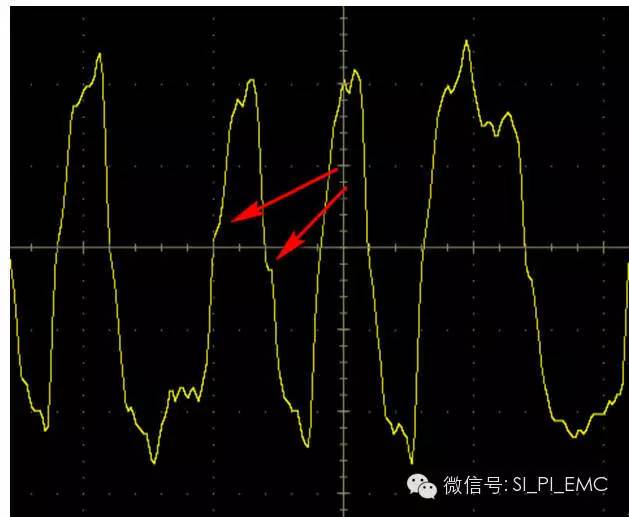

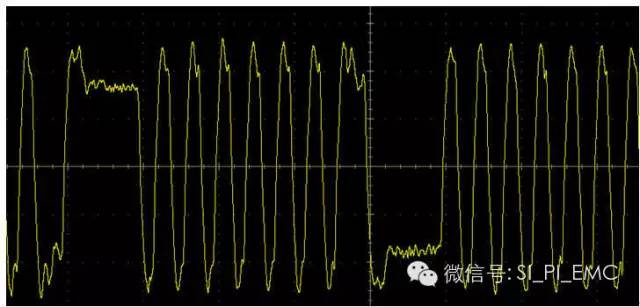

將示波器的原始波形展開放大觀察,發(fā)現(xiàn)信號在上升和下降沿上出現(xiàn)了非單調(diào)的現(xiàn)象,對比眼圖,正好能對應上眼圖的交叉點處,如下圖4所示。

圖4 測試波形圖

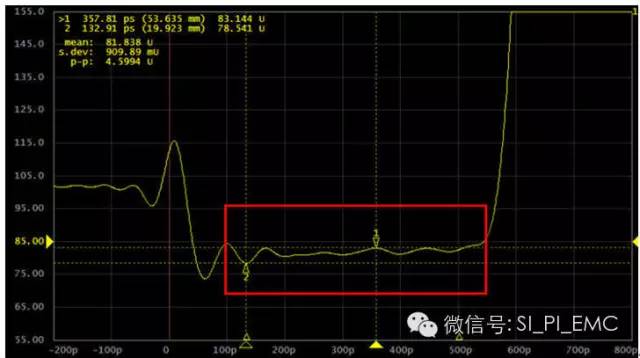

一般非單調(diào)是因為阻抗不連續(xù)造成的。在PCB生產(chǎn)完成之后,我們對高速信號進行了阻抗的測試,對應的阻抗如下圖5所示:

圖5 阻抗測試曲線

上圖所示,這是使用網(wǎng)絡分析儀的TDR軟件測試得到的結果,信號線的設計阻抗為85ohm,有上圖5紅色框曲線所示,測試阻抗都能滿足在85ohm +/-10以內(nèi)的設計要求,可以認為其阻抗一致性比較好。不存在信號線阻抗突變的問題。如果阻抗沒有突變,一般在測試時出現(xiàn)這種非單調(diào)的情況,大多時候都是由于測試不在最終端所造成的(當然,最終端的die達不到,那么至少要求stub最短)。

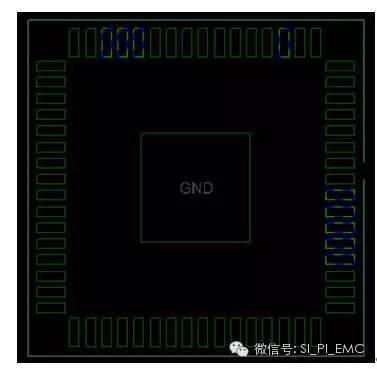

項目使用的以太網(wǎng) PHY封裝如下圖6所示:

圖6 芯片封裝

這種封裝,很多時候其芯片內(nèi)部走線比較長,那么在測試的時候,其探測點在芯片的引腳上,那么內(nèi)部的走線就是一段stub,顯然,這一段stub很長,由于stub的作用,很可能最終導致其測試時信號波形出現(xiàn)非單調(diào)。進而影響眼圖、jitter等信號完整性的表現(xiàn)。

解決方案:分析了相關的原因后,懷疑就是在測試時芯片內(nèi)部的走線形成了stub,那么在測試把芯片去掉,在PCIE信號兩個引腳上分別焊接上50ohm的端接電阻,類似PCIE CEM的測試一樣,探頭連接在電阻端進行測試,這樣就不會存在stub,如果信號波形是好的,都能滿足眼圖、jitter等性能指標,那么懷疑是芯片內(nèi)部的走線引起的stub導致的反射,這就是成立的,這樣的情況可以認為PCIe的互連通道的信號完整性能滿足產(chǎn)品和規(guī)范的要求。

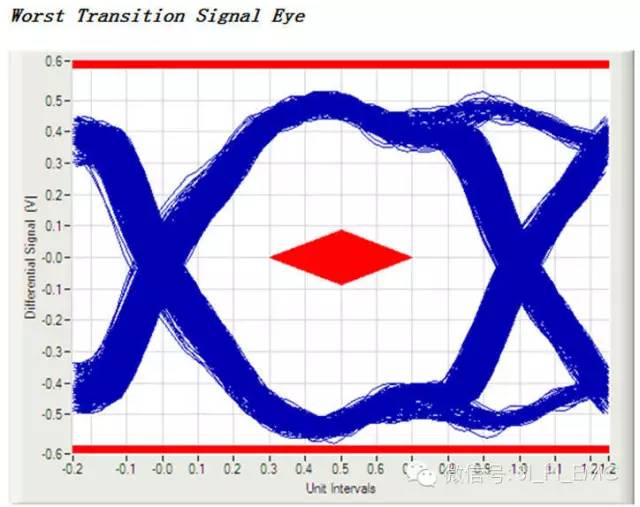

芯片去掉之后,端接上電阻,得到眼圖和jitter分析結果如下圖7所示:

圖7 改變后測試眼圖和jitter

下圖8是端接后展開的波形,在上升和下降沿處都沒有觀察到非單調(diào)性。

圖8 改變后測試波形圖

綜上所述,此處PCIe Gen1測試信號完整性fail的問題是由于測試點不在最終端測試所造成的結果,可以推斷此PCIe互連通道的信號完整性沒有問題。

如果其它的測試遇到這樣的情況也是一樣,特別是一些項目的芯片很大,像FPGA那樣的,如果需要測試的信號線其能探測的測試點離最終端(Die)比較遠,在測試的時候又出現(xiàn)了問題,這個時候就需要考慮是否是由于測試點不在最終端(或最靠近最終端)造成的。

審核編輯:郭婷

-

芯片

+關注

關注

456文章

50879瀏覽量

424137 -

pcb

+關注

關注

4319文章

23108瀏覽量

398208

原文標題:[案例]PCIE jitter測試問題分析以及解決方案

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

聽懂什么是信號完整性

12月20日線上講堂|聽懂什么是信號完整性

高速PCB的信號完整性、電源完整性和電磁兼容性研究

什么是信號完整性

構建系統(tǒng)思維:信號完整性,看這一篇就夠了!

DDR4信號完整性測試要求

信號完整性測試 如何才能測試到芯片的的最終端

信號完整性測試 如何才能測試到芯片的的最終端

評論