誕生50幾年來,摩爾定律一直是半導體行業的主要推動力。當我們談論摩爾定律時,所談的不僅是一項晶體管數量相關的經驗法則,更是一本為行業公認的經濟賬,一種足以驅動各大芯片制造商未來產品戰略的方法論。

片上系統(SoC)作為完美踐行了這一法則的模范架構,在多年中幫助很多企業在商業上取得了巨大的成功。但在進入10nm制造節點之后,SoC的量產成本逐漸突破了市場所能承受的極限,其市場表現也與當初的預測愈行愈遠。當然,摩爾定律也并非一成不變,它需要有更符合未來創新需求的靈活商業模式,以適應更長時間的增長。在這樣的趨勢中,越來越多的芯片廠商開始從SoC架構轉向Chiplet。

SoC:良率之下的成本危機

在半導體行業,良率已經成了與制程同等重要的行業性難題,生產大型SoC之所以難以為繼,核心原因就是良率降低引起的硬件成本飆升,全球三大半導體代工廠無不為良率困擾。誰贏得了良率,誰就會贏得未來。簡單的說,芯片良率就是晶圓上合格芯片數量與芯片總數的比值,這個數值越大,說明有用芯片數量越多,浪費越少,成本越低,利潤越高。芯片尺寸和制程都會直接影響良率。與面積較小的芯片相比,大型單一芯片更容易出現不可逆轉的缺陷。以臺積電5nm工藝晶圓測試為例,18mm2芯片的平均良率約為80%,而100mm2芯片的良率則會驟降至32%。 先進工藝的發展也會進一步引發良率的挑戰。隨著工藝節點不斷縮小,足以引發芯片嚴重問題的缺陷尺寸也越來越小。例如,對于45nm制造節點,<9nm的缺陷是可接受的,但對于5nm制造節點,僅僅1nm的缺陷就可能讓芯片報廢。此外,隨著制造工藝提升,光刻技術的制造成本也越來越高,從而增加了成本。

增加芯片尺寸的芯片成本變化,先進工藝節點上的芯片制造的良率問題,已成為全球三大代工廠的競爭焦點。三星基于GAA結構的3nm制程芯片正式進入量產,由于其良率未能達到預期,其晶圓代工業務飽受爭議(有消息稱,三星3nm工藝良率僅在10%到20%之間)。此外,英特爾原計劃于2021年底上市的7nm芯片,也因工藝存在缺陷,導致良率下降,發布時間推遲6個月。無法停步的良率危機表明半導體行業已經達到了一個臨界點,而 Chiplet就是下一個階段的答案。

Chiplet成本方程①

面積減法,良率提升

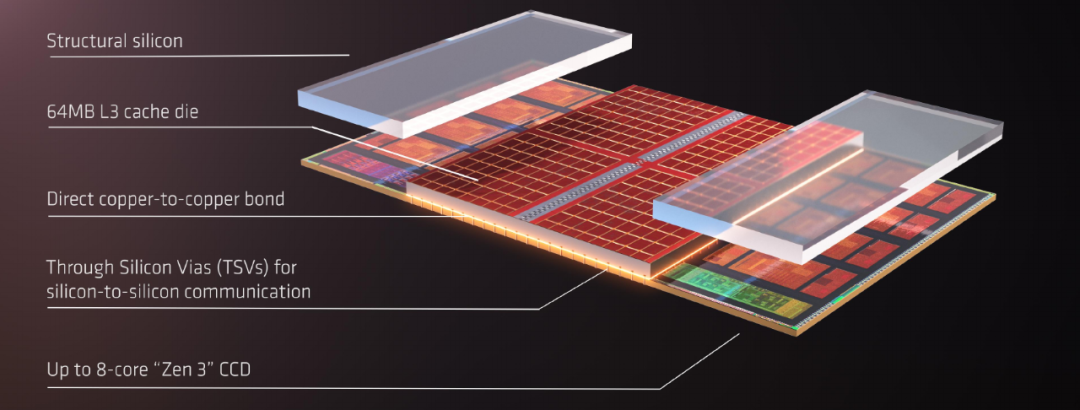

傳統的SoC通常將多個負責不同類型計算任務的計算單元,通過光刻的形式制作到同一塊晶圓上。而Chiplet將復雜芯片拆解成一組具有單獨功能的小芯片單元die,再通過die-to-die將模塊(Top dies)芯片和底層基礎(Base die)芯片封裝組合在一起,減少整個芯片面積,以提升良率。 通過使用與SoC相同的標準光刻程序,芯片制造商可以用同樣的晶圓生產出更多面積更小,良率更高的Chiplet,并進行單獨的KGD(Known good die)測試,重新組裝并封裝到完整的芯片中。對于與SoC情況相同的故障分布,Chiplet上因缺陷導致的廢棄約為SoC的4分之1。

AMDEPYC AMD最早在其第一代 EPYC 數據中心處理器重采用了Chiplet方案,“基于AMD內部良率模型和使用成熟工藝的缺陷密度數據,我們估計四個chiplet設計的最終成本僅為單片架構的約0.59。”

Chiplet成本方程②

制程加法,良率提升

除了良率問題,先進制程的費用也是制約芯片成本的一大因素。傳統的SoC,所有模塊都需要在相同工藝節點下制作。然而,并非所有芯片都適用于先進制程。例如,射頻前端作為模擬芯片,其特征尺寸的縮小并不能帶來性能的提升,在先進制程下,單位芯片成本不降反升。在Chiplet架構中,不同的模塊可以被拆解出來,通過更適合的工藝節點來制造。如在運算核心采用先進制程,射頻前端等模塊采用成熟制程。設計師還可以將大型SRAM存儲器從計算邏輯芯片中拆分出來,優化其制程,能帶來更好的整體性能指標提升。由此可以大幅減少芯片對先進制程的依賴,從而降低芯片的量產成本。

不久的將來,芯片制造商將有望從不同代工廠處采購不同工藝、甚至不同材質生產的標準化Chiplet,快速把它們組裝成一個SoC級的大芯片,以進行最終驗證和測試,就像今天SoC設計師從不同供應商那里采購IP一樣。

Chiplet成本方程③

設計難度減法,IP硬核復用

在芯片開發中,制造商不僅要面臨與芯片尺寸和工藝節點提升帶來的成本挑戰,芯片的設計成本也在不斷上漲。芯片設計成本通常包含工程師的人力成本、EDA等開發工具、設備、場地、IP等費用。 研發一款傳統SoC芯片,需要設計出芯片上的所有模塊,不但設計周期漫長,設計費用也居高不下。而Chiplet架構中,芯片在設計層面被分為核心芯粒和非核心芯粒兩部分,客戶可以直接向第三方公司采購非核心芯粒,從而簡化芯片設計難度,提高設計成功率并縮短設計周期。此外,這些成熟的Chiplets,基于KGD(已知良品芯片)設計,可廣泛復用于其他芯片中,在保證良率的前提下繼續提升單顆芯片性能。

Chiplet成本方程④

上市周期減法

設計周期與上市時間息息相關。在激烈的市場競爭中,僅僅有一個好產品是不夠的,企業必須要竭盡所能縮短上市周期,以確保競爭優勢。相比傳統SoC原型設計之后“一個也不能少”的軟硬件協同驗證、后端與物理設計、流片制造、封裝測試全流程,Chiplet是一個已經走完了設計、制造、測試流程的成品小裸片,僅需要做一次封裝就可以使用起來。通過組合現有KGD與可配置硬件,針對應用提供定制化解決方案,Chiplet可以在保障、提升芯片性能的情況下,滿足快速TTM需求(Time to market),幫助企業在競爭中贏得優勢。

芯片研發已然成了全球最昂貴的賽道,從芯片架構到工藝制程再到設計模式,每一個潛在變量都會引發最終成本的雪崩。Chiplet的出現,給SoC主導多年卻日漸式微的半導體行業開辟了一條新的通道。而這條新路的出現絕非偶然,它是行業巨頭們耗費多年精力,在芯片功耗、性能、成本、上市周期幾者間找到的絕佳平衡,是為了讓行業賴以生存的經濟規律持續下去積極為之的變化。從SoC走向Chiplet,不是為放棄,是為了讓摩爾定律涅槃重生。

審核編輯:郭婷

-

芯片

+關注

關注

455文章

50740瀏覽量

423297 -

soc

+關注

關注

38文章

4163瀏覽量

218184 -

奇異摩爾

+關注

關注

0文章

49瀏覽量

3405 -

先進封裝

+關注

關注

2文章

403瀏覽量

241 -

芯粒

+關注

關注

0文章

59瀏覽量

134

原文標題:Chiplet,芯片成本加減法

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文看懂SoC的架構

Cadence推出基于Arm的系統Chiplet

Chiplet技術有哪些優勢

最新Chiplet互聯案例解析 UCIe 2.0最新標準解讀

SOC芯片在人工智能中的應用

從芯片到系統:SOC如何重塑電子產業

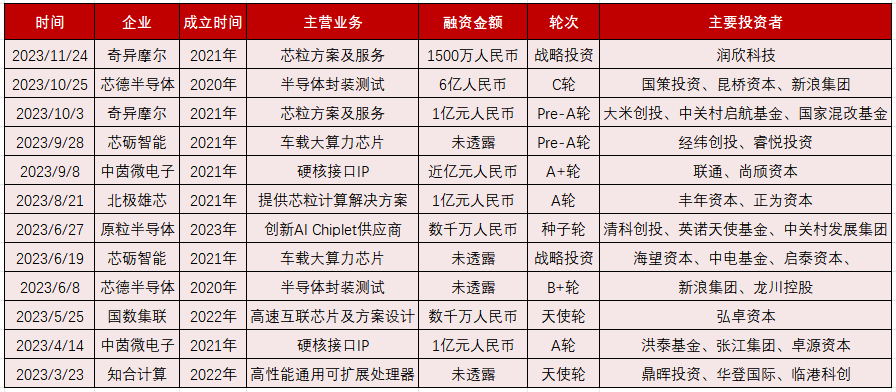

2023年Chiplet發展進入新階段,半導體封測、IP企業多次融資

芯片廠商從SoC架構轉向Chiplet

芯片廠商從SoC架構轉向Chiplet

評論