提到位置約束,我們會想到手工布局的方式,即畫Pblock,將指定模塊放入相應Pblock內,這既是面積約束又是位置約束,但顯然這種約束是較為具體的位置約束。這種方式需要工程師有一定的經驗,有時還需要借鑒參考Vivado之前的布局結果,換言之,我們確定的Pblock位置未必是工具認為的最佳位置。對于特定的底層單元,例如RAMB36K或DSP48,可通過屬性LOC指定其具體位置(site的位置),顯然這也是非常具體的位置約束。那么是否可以做模糊的位置約束?即希望指定的模塊彼此靠得近一些,或一些底層單元在指定區域(無需指定具體site的位置)。答案是肯定的。這里我們就介紹幾個屬性。

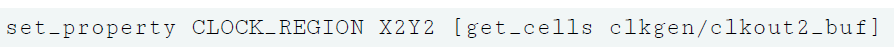

CLOCK_REGION 屬性CLOCK_REGION可用于指定時鐘緩沖器如BUFG的位置,不同于屬性LOC,/CLOCK_REGION僅確定指定時鐘緩沖器位于哪個時鐘區域,這個區域內會有多個時鐘緩沖區可供選擇。CLOCK_REGION可以在XDC中使用,方法如下:

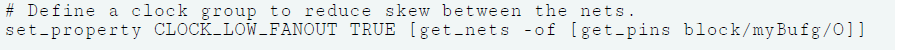

在大多數情況下,時鐘緩沖器由全局時鐘管腳、MMCM/PLL或GT*_CHANNELs驅動,這種情況下,Vivado會自動確定時鐘緩沖器的位置,無需人工干預。 CLOCK_LOW_FANOUT 如果某個時鐘所驅動的負載較小(時鐘扇出較低),那么可以對時鐘緩沖器輸出端所連接的網線施加屬性CLOCK_LOW_FANOUT,并將其值設置為TRUE,這樣工具將嘗試將這些負載放置在一個時鐘區域內,但用戶無需指定到底是哪個時鐘區域。具體使用方法如下:

這里需要注意:這個屬性的施加對象是網線net,這個net應是時鐘緩沖器輸出端所連接的net。此外,如果這些負載無法放置在一個時鐘區域內(資源不夠),那么工具將會忽略此約束。

審核編輯:湯梓紅

-

緩沖器

+關注

關注

6文章

2037瀏覽量

46640 -

Vivado

+關注

關注

19文章

830瀏覽量

68260

原文標題:Vivado里如何使用模糊性的位置約束?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

VIVADO時序約束及STA基礎

vivado約束參考文檔

Vivado忽略了約束文件

ISE約束導入vivado總共分幾步

Vivado進行時序約束的兩種方式

Vivado中XDC文件的約束順序

vivado多時鐘周期約束set_multicycle_path使用

Vivado設計約束功能概述

Vivado綜合階段什么約束生效?

Vivado的Implementation階段約束報警告?

Vivado Design Suite用戶指南:使用約束

Vivado使用小技巧

評論