導讀

本文將概要介紹數字芯片設計的十大流程,以及各大流程中使用的主流EDA軟件。

芯片在我們的生活和工作中無處不在。

例如,交通智能卡就嵌入了一顆帶有微處理器、儲存單元、芯片操作系統的芯片;而手機的主板則集成了數百顆芯片,有的負責無線電收發、有的負責功率放大、還有的負責存儲照片和文件、處理音頻,完成指紋、虹膜、面部的識別。

當然,手機中最重要,也是價格最昂貴的還屬CPU,它是手機的控制中樞和邏輯計算的中心,通過運行存儲器內的軟件及數據庫來操控手機。

根據處理的信號類型不同,芯片可以分為數字芯片和模擬芯片。

要制造出芯片,首先要完成芯片設計。

本文將概要介紹數字芯片設計的十大流程,以及各大流程中使用的主流EDA軟件。

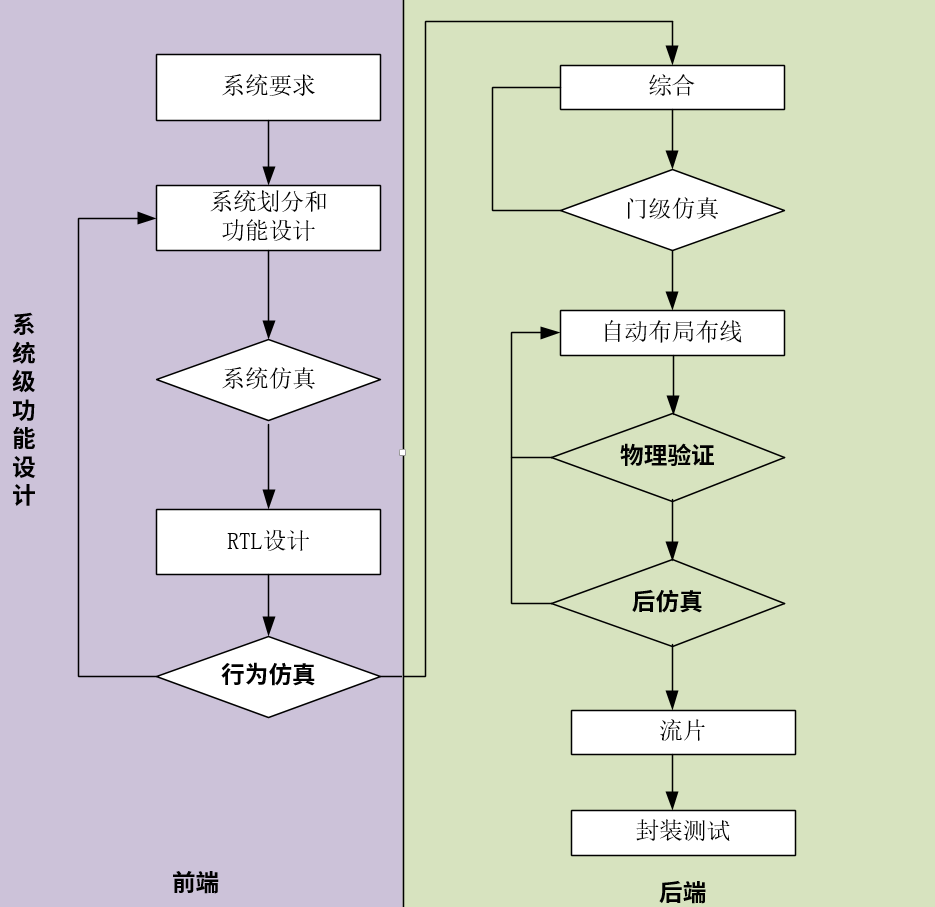

芯片設計可以分為前端設計(即邏輯設計)和后端設計(即物理設計)。前端設計包括以下四個步驟:

前端設計

(1)算法或硬件架構設計與分析

在明確芯片的設計需求之后,系統架構師會把這些市場需求轉換成芯片的規格指標,形成芯片的Spec,也就是芯片的規格說明書。

這個說明書會詳細描述芯片的功能、性能、尺寸、封裝和應用等內容。

系統架構師會根據芯片的特點將芯片內部的規格使用劃分出來,規劃每個部分的功能需求空間,確立不同單元間聯結的方法,同時確定設計的整體方向。

這個步驟對之后的設計起著至關重要的作用,區域劃分不夠的,無法完成該區域內的功能實現,會導致之前的工作全部推翻重來。

設計出來的東西,必須能夠制造出來,所以芯片設計需要與產業鏈后端晶圓的制造和封裝測試環節緊密合作,工程師不但需要考慮工藝是否可以實現相應電路設計,同時需要整合產業鏈資源確保芯片產品的及時供給。

這里的算法構建會用到編程語言(MATLAB,C++, C,System C, System Verilog等),對于不同類型的芯片,工程師們會有不同的偏好選擇。

(2)RTL code(Register Transfer Level,寄存器傳輸級)實現

由于芯片的設計及其復雜,設計人員并不在晶體級進行設計,而是在更高的抽象層級進行設計。

RTL實現就是根據第一步的架構設計結果,轉化為Verilog HDL或VHDL語言,這兩種語言是世界上最流行的兩種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的硬件編程語言,可以用于表示邏輯電路圖、表達式等邏輯輸出。

所以,可以理解為上一步是統籌規劃,第二步是具體去實現,設計工程師們通過敲一行行代碼,去實現電路的功能。

輸出結果轉化為Verilog HDL或VHDL語言。

(3)編碼檢查與分析

這一步就是檢查代碼有沒有錯誤,保證代碼不會出現什么歧義導致實現結果和設計目的不一致。

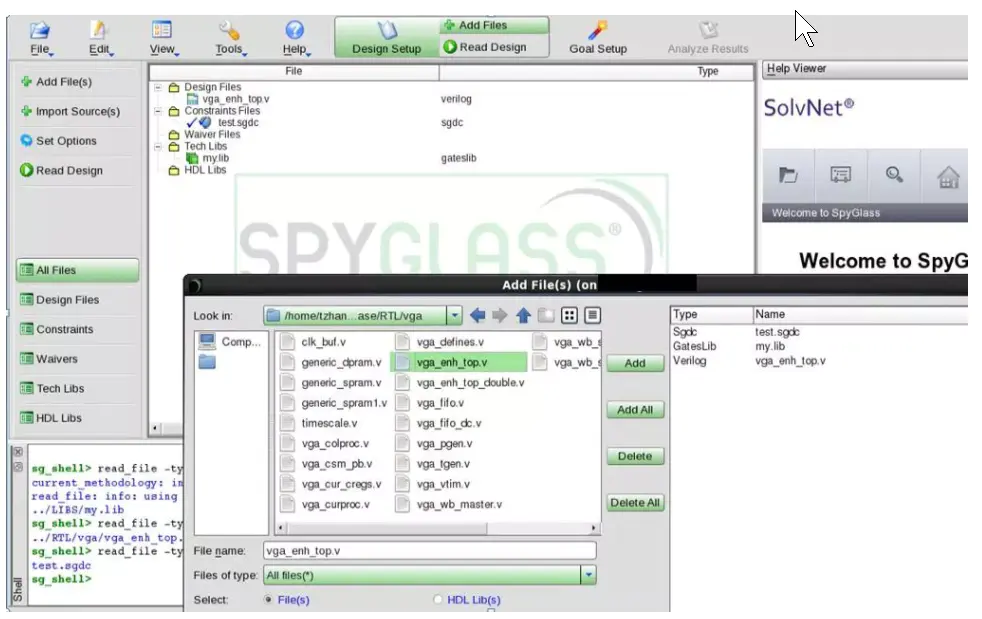

一般來說,最常用的編碼檢查工具就是Synopsys的Spyglass,這個工具最主要檢查的內容有兩個,一個是Lint檢查,一個是CDC (Clock Domain Crossing,跨時鐘域)檢查。

Lint檢察不僅可以檢測出許多編譯器編譯過程中的錯誤,還可以關聯很多文件進行錯誤的檢查和代碼分析;CDC檢查則是對電路設計中同步電路設計的檢查,在大型電子電路設計中,設計人員很難設計出整個大型的同步電路,而只能根據電路邏輯功能,劃分為多個同步電路部分,由不同的時鐘域控制。

這些部分可能存在重疊,這會導致重疊部分的觸發器狀態變化不能在統一的時鐘作用下完成,從而導致電路出現亞穩態。

電路出現亞穩態會讓組合邏輯電路輸入狀態不可頂知,甚至產生突然的跳變,因此需要進行CDC檢查。

SPYGLASS截圖,圖片源自網絡

(4)功能驗證

這一步是驗證芯片設計與預定的設計需求是否相符的關鍵步驟,主要是驗證電路設計邏輯功能的正確性,而非電路的物理特性(后面的步驟會講到物理驗證)。

數字仿真器是數字集成電路邏輯功能驗證的主要手段。

隨著超大規模集成電路的高速發展,高性能數字仿真器已經成為數字集成電路設計與驗證中必備的一環。

近年來數字仿真器技術發展很快,當今主流數字仿真軟件可以支持數十億晶體管規模的超大規模集成電路的邏輯功能進行高效精確的仿真驗證。

為了保證芯片的穩定性,這個階段的過程時間會持續數月。

EDA工程師常用的EDA工具是Mentor(西門子EDA)的Modelsim、Synopsys的VCS和Candence 的NC-Verilog。

功能仿真驗證

在整個芯片設計流程中的位置(黑體)

后端設計

(5)邏輯綜合(Synthesis)

從這一步開始,就進入芯片設計的后端設計(物理設計)階段了。

主要負責將RTL code轉換為實際后端使用的Netlist(網表,包含了RTL中所有的邏輯信息,以及離散傅立葉變換、門控時鐘和I/O等)。

網表的質量對芯片的布局布線工作起到決定性作用。

該過程需要考慮工藝的電特性和物理特性等因素,要盡可能做到Performance(性能)、Power(功耗)和Area(面積)的PPA優化。

Synthesis的質量在一定程度上取決于綜合軟件的性能,業界流行的兩個邏輯綜合工具是Synopsys的Design Compiler和Cadence的Genus,綜合工程師的一個基本要求便是熟練的掌握兩個工具的使用方法。

(6)布局布線(PD)

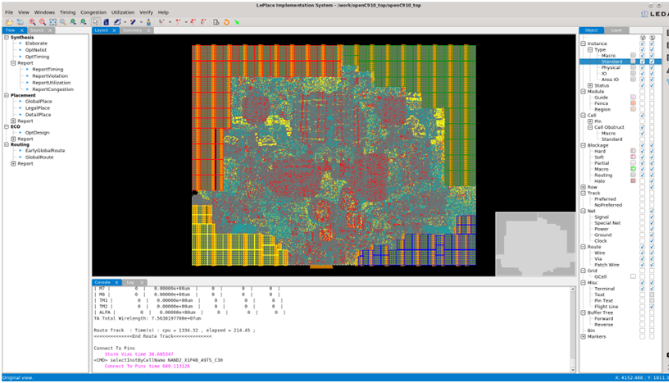

布局布線是數字后端中占比最大的工作,主要就是把網表轉化成GDSII流格式(這是一種用于集成電路版圖的數據轉換的標準數據文件庫格式,其中含有集成電路版圖中的平面的幾何形狀、文本或標簽等有關信息,由層次結構組成),確定各種功能電路的擺放位置。

PD的步驟包括Floorplan(布局規劃)、Place(功能電路的擺放)、CTS(時鐘綜合)、Optimize(優化)、Route(布線)和ECO(工程變更)等,確保各個模塊滿足時序和物理制造的要求。

這個步驟是后端設計中最核心的工作。

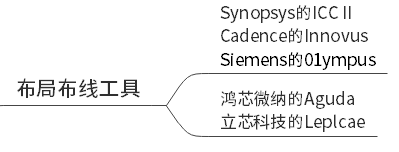

布局布線對工具的依賴程度較強,而且工具操作相對來說較為復雜。業界較為常用的是Cadence的Innovus和Synopsys的ICC。

國內外布局布線工具廠商

Leplace圖形界面

(7)靜態時序分析(STA)

STA(Static Timing Analysis,靜態時序分析)是芯片后端設計中的重要步驟。

芯片上有海量的極其微小的金屬元器件,這些元器件的大小不一,通過引線流過這些元器件的延時會有不同,由于元器件過于微小,芯片的布局布線肯定會受到這些不同大小元器件和之間引線的各種限制,而靜態時序分析則是模擬各種元器件間的互聯和各種不同狀況的仿真,找出存在的各種問題。

靜態分析需要保證芯片設計中所有的路徑,滿足內部時序單元對建立時間和保持時間的設計要求。

也就是說無論信號的起點是什么,信號都可以被及時地傳遞到該路徑的終點。同時,也要滿足電平跳變時間、電容、噪聲、等要求。

STA需要制定整個芯片的時序約束約束文件,選擇芯片需要Signoff(簽發)的Corner(工作范圍)以及全芯片的Timing(時序) ECO流程,這個步驟的難度要求很高。

STA階段應用較廣的是Synopsys的Primetime和Cadence的Tempus軟件。值得一提的是國內鴻芯微納的ChimeTime,它是一種靜態時序簽核工具,提供了SPICE仿真精度的簽核結果。

(8)物理驗證

物理驗證也是流片(即試生產)前的一項重要事項。

如果物理驗證有錯,那芯片生產就會失敗。在布局布線工具中,真正的物理驗證需要檢查到器件底層。

因此,物理驗證需要將金屬層和底層金屬合并到一起,進行全芯片的DRC(設計規則檢查)。

同時,還需要做全芯片的LVS(版圖與原理圖一致性檢查),ERC(電氣規則檢查),確保芯片沒有違反任何物理設計規則。

物理驗證的主要工具在Mentor(西門子EDA)的Calibre中進行,Calibre也是業界標準的物理驗證工具。

(9)功耗分析(PA)

功耗分析也是芯片簽發的重要步驟,功耗分析的兩大任務是分析IR drop(電壓降)和EM(電遷移)。

及時將結果反饋給布局布線任務組,讓他們及時修改后端設計圖,解決設計中潛在的問題。

功耗分析常用的軟件有Ansys公司的Redhawk,以及Cadence公司的Voltus和Synopsys公司的Ptpx。

(10)時序仿真

該步驟是對芯片實際工作時的狀態進行仿真,即后仿真,來驗證功能是否正常。

時序仿真使用布局布線后器件給出的模塊和連線的延時信息,在最壞的情況下對電路的行為進行實際評估。

時序仿真使用的仿真器和上述第四步的功能仿真使用的仿真器是相同的,區別在于功能仿真是在布線前進行,僅僅關注輸出和輸入的邏輯關系是否正確,不考慮時間延時信息;而時序仿真是在布線后進行,不僅關注輸出和輸入的邏輯關系是否正確,同時還計算了時間延時信息。

總結下來,數字芯片的前端設計是邏輯設計,用邏輯電路實現其預期的功能。

后端部分則是對前端設計的物理實現。芯片設計完成后,Fabless(芯片設計)公司一般會將設計結果以GDSII格式記錄的電路版圖數據交給Foundry(芯片代工廠)進行Tape-out(流片)了,也就是試生產。

為什么會叫Tape-out呢?因為在上世紀七八十年代,芯片的設計數據都是寫到磁帶或者膠片里傳給工廠,設計團隊將數據寫入磁帶叫Tape in,工廠讀取磁帶的數據叫Tape out,雖然隨著科技的發展,自動化集成電路版圖工具軟件早已代替了磁帶,但是這個叫法一直沿用下來了。

當Tape out完成后,芯片就可以正式開始生產了。

由于芯片的流片花費巨大,因此芯片的可靠性和可制造性,需要盡可能在設計階段就能確保。

主流EDA軟件的驗證和仿真功能十分完善,可以通過在各個階段不斷地進行驗證仿真,減少在流片中的錯誤,降低流片的成本,確保芯片的可靠性。

芯片設計非常專業,每一個設計階段涉及到的各種軟件種類繁多,雖然全球EDA軟件市場只有數百億美元的規模,但是它撬動的是萬億美元級的集成電路市場,因此,EDA軟件產業具有重要的戰略意義。

當前,我國高速重視發展工業軟件,國產EDA軟件迎來了發展的春天,我國的EDA市場正在全面發力,涌現出華大九天、概倫電子、廣立微、九同方、上海立芯、芯華章、芯愿景和鴻芯微納等知名品牌。雖然EDA領域的“卡脖子”問題對我國高端芯片的設計與制造產生了較大影響,但同時也為國產EDA軟件廠商帶來更大的市場機會。

通過更多芯片設計、制造和封裝測試企業在實踐中的應用,不斷為國產EDA軟件反饋應用需求和軟件改進需求,將迅速提升我國EDA軟件的技術水平。

審核編輯:劉清

-

matlab

+關注

關注

185文章

2977瀏覽量

230645 -

EDA軟件

+關注

關注

6文章

97瀏覽量

18714 -

模擬芯片

+關注

關注

8文章

629瀏覽量

51239 -

數字芯片

+關注

關注

1文章

110瀏覽量

18424

原文標題:數字芯片是怎樣設計出來的?

文章出處:【微信號:數字化企業,微信公眾號:數字化企業】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

華為發布2025智能光伏十大趨勢

佰維存儲榮獲十大數智化轉型創新企業

達實智能榮獲十大數字科技創新產品獎

瑞薩電子榮獲2024年度電機控制器十大主控芯片

數字設計ic芯片流程

華為發布5G-AA十大產品解決方案

“智能網聯汽車全球十大發展突破”在京發布

【「數字IC設計入門」閱讀體驗】+ 數字IC設計流程

中國信通院發布“2024云計算十大關鍵詞”

中國半導體產業的十大技術“瓶頸”解析

度亙核芯榮獲“2023年度中國十大光學產業技術”獎

介紹數字芯片設計的十大流程

介紹數字芯片設計的十大流程

評論