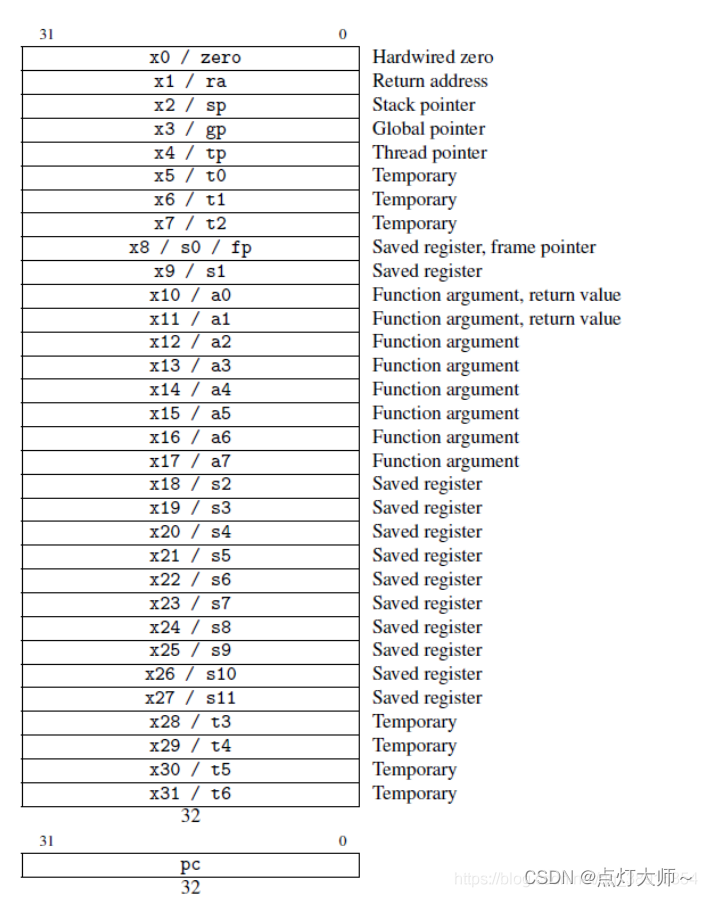

1、寄存器

RV32I有32個通用寄存器,以及一個PC寄存器。其中有一個通過硬件設置的值恒為 0 的 x0 寄存器

注:RISC-V的32個寄存器x0~x31是用0~31這些數字來表示。

2、基礎指令

RISC-V有六種基本指令格式:

每個字段名稱的含義:

- opcode (操作碼):指令的基本操作,這個縮寫是它慣用名稱。

- rd : 目的操作寄存器,用來存放操作結果。

- funct3 : 一個另外的操作碼字段。

- rs1 : 第一個源操作數寄存器。

- rs2 : 第二個源操作數寄存器。

- funct7 : 一個另外的操作碼字段。

- imm :立即數

2.1、R 型指令

字段:

| funct7 | rs2 | rs1 | funct3 | rd | opcode |

|---|---|---|---|---|---|

| 7位 | 5位 | 5位 | 3位 | 5位 | 7位 |

指令:

示例:

| 指令 | 示例 | 含義 |

|---|---|---|

| add | add a0, a1, a2 | a0 = a1 + a2 |

| sub | sub a0, a1, a2 | a0 = a1 - a2 |

| sll | sll a0, a1, a2 | a0 = a1 << a2 (低位補0) |

| srl | srl a0, a1, a2 | a0 = a1 >> a2(高位補0) |

| sra | sra a0, a1, a2 | a0 = a1 >> a2 (算術右移,高位補原來的符號位) |

| slt | slt a0, a1, a2 | a1 < a2 ? 1 : 0 |

| xor | xor a0, a1, a2 | a0 = a1 ^ a2 |

| or | or a0, a1, a2 | a0 = a1 |

| and | and a0, a1, a2 | a0 = a1 & a2 |

2.2、I 型指令

字段:

| imm | rs1 | funct3 | rd | opcode |

|---|---|---|---|---|

| 12位 | 5位 | 3位 | 5位 | 7位 |

指令:

示例:

| 指令 | 示例 | 含義 |

|---|---|---|

| addi | add | a0, a1, 0x50 |

| slli | slli a0, a1, 5 | a0 = a1 << 5 (低位補0) |

| srli | srli a0, a1, 5 | a0 = a1 >> 5 (高位補0) |

| srai | sra a0, a1, 5 | a0 = a1 >> 5 (高位補原來的高位) |

| slti | slti a0, a1, 0x50 | a1 < 0x50 ? 1 : 0 |

| xori | xor a0, a1, 0x50 | a0 = a1 ^ 0x50 |

| ori | ori a0, a1, 0x50 | a0 = a1 |

| andi | andi a0, a1, 0x50 | a0 = a1 & 0x50 |

取值指令—Load

字段:

| imm | rs1 | funct3 | rd | opcode |

|---|---|---|---|---|

| 12位 | 5位 | 3位 | 5位 | 7位 |

指令:

示例:

lb x10, 0(x1) //將x1的值加上0,將這個值作為地址, 取出這個地址所對應的內存中的值, 將這個值賦值給x10(取出的是8位數值)

lh x10, 0(x1) //從內存中取出16位數值

lw x10, 0(x1) //從內存中取出32位數值

lbu x10, 0(x1) //從內存中取出8位無符號數值

lhu x10, 0(x1) //從內存中取出16位無符號數值

2.3、S 型指令

字段:

| imm[11:5] | rs2 | rs1 | funct3 | imm[4:0] | opcode |

|---|---|---|---|---|---|

| 7位 | 5位 | 5位 | 3位 | 5位 | 7位 |

指令:

示例:

sb x10, 0(x1) //x1的值加上0,將這個值作為地址, 將x10的值存儲到上述地址所對應的內存中去 (只會將x10的值的低8位寫入)

sh x10, 0(x1) //只會將x10的值的低16位寫入

sw x10, 0(x1) //只會將x10的值的低32位寫入

2.4、B 型指令

字段:

| imm[12] | imm[10:5] | rs2 | rs1 | funct3 | imm[4:1] | imm[11] | opcode |

|---|---|---|---|---|---|---|---|

| 1位 | 6位 | 5位 | 5位 | 3位 | 4位 | 1位 | 7位 |

指令:

| 指令 | 示例 | 含義 | 備注 |

|---|---|---|---|

| beq | beq a1, a2, Lable | if(a1 == a2){goto Label;} | Lable是任意自定義的標簽 |

| bne | bne a1, a2, Lable | if(a1 != a2){goto Label;} | |

| blt | blt a1, a2, Lable | if(a1 < a2){goto Label;} | |

| bgt | bgt a1, a2, 100 | if(a1 > a2){goto Label;} | 100與Label對應著相同的指令, 實際上在運行時Label會變成pc+xxx |

| bge | bge a1, a2, 100 | if(a1 <= a2){goto Label;} | |

| ble | ble a1, a2, 100 | if(a1 >= a2){goto Lable;} |

2.5、U 型指令

字段:

| imm[31:12] | rd | opcode |

|---|---|---|

| 10位 | 5位 | 7位 |

指令:

lui x10, 0x65432 //得到立即數的高20位,低位補0,立即數范圍為:0x00~0xFFFFF

2.6、J 型指令

字段:

| imm[20] | imm[10:1] | imm[11] | imm[19:12] | rd | opcode |

|---|---|---|---|---|---|

| 1位 | 10位 | 1位 | 8位 | 5位 | 7位 |

指令:

示例:

jal ra, symbol // 跳轉到Symbol中去, 并把ra設置成返回地址 Symbol 可以是自定義的Label ,也可以是某個函數名

jal ra, 100 // 跳轉到pc + 100 * 2的地方中去, 并把ra設置成返回地址 pc相對尋址,對應的是位置無關代碼(PIC)

jalr ra, 40(x10) //跳轉到x10+40 的地方中去, 并把ra設置成返回地址x10+40必須是絕對地址,指向內存中某個確定的地方(往往是函數的開頭),非PIC

3、匯編語言翻譯成機器語言

示例1:

例題

對于符號表示為:

add x9, x20, x21

的RISC-V指令,首先以十進制表示,然后用二進制表示

答案

有上面的介紹可知add指令的字段如下:

直接用十進制表示如下:

| funct7 | rs2 | rs1 | funct3 | rd | opcode |

|---|---|---|---|---|---|

| 0 | 21 | 20 | 0 | 9 | 51 |

一條指令的每一段稱為一個宇段。

第一、第四和第六個字段(0、0 和 51)組合起來告訴RISC-V計算機該指令執行加法操作。

第二個字段給出了作為加法運算的第二個源操作數的寄存器編號(21 表示 x21),

第三個字段給出了加法運算的另一個源操作數(20代表×20)。

第五個字段存放要接收總和的奇存器編號(9代表x9)。

因此,該指令將寄存器 x20 和寄存器 x21 相加并將和存放在寄存器x9中。

用二進制表示如下:

| funct7 | rs2 | rs1 | funct3 | rd | opcode |

|---|---|---|---|---|---|

| 0000000 | 10101 | 10100 | 000 | 01001 | 0110011 |

總上,add x9, x20, x21 的RISC-V指令對應的機器碼為: 00000001010110100000010010110011

示例2

例題

有以下幾條匯編:

ld x9, 240(x10)

add x9, x21, x9

addi x9, x9, 1

sd x9, 240(x10)

將它們翻譯為對應的機器碼

答案

審核編輯:湯梓紅

-

寄存器

+關注

關注

31文章

5357瀏覽量

120600 -

指令集

+關注

關注

0文章

226瀏覽量

23389 -

RISC-V

+關注

關注

45文章

2292瀏覽量

46227

發布評論請先 登錄

相關推薦

正式的RISC-V基礎指令集架構與特權架構規范來了,RISC-V基金會已正式批準

淺談RISC-V指令集架構的來龍去脈

Microchip發布業界首款基于RISC-V指令集架構的SoC FPGA開發工具包

RISC-V指令集的特點總結

僅用7個月就設計出了一款基于RISC-V指令集的AI芯片

RISC-V指令集架構微控制器相關知識

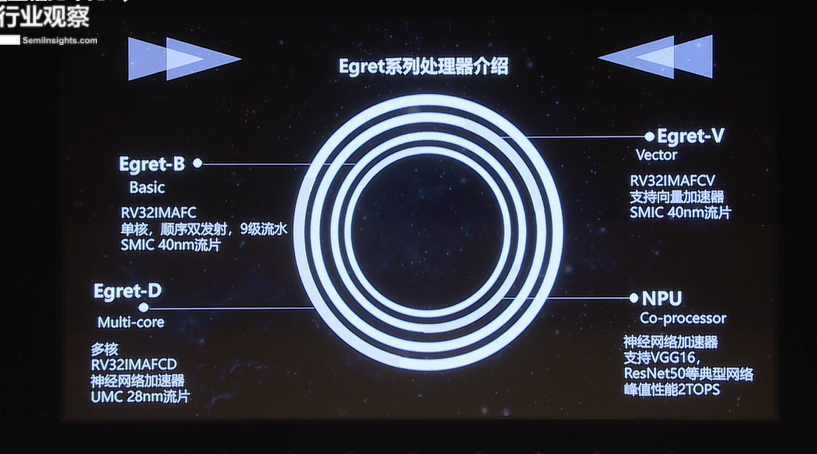

基于RISC-V指令集Egret系列處理器的性能及應用場景

risc-v中國峰會直播:如何優化RISC-V指令集架構的代碼密度?

RISC-V指令集

RISC-V指令集

評論