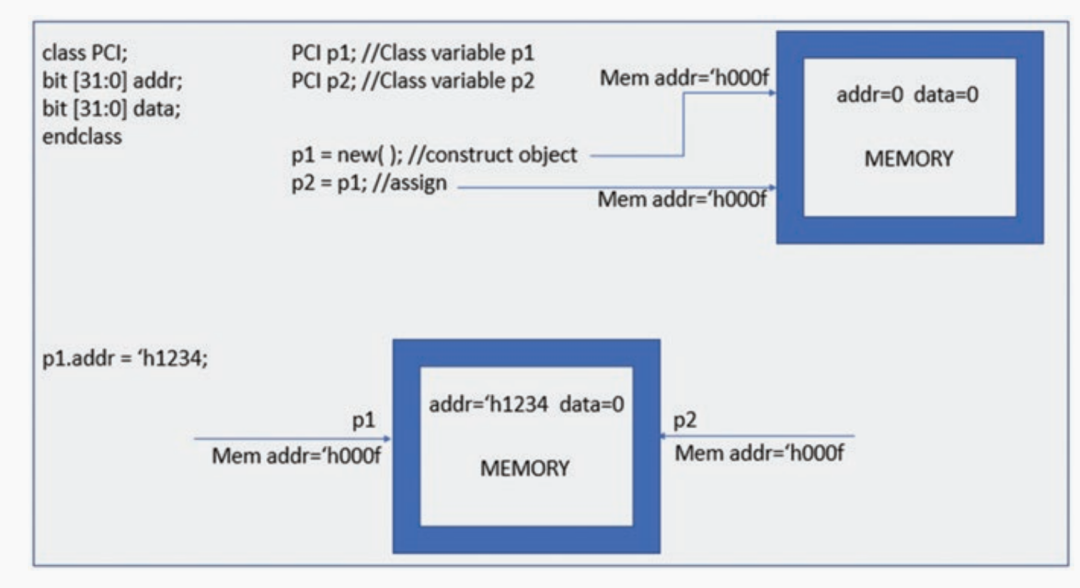

當我們聲明一個類時還沒有分配內存,只有在實例化(new())時才會分配內存。這個時候對象句柄指向被分配的內存,下面是對象句柄賦值的示例:

class PCI; …… endclass PCI p1; //a variable 'p1' of type PCI is created. //Memory is not allocated. p1 = new; //this is where memory is allocated for 'p1'. PCI p2; p2 = p1; //class assignment

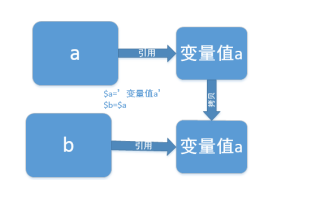

在上面的例子中,p2是一個PCI類型的變量(尚未完成實例化分配內存),而p1是一個完成了實例化的對象句柄。

當賦值p2 = p1時,實際上還是只有一個對象,“p1”和“P2”對象句柄現在都指向相同的內存空間。

正因為它們都指向相同的內存空間,所以“p1”對象的變化將反映到“p2”對象,反之亦然。

module class_TOP( ); class PCITop; logic [31:0] addr; logic [31:0] data; function void disp (string instName); $display("[%s] addr = %h data = %h", instName, addr, data); endfunction endclass : PCITop PCITop PCI1, PCI2; initial begin; PCI1 = new;//create object PCI1 PCI2 = PCI1; //class assignment PCI1.addr = 'h1234_5678; //using PCI1 handle PCI1.data = 'hf0f0_f0f0; PCI1.disp("PCI1"); PCI2.disp("PCI2"); PCI2.addr = 'h8765_4321; //using PCI2 handle PCI2.data = 'hff_0101; PCI1.disp("PCI1"); PCI2.disp("PCI2"); end endmodule

仿真log:

[PCI1] addr = 12345678 data = f0f0f0f0 [PCI2] addr = 12345678 data = f0f0f0f0 [PCI1] addr = 87654321 data = ffff0101 [PCI2] addr = 87654321 data = ffff0101 V C S S i m u l a t i o n R e p o r t

上面的例子中,我們對對象“PCI1”的修改能反映到“PCI2”,對對象“PCI2”的修改也反映到了“PCI1”。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

內存

+關注

關注

8文章

3019瀏覽量

74005 -

Verilog

+關注

關注

28文章

1351瀏覽量

110077 -

System

+關注

關注

0文章

165瀏覽量

36929

原文標題:SystemVerilog中的類的賦值

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SystemVerilog中的類構造函數new

在systemverilog中,如果一個類沒有顯式地聲明構造函數(new()),那么編譯仿真工具會自動提供一個隱式的new()函數。這個new函數會默認地將所有屬性變量。

發表于 11-16 09:58

?3636次閱讀

SpinalHDL中Bundle與普通數據類型之間的連接賦值轉換

SpinalHDL中Bundle與SystemVerilog中的packed struct很像,在某些場景下,與普通數據類型之間的連接賦值可以通過asBits,assignFromBi

發表于 10-18 14:22

更好地理解SystemVerilog的多態Polymorphism

多態(Polymorphism) ,從字面意思上看指的是多種形式,在OOP(面向對象編程)中指的是同一個父類的函數可以體現為不同的行為。在SystemVerilog中,指的是我們可以使用父類

發表于 12-05 17:34

verilog中阻塞賦值和非阻塞賦值到底有什么區別

1、阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當前的賦值語句執行完畢才能

發表于 04-25 08:00

?0次下載

SystemVerilog中$cast的應用

SystemVerilog casting意味著將一種數據類型轉換為另一種數據類型。在將一個變量賦值給另一個變量時,SystemVerilog要求這兩個變量具有相同的數據類型。

數字硬件建模SystemVerilog-組合邏輯建模(1)連續賦值語句

SystemVerilog有三種在可綜合RTL級別表示組合邏輯的方法:連續賦值語句、always程序塊和函數。接下來幾篇文章將探討每種編碼風格,并推薦最佳實踐編碼風格。

SystemVerilog中的Semaphores

SystemVerilog中Semaphore(旗語)是一個多個進程之間同步的機制之一,這里需要同步的原因是這多個進程共享某些資源。

verilog中阻塞賦值和非阻塞賦值的區別

阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當前的賦值語句執行完畢才能執行

發表于 12-19 16:49

?7413次閱讀

簡述python空類和實例屬性賦值

python類主體沒有任何內容,只有pass語句,稱為空類。

## 1.2 obj.attr屬性賦值

通過obj.attr=value進行類和實例屬性

SystemVerilog:處理信號雙驅動問題解析

在SystemVerilog中,類型可以分為線網(net)和變量(variable)。線網的賦值設定與Verilog的要求相同,即線網賦值需要使用連續

SystemVerilog中的類的賦值

SystemVerilog中的類的賦值

評論