一、

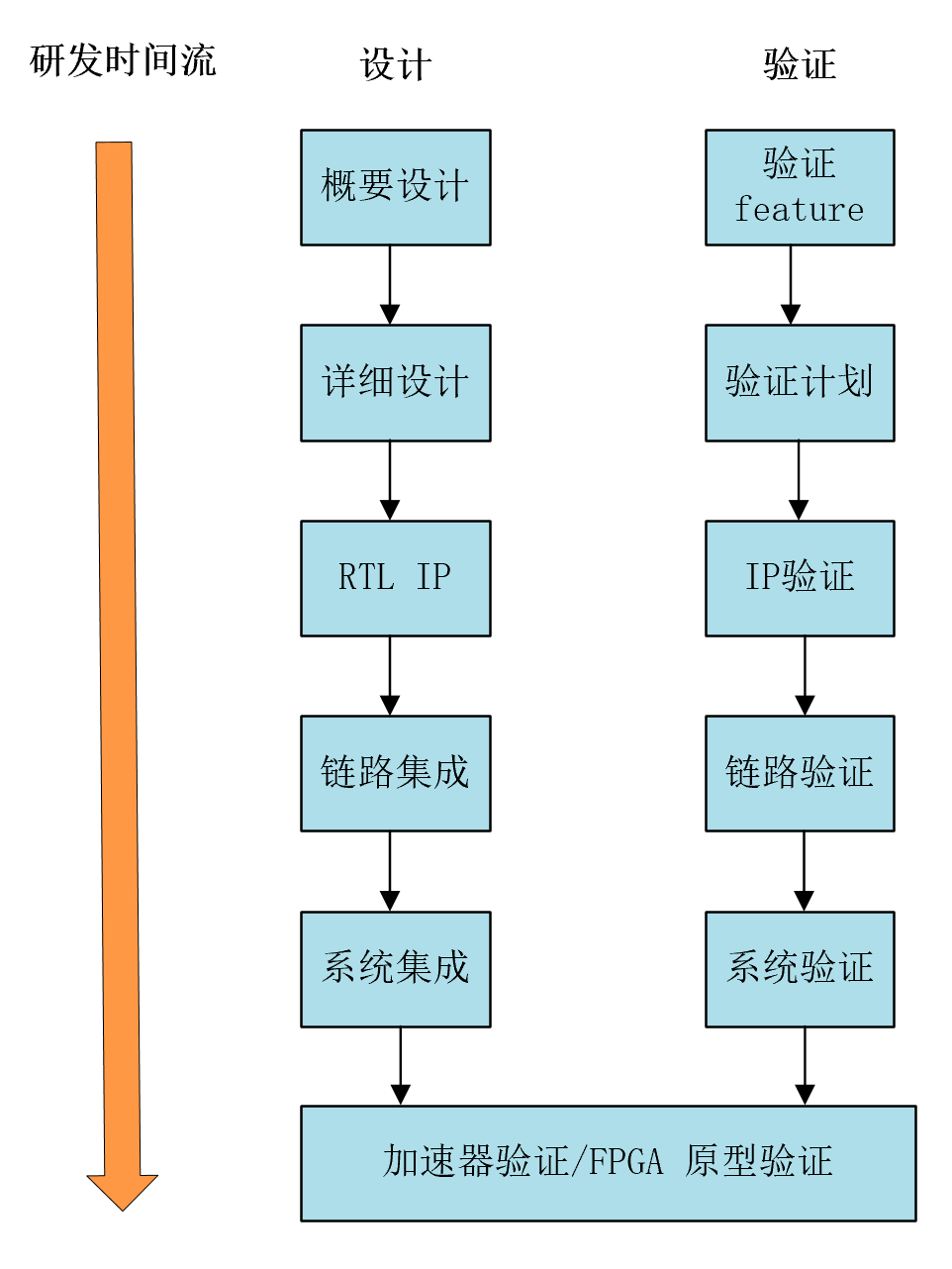

經典的設計與驗證流程

可以看到設計與驗證永遠是同步節奏,即使因為一些客觀原因,導致驗證稍微慢于設計節奏,最終也會回到同步的節奏上。

這樣的理想狀態就對設計工程師有一定要求,比如拿到設計需求,就然后開始概要設計文檔,其中就包括整體的模塊對外接口,關鍵時序,整體的架構設計等。驗證工程師拿到概要設計,就可以開始進行驗證feature規劃。

詳細設計文檔,設計要完成整體的模塊的控制流,數據流、memory需求規格,狀態機,關鍵電路,關鍵時序設計等。驗證拿到詳細設計文檔,就可以進行驗證case規劃,驗證計劃文檔編寫。

理想的狀態下設計拿著自己的詳細設計文檔就可以直接行云流水式的寫代碼。寫代碼真體力活。而這段時間驗證就可以進行驗證平臺搭建和驗證case設計。

設計代碼寫完,編譯通過,lint清除,將一些低級錯誤扼殺在搖籃里。驗證平臺也搭建好,設計與驗證對接,一起調試第一條case。第一條case通過,環境OK,代碼OK。開始循序漸進debug。

驗證驗出bug,提給設計,設計修改,上傳版本管理庫,驗證up,進行回歸。完全正確,調試下一條case。

IP驗證到一定feature成熟,釋放一個版本給鏈路驗證同事,驗證多個IP配合的場景和當前版本成熟的feature,很少會出現在鏈路上驗出IP級的bug(當然也有)。

鏈路驗證到一定feature成熟階段,釋放版本給系統驗證同事,驗證多個鏈路配合場景和當前版本的成熟feature。系統驗證成熟到一定feature。然后再上硬件加速器驗證和FPGA原型驗證。

整個理想的過程,一氣呵成,在系統驗證和加速器/FPGA原型驗證上,會比較順利,不會因為模塊級的bug卡住驗證進度,因為在大系統里面調試效率非常低,基本就只剩過case。

理想很豐滿,現實很骨感。

現實情況是

設計人員寫完代碼才寫文檔,導致驗證遲遲沒有設計文檔,無法開始驗證計劃和驗證環境搭建。最終整體項目時間delay1-2個月。

設計人員不寫文檔,直接寫代碼,邊寫邊想,設計架構沒有經過評審,和上下游交互接口和時序都對不上,代碼寫完也是要修改重新寫,最終整體項目delay1-2個月。

項目delay了,設計著急了,在IP驗證尚未完全時就開始鏈路驗證,系統驗證。出現問題,debug效率低下,一天發現一個低級錯誤,鏈路驗證和系統驗證仿真時間長。你為什么總在加班?

設計著急了,在鏈路驗證和系統驗證尚未完全時,就開始加速器/FPGA原型驗證,編譯一個版本要一天,效率更低下。你為什么總在加班?

最終,項目還是delay,所有人也還是要加班完成。所以做芯片是有章法可循,業界多少年總結出來的血淚經驗,不遵守是要吃虧的。

設計工程師與驗證工程師是好朋友

設計工程師和驗證工程師是永遠的好朋友,你們是共同在完成一個工程,產品,磚。驗證的case和驗證完備性是要兩個人共同的努力的成果。

有一個驗證,發現一個case fail了,打電話給設計,case xxx fail了,看下什么原因。設計跑出來看了下,回個電話,是你平臺的原因,修改下,case pass了。設計與驗證是好朋友。

有一個驗證,發現一個case fail了,打電話給設計,case跑一次賊慢 ,波形我已經跑好了,直接在我們的共享窗口上看下吧,設計看出了問題,本地修改了下,回個電話,我上傳了,你up下再跑一下。晚上下班前回歸下case。設計與驗證是好朋友。

又有一個驗證,因為一些個人原因,驗證平臺沒有及時搭建起來,delay與設計,但設計代碼已經寫完了,沒有平臺和case驗,跑到驗證辦公位后面,站在身后監工,沒你平臺,我可搞不了。設計與驗證是好朋友。

還有一個驗證,沒有發現任何bug,設計打電話說,我改了一行代碼,沒有任何影響,就是代碼風格變了下,這樣寫覆蓋率更好收,占用資源更小。我要提個問題單記錄一下,這造成了我回歸的工作量。設計與驗證是好朋友。

突然有一個設計,代碼遲遲不愿意給驗證,說我代碼bug太多了,我要自己先驗下,驗證沒法開展工作,然后過了一陣子,找驗證說,我過了一百多條冒煙case。拿去給你驗吧。驗證:你這代碼給我都八時了,等著項目delay吧。設計與驗證是好朋友。

流程死的,人是活的

并不是所有的設計都要走繁重的流程,我做了個xxx設計,先進行概要設計評審,詳細設計評審,代碼review,驗證feature評審,驗證計劃評審,驗證環境搭建,最后規劃了10個case,覆蓋率達到100%。這么個破玩意兒,兩個人整兩個月的時間。

有設計說,就這,那我還不如自己驗,你給我搭個平臺,我自己跑case,收覆蓋率,上FPGA原型驗證。兩周搞定。流程是死的,人是活的。但你需要分清什么情況下怎么做才是對的。

審核編輯 :李倩

-

工程師

+關注

關注

59文章

1592瀏覽量

69688 -

架構設計

+關注

關注

0文章

33瀏覽量

7136

原文標題:設計工程師與驗證工程師如何合作?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RK3128 Android 7.1 進入深度休眠流程分析

新思科技如何驗證更安全的智能汽車軟件

華大九天物理驗證EDA工具Empyrean Argus助力芯片設計

超大規模芯片驗證:基于AMD VP1902的S8-100原型驗證系統實測性能翻倍

Cadence Conformal AI Studio助力前端驗證設計

西門子利用AI來縮小行業的IC驗證生產率差距

西門子推出Questa One智能驗證解決方案

西門子EDA助力提升IC設計驗證效率

使用HLS流程設計和驗證圖像信號處理設備

芯華章發布FPGA驗證系統新品HuaProP3

【「數字IC設計入門」閱讀體驗】+ 數字IC設計流程

Lint靜態驗證工具如何助力IC設計

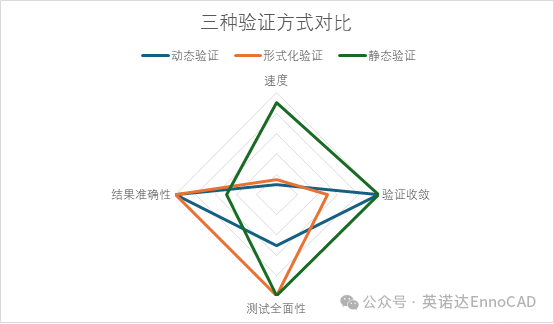

形式驗證如何加速超大規模芯片設計?

評論