本篇文章為“讀懂 SmartSiC” 系列文章的下篇,將對 SmartSiC 解決方案的創新優勢、研發、生產情況進行深入的介紹。

閱讀“讀懂 SmartSiC” 系列文章上篇

SmartSiC晶圓卓越的性能:

更環保、更高效、更出色

Soitec SmartSiC 晶圓

無論是對于 150mm 晶圓還是 200mm 晶圓而言,SmartSiC 都是一種更環保、更高效、更出色的技術解決方案,有望成為 SiC 市場的行業標準之一。

SmartSiC 將可重復利用十次的優質單晶 SiC 與超高導電性操作晶圓相結合,與傳統 SiC 襯底相比,這種即插即用的解決方案可以無縫集成到所有現存的電源生產線中,并表現出明顯的商用、環境與制造優勢。

簡單且節能的制造工藝使 SmartSiC 的碳足跡更少,更為環保。與傳統 SiC 相比,每片 SmartSiC 晶圓減少的碳排放量可高達 70%。

通過重復利用稀缺的 200mm 單晶供體,Soitec 能夠助力這些大尺寸襯底的快速落地應用,賦能市場的增長。SmartSiC 的優化設計所帶來的卓越生產良率、更高的效率和功率密度,為電力電子設備提供了更好的解決方案。相比塊狀 SiC,SmartSiC 具有更高的導電性,可為每平方毫米功率器件(例如 MOSFET 或二極管)提供多達 20% 的電流。這是生成新一代功率器件的制勝秘訣。

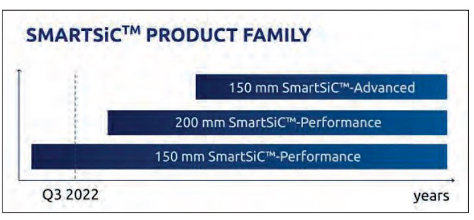

Soitec 的 SmartSiC 產品系列由 SmartSiC-Performance和 SmartSiC-Advanced 襯底組成。SmartSiC-Performance 目前處于原型開發階段,正在與 Soitec 客戶進行驗證。而 Soitec 的創新團隊正在研發 SmartSiC-Advanced 無 BPD 襯底,該產品目前處于送樣階段。

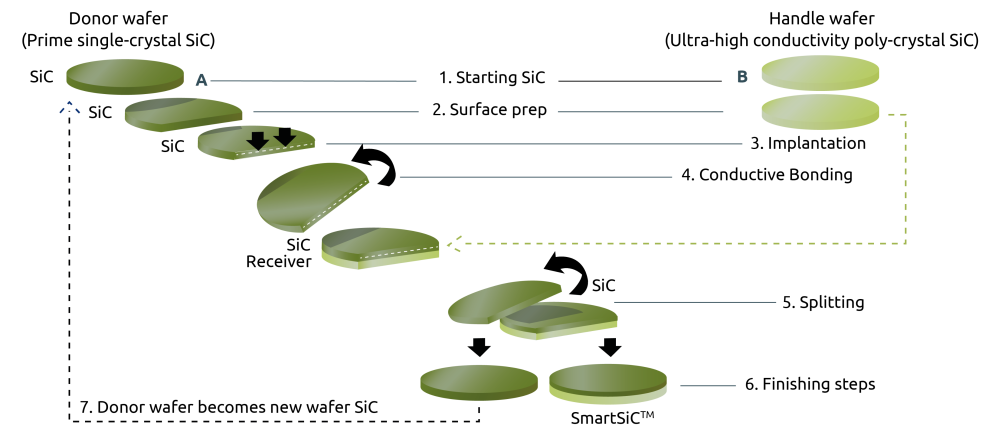

圖 2:Soitec 獨特且專利的 SmartCut 工藝同樣適用于 SiC 材料

在具有超高導電性的多晶碳化硅操作襯底之上(其 150mm 和 200mm 晶圓的總厚度分別為 350μm 和 500μm),SmartSiC 襯底的優化設計能夠提供最高水準、厚度小于 1μm 的單晶 SiC 層。供體晶圓減去用于第一個 SmartSiC 晶圓的 1μm 層之后,可重復用于第二個 SmartSiC 晶圓。以此類推,每個供體晶圓至少可用于十個 SmartSiC 晶圓。

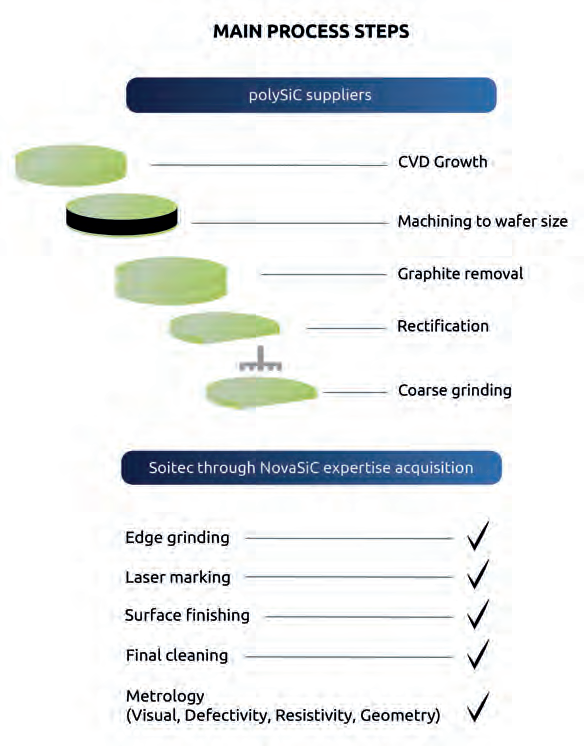

與塊狀 SiC 中使用的物理氣相傳輸 (PVT) 相比,采用多晶碳化硅作為每個 SmartSiC 晶圓生產的操作晶圓則是基于更環保、用時更短的化學氣相沉積 (CVD) 工藝。Soitec 和合作伙伴共同開發的 PolySiC 具有足夠的摻雜來控制襯底的導電性,同時還能保持極具競爭力的成本優勢(見圖 3)。

圖 3:PolySiC 主要工藝步驟

經過多年積淀,無論成熟度還是專業儲備,Soitec 都具備能力定義并確保晶圓幾何構造的完美,而這恰是掌握晶圓鍵合的關鍵所在。2021 年 11 月 Soitec 收購 NovaSiC,為公司帶來超過 25 年的 SiC 晶圓生產經驗,是 Soitec 在碳化硅戰略路線上的又一里程碑。

截至目前,Soitec 的 SmartSiC 已在襯底工藝和設計中達到了穩定的高水平。經過密集和大規模的測試與原型設計,Soitec 生產的晶圓為市場、電力設備和電力系統帶來的價值和益處顯著。采用 SmartSiC 生產的 MOSFET 和二極管性能均獲得大幅提升,同時擁有了更為長期的可靠性和更強的高溫穩健性。目前,多家設備制造商已承諾加大資源投入力度,在其下一代產品的認證中采用 SmartSiC。

探秘 SmartSiC 的研發

Soitec 最初派遣研發團隊深入研究 SmartSiC 項目時,目的在于將 SiC 的制造良率提高到全球公認的硅基功率器件標準水平。

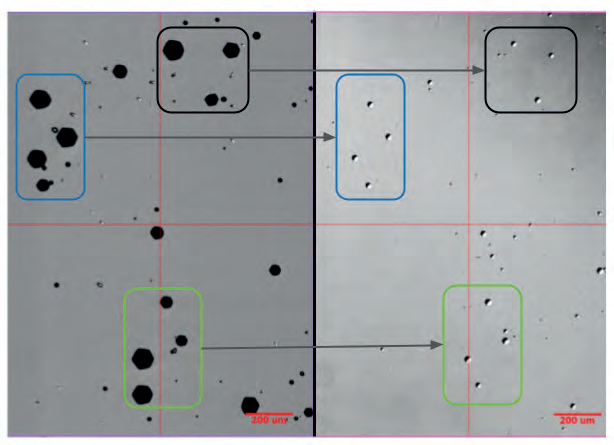

SmartCut 工藝可以保持來料供體晶圓的晶體質量。如圖 4 所示,在供體和 SmartSiC 表面的相同位置可以觀察到氫氧化鉀(KOH) 蝕刻晶體產生的缺陷。

圖 4:晶體缺陷表征、KOH 蝕刻和光學顯微鏡觀察結果;單晶 SiC 供體(左)和 SmartSiC (右)點對點比對

為降低缺陷水平,Soitec 探索并采用了一種新的概念,即在已去除基面位錯(BPD)的供體上采用 Smart Cut 工藝。

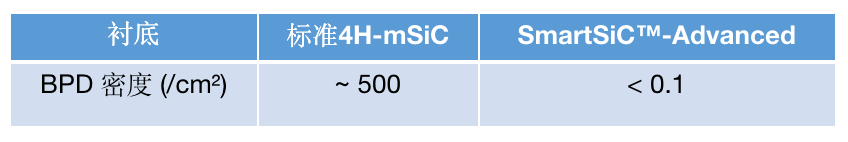

利用單晶 SiC 晶圓獨特的生長特性,無 BPD 的供體能夠將無 BPD 層轉移到多晶 SiC 操作晶圓上。這種新型優化襯底稱為 SmartSiC-Advanced。SmartSiC-Advanced 襯底的 BPD 密度值如圖 5 所示。

圖 5:供體 SmartSiC-Advanced 襯底中的 BPD 缺陷密度

具備無 BPD 頂層的 SmartSiC-Advanced 襯底因此成為漂移外延環節的優質晶種層。

這明顯降低了致命缺陷的潛在成核位置密度,同時擴大了外延工藝窗口并簡化了外延堆棧,而且無需轉換緩沖層。

良率模擬和實驗表明,這些改進將引入的外延生長致命缺陷密度降低了 10 倍,并且將大于 20 平方毫米的器件生產良率提高到 20% 以上。在器件可靠性方面,無基面位錯層不僅可以防止位錯滑動,還能消除器件中的雙極退化。Soitec 的下一代 SmartSiC-Advanced 襯底消除了 SiC 晶圓中的 BPD,對整個 SiC 行業而言,有望將 SiC 器件制造良率提升至 90%。

而且,SmartSiC 中采用的多晶 SiC 操作襯底具有高摻雜水平,這使 SiC 功率器件(二極管或 MOSFET)背面的歐姆接觸層更易制成。

Soitec 的最新研究證明,無需退火的歐姆接觸工藝可在 SmartSiC 襯底上輕松執行,且長遠芯片組裝的可靠性不會因此受到影響。

Soitec 150mm 的 SmartSiC-Advanced 產品已經開始送樣。其原型襯底正接受主要客戶的檢驗,并可根據需求向其他客戶彈性交付。更多數據已于 ICSCRM 2022 國際會議(2022 年碳化硅及相關材料國際會議)上進行公布。

SmartSiC 晶圓廠的啟動與擴產

圖 6:位于法國的新工廠貝寧 4 廠

大批量生產是 Soitec 的下一步目標舉措。Soitec 用于 SmartSiC 大規模生產的新工廠 Bernin 4 已于 2022 年 3 月破土動工,開工日期定為 2023 年年中(如圖 6 所示)。憑借最先進的設備設施,Soitec 將在 2024 年實現 SmartSiC 的產能提升;到 2030 年,SmartSiC 晶圓總產能(包括 150mm 和 200mm)將達到 100 萬片/年。其中大部分為 200mm 晶圓,這得益于 Soitec 的兩項關鍵技術:

經過數十年的發展,晶圓的尺寸面積不斷擴大,SmartCut 工藝的效益規模也呈現出指數級增長,而 200mm 規格的晶圓變得愈發重要。

Soitec 200mm SmartSiC 晶圓所具備的 10 倍重復利用率,將成倍優化資源利用率,緩解供應鏈壓力,并加速汽車和工業市場中高質量晶圓的高效生產與應用。

隨著多個合作伙伴對 SmartSiC-Performance 產品原型的認可(如圖 7 所示),2022 年的產品認證正處于緊鑼密鼓地擴大范圍并加速推進中。

圖7:150mm 和 200mm 規格的 SmartSiC 晶圓

SmartSiC晶圓正成為新的行業標準

電動汽車正在經歷百年一遇的變革,市場上的創新成果不斷涌現。上一次交通業變革發生在二十世紀 90 年代左右,人類用了 15 年時間從馬車交通時代轉進入機械交通時代;而鑒于 CO2減排和減緩全球變暖的迫切需要,從汽油車時代進入電動車時代的轉變應該會更快。

自 2018 年特斯拉引入 SiC 并開創電動汽車市場以來,這項技術已被大多數汽車制造商采納。然而,SiC 還需要克服在電氣性能、產能、成本和良率方面的眾多障礙,才能在電動汽車領域獨占鰲頭。

Soitec 成功預見了上述挑戰以及電動汽車行業蓬勃發展的勢頭。我們推出的 SmartSiC 是具有更高附加值的單晶 SiC 襯底替代品,能夠為更高效率的電源提供更環保、更高效、更出色的解決方案。

由于單晶 SiC 供體晶圓可重復使用 10 次,并且低 RDSON 功率器件的電導率提高了10倍,SmartSiC 已能夠實現大批量生產,并有望成為行業新標準。

Soitec 汽車與工業部門副總裁 Emmanuel Sabonnadiere 表示:“我們的 SmartSiC 襯底將成為加速電動汽車變革的關鍵,可幫助電力電子設備的能效與性能提升至新高度,賦能電動汽車的發展。”

圖 8:SmartSiC 產業化藍圖

Soitec 的創新將助力提升資源利用及能效,助推經濟發展和賦能商業成功。我們的創新成果正在推動眾多行業和生態系統的發展,而半導體及其基礎襯底的戰略地位正是他們所一致認可的。

Soitec 的創新土壤孕育著美好未來!

注:Soitec 的四篇科學出版物已于 ICSCRM 2022 上正式發布。

審核編輯 :李倩

-

單晶

+關注

關注

1文章

61瀏覽量

14157 -

SiC

+關注

關注

29文章

2841瀏覽量

62720 -

SOITEC

+關注

關注

3文章

48瀏覽量

14305

原文標題:讀懂 SmartSiC?| 助推電動汽車發展的新動力:Soitec 的 SmartSiC? (下篇)

文章出處:【微信號:Soitec,微信公眾號:Soitec】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

中科曙光南京研究院方案入選江蘇省信息技術創新優秀解決方案

LoRaWAN網絡在智慧水務中的創新解決方案

硬核智造驅動創新,大核桃智能巡檢整體解決方案助力高危行業安全生產

解決方案 | 基于TSMaster的平板電腦解決方案

emc存儲解決方案的優勢

【?嵌入式機電一體化系統設計與實現?閱讀體驗】+磁力輸送機系統設計的創新與挑戰

梯度科技入選2023年信息技術應用創新解決方案名單

飛凌嵌入式技術創新日(深圳站)精彩回顧

環旭電子微小化創新研發中心為多樣化市場提供SiP雙引擎技術平臺

SmartSiC解決方案的創新優勢、研發、生產情況

SmartSiC解決方案的創新優勢、研發、生產情況

評論