自過去十年以來,從消費類應用、網絡或防御系統(包括傳感器)開始的不同應用領域都是半導體VLSI電路技術的影響。對于ASIC(SoC)功耗,性能(時間)和面積始終是設計中具有挑戰性的因素。根據用戶應用,對上述一個或所有因素進行優化。除了PPA,處理IC結構測試-DFT時間也成為一項聚合挑戰性的任務。由于設計復雜性每天都在增加數倍 - 由于摩爾定律,使用傳統的DFT掃描方法可以測試ASIC,但它會導致更高的測試數據量和測試時間非線性增加。以前,測試成本是實施掃描壓縮時唯一考慮的因素。與標準(未壓縮)相比,任何壓縮技術的關鍵要求都是保持較高的測試質量。測試壓縮比在減少總測試時間方面起著至關重要的作用。在本文中,我們主要關注一種在芯片頂部使用最佳數量的測試通道來減少測試時間的方法,而不會影響測試質量。

一、簡介

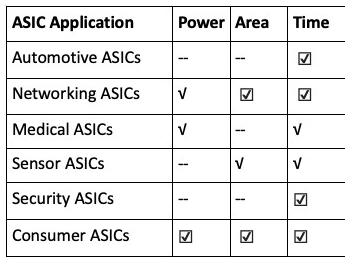

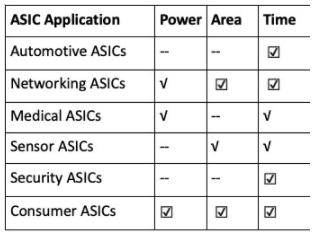

ASIC,如名稱所定義,是為特定應用而設計的。可以使用不同的技術來創建ASIC,但由于高可靠性和低成本,CMOS很常見。對于ASIC(SoC設計),功耗、性能(時間)和面積是設計中具有挑戰性的因素。根據應用權重,這些因素取決于ASIC。在這里,圖1顯示了不同的應用,表I列出了因子的權重。

表一

功率、面積和時間比較

第二。ASIC設計中掃描壓縮的需求

早些時候,測試儀成本是實施掃描壓縮時唯一考慮的因素。測試模式的數量取決于測試數據量和測試時間。模式截斷選項會導致較低的測試覆蓋率,并最終增加發往客戶的百萬分之缺陷部件 (DPM),從而影響良率 [1]。因此,為了避免由于測試質量低而導致測試逃逸增加,業界已經認識到不可避免地需要壓縮測試模式。下一代 ASIC (SoC) 設計流程具有更復雜的結構,這導致有新的故障模型和額外的測試模式來檢測這些,壓縮也有助于解決該因素 [1]。

掃描壓縮的結果如下 [1]:

? 減少掃描數據存儲器的要求

? 減少每個零件的測試應用時間

? 減少所需的掃描通道數量

? 縮短串行負載模式的仿真時間

A. 壓縮技術簡介

與標準(未壓縮)ATPG相比,任何壓縮技術的關鍵要求都是保持較高的測試質量。壓縮技術基于傳統的確定性ATPG,并使用相同的故障模型,通過熟悉的流程[1]獲得類似的測試覆蓋率。它通過改進掃描測試數據的壓縮和減少測試時間來擴展ATPG。它通過使用少量掃描通道控制大量內部掃描鏈 [1] 來實現掃描測試數據的壓縮。

B. 基本壓縮術語

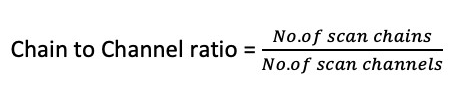

對于壓縮,外部掃描鏈稱為掃描通道,以區別于內核內部的內部掃描鏈 [2]。它們的數量明顯少于內部掃描鏈的數量。鏈通道比的確定,定義了設計的壓縮,直接影響測試覆蓋率和測試數據量。有效壓縮取決于掃描鏈和掃描通道 [2]。

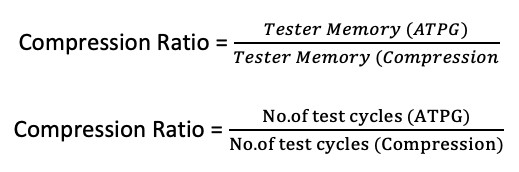

壓縮可以表示為 ATPG 的測試器內存與壓縮的比率或 no 的比率。ATPG 與壓縮的測試周期。自 No.通道相同,兩種計算將是等效的 [3]。

壓縮是兩個因素的函數[3]。:

* 鏈與通道比率:掃描鏈(內部與核心)與掃描通道(外部)的比率

* 每種模式的班次循環次數變化(否。掃描鏈,否。掃描細胞和每個模式的初始周期)。

三、S罐壓縮分析

我們只能直接控制鏈與渠道的比例。然而,這三個因素是相關的。內部掃描鏈與外部掃描通道的比率越高,每個模式的壓縮率就越高,但壓縮分析將在您改變不同因素時為您提供壓縮的估計計算 [3]。

一個。什么是分析壓縮?

通常,掃描通道的數量由硬件資源決定,例如ATE上的測試通道和可用于測試的頂級設計引腳。但是,為了有效壓縮,我們可以更改掃描鏈要求。[4]。 壓縮分析命令處理不同鏈通道比對測試數據的影響,而無需修改芯片設計。壓縮分析有助于確定壓縮結構的鏈通道比率、測試覆蓋率和測試數據量。

B.壓縮分析如何工作?

它分兩步分析應用程序的壓縮。

這兩個步驟如下:

1. 分析掃描插入的設計,并給出測試覆蓋率開始下降的最大鏈通道比范圍。

2. 計算指定鏈通道比的硬件配置,生成臨時測試模式,并返回壓縮配置 [4] 的測試數據統計信息。

C. 壓縮分析流程:

1. 檢查當前掃描配置并計算通道/鏈比。

一個。根據壓縮配置,它將為您提供估計的壓縮比。(使用測試/測試配置報告進行檢查)。

2. 使用現有掃描配置寫出掃描設計網表并生成運行模式。

3. 在模式生成開始之前,添加analyze_compression命令。(模式生成之前)[4]。

4.此命令將有助于分析壓縮,并在模式生成階段結束時為您提供以下統計信息。

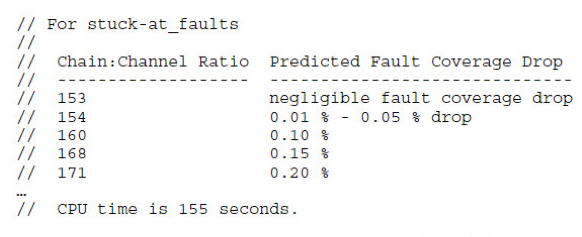

該工具分析設計并返回一系列鏈-通道比率值,從故障覆蓋率下降可忽略不計的比率開始,到故障覆蓋率下降 1% 的比率結束,如下所示:

圖2 壓縮分析數據 [4]

6. 為可忽略不計的故障覆蓋率下降選擇相應的通道環比值,并重新計算通道數。

7. 更新的通道號將是實現高壓縮所需的最小通道,故障覆蓋率下降可以忽略不計。

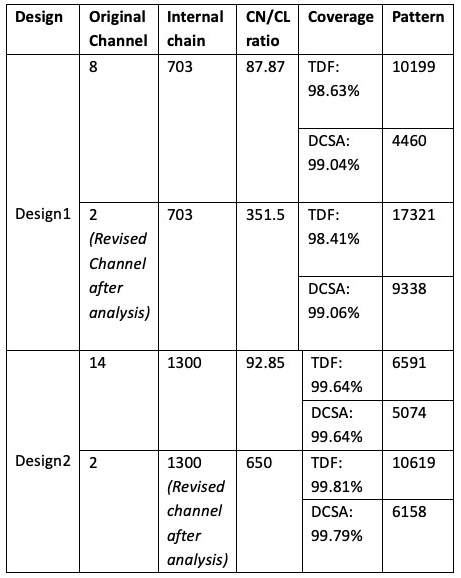

表三

結果比較

基于Flow,進行了通道縮減實驗,表II顯示了通道鏈比、壓縮比、覆蓋率和模式數的結果比較。

四。對分層測試的影響

致力于尖端技術導致頂級ASIC/SoC的引腳數減少。頂層將提供有限的引腳進行測試,大多數情況下,這些引腳在功能引腳之間共享[5]。引腳數量在頂層受到限制。使用以下示例,我們可以檢查塊級掃描通道減少在芯片級協作期間如何提供幫助。考慮下圖所示的場景。

使用不同的案例/場景,我們將檢查掃描通道減少如何在頂層提供幫助。

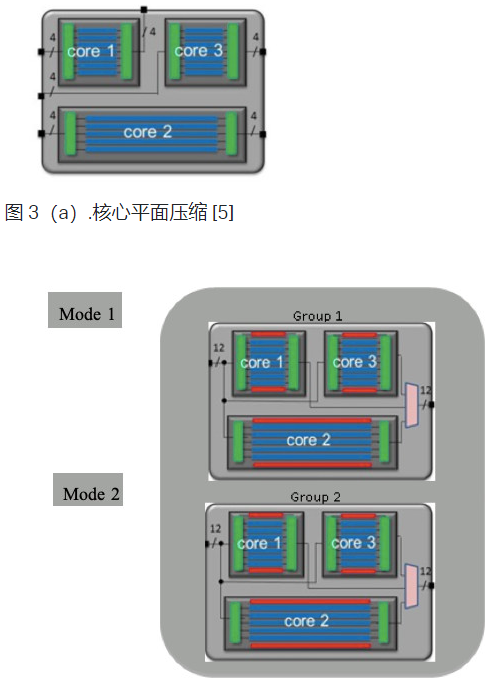

1) 案例 1:考慮我們有 3 個塊內核可用,并且有兩個在芯片頂層可用的實例。每個磁芯通過圖3(a)所示的4個掃描通道運行。在芯片頂級模式生成和仿真期間,所有三個實例都將成組使用。3 個核心/塊 * 2 個實例 = 6 個頂級實例。考慮到我們將有 12 個頻道可用。為了容納所有 6 個實例,我們需要創建 2 個模式來生成模式,如圖 3(b) 所示。

圖 3(b)。分層測試的概念圖

因此,在這種情況下,我們需要創建總共 2 個組來容納所有實例(每個 3 個)以使用 12 個可用的掃描通道。現在讓我們看看另一個案例。

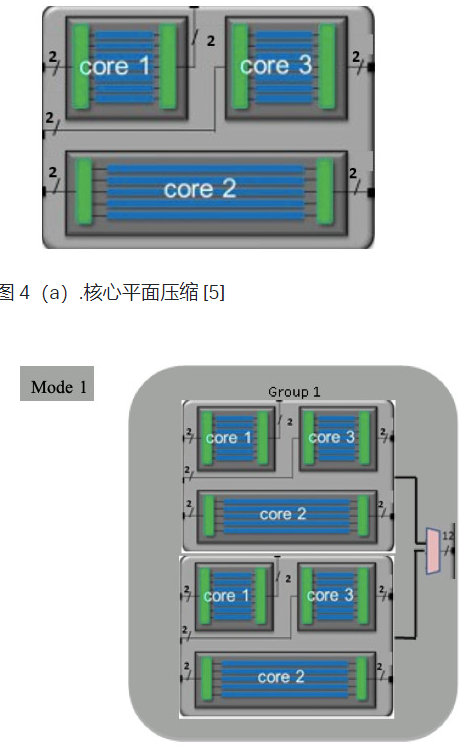

2) 案例 2:在這種情況下,請考慮使用 analyze_compression。我們已經減少了掃描通道,每個內核使用的掃描輸入/輸出通道數量為2個,如圖4(a)所示。讓我們檢查統計數據。3 個核心塊 * 2 個實例 = 6 個實例,頂部可用的總掃描通道為 12。每個塊將只使用2個通道,所以使用的總通道是6個通道。考慮到這一點,現在我們可以在 1 個模式下容納所有 6 個實例,如圖 4(b) 所示。測試時間將減少一半。

圖 4(b)。分層測試的概念圖

V. 增加壓縮和模式膨脹之間的權衡

1) 壓縮比

掃描通道數的減少導致更高的壓縮比。平衡壓縮目標與測試資源和設計需求也很重要。使用不必要的大壓縮目標可能會對壓縮、測試質量和芯片設計布局產生不利影響。

2) 測試覆蓋率較低

較高的壓縮比增加了每個測試模式的壓縮,但也增加了生成無法壓縮的測試模式的可能性,并可能導致較低的測試覆蓋率[6]。

3) 模式膨脹

更高的壓縮比還減少了動態壓實可以適應測試模式的故障數量。這可以增加測試模式的總數以檢測這些故障。

為了減輕較高壓縮對 ATPG 覆蓋率和模式數的影響,在analyze_compression期間,選擇通道與鏈比的值,以便對覆蓋率的影響可以忽略不計。

結論

在本文中,我們檢查了掃描壓縮是否確實有助于減少ASIC設計中的測試時間(DFT),而且掃描通道減少是幫助頂級測試時間的一種方式。根據示例案例研究,我們可以確定有效壓縮所需的最小通道數,以及它如何影響其他參數,如鏈通道比、壓縮比和測試時間。如今在半導體行業中,這些因素被廣泛用于節省測試成本。

審核編輯:郭婷

-

傳感器

+關注

關注

2550文章

51035瀏覽量

753081 -

asic

+關注

關注

34文章

1199瀏覽量

120436 -

soc

+關注

關注

38文章

4161瀏覽量

218165

發布評論請先 登錄

相關推薦

DFT和BIST在SoC設計中的應用

什么是DFT,DFT是什么意思

基于架構與基于流程的DFT測試方法之比較

Diodes MOSFET H橋節省50%占位面積

Xilinx RFSoC技術如何減少占位面積和功耗,提高硬件靈活性

PADS DFT審核確保設計的可測試性

如何使用DFT App進行硬件加速仿真設計

通過縮短測試時間減少ASIC設計中的DFT占位面積

通過縮短測試時間減少ASIC設計中的DFT占位面積

評論