頻率監控電路有多種類型。“過零檢測器”被認為是最常見的方法之一,因為它對周期性和常規信號的設計簡單。但是,如果信號是非周期性的或不規則的(脈沖之間包含非瞬時零周期),則不能使用過零。在這種情況下,峰峰值頻率監視器是理想的替代方案。

峰峰值法用于真實世界的模擬信號,通常來自模擬傳感器。本文所述的設計使用SLG46620VGreenPAK?計算0.5 Hz至200 Hz信號的低端頻率,其波形寬度在100 - 1000 ms之間。通過對該應用的基本了解,可以設計其他模擬寬度和周期的峰峰值測量。

該電路包括峰峰值設計的所有部分。因此,IC負責接收模擬信號樣本并將識別的峰值存儲在內部緩沖器中。它還負責將兩個峰值之間的測量時間段與內部閾值進行比較,以便在超過這些閾值時給出信號。

該設計由一個模擬信號輸入和 4 個輸出組成:

PD:在檢測到峰值時發出脈沖。

高 PPM:如果信號頻率超過上限閾值,則給出高。

低 PPM:如果信號頻率超過下限閾值,則給出高。

正常:如果頻率在兩個閾值內,則給出 HIGH。

該 IC 的模數轉換器 (ADC) 宏單元非常適合峰值信號檢測。所選電路功耗低且性價比高。它是此應用程序中所需的小型設備。該 IC 可以替代分立 IC 和無源器件系統。

對一般電路的解釋是期望它將被增強以適應特定的實際應用。設計結果利用GreenPAK Designer軟件信號發生器來測試各種信號并顯示相應的輸出。信號以高于和低于IC中存儲的值的頻率生成,并顯示每種情況的相應輸出,以向讀卡器確認操作正確。

可以在此處找到此應用程序的完整設計文件。

設計概述

檢測過程使用ADC模塊對模擬信號進行采樣,然后將其存儲在內部緩沖器中。然后接收模擬信號的新樣本,并與存儲的樣本進行比較。

如果新樣本的值大于當前存儲的值,則模擬電壓正在增加。新樣本存儲在緩沖器中,接收并比較信號的下一個樣本。但是,如果接收到的樣本等于緩沖區中存儲的樣本,則信號是恒定的。此時,它要么達到一個短暫的常數值但沒有達到峰值,要么已經達到峰值,因此只有在信號開始下降時才考慮峰值狀態。

如果下一個樣本小于存儲在ADC緩沖器中的前一個樣本,則記錄峰值狀態。在另一個循環中重復該過程以找到下一個峰值。

為了計算頻率,我們計算兩個連續峰值之間的時間,并將該時間與預先存儲在IC內部寄存器中的某些閾值進行比較。如果此時間大于較高的閾值,則頻率小于允許的限制。如果此時間小于下限閾值,則頻率大于允許的限制。

由于該設計適用于相對低頻的信號,因此它們通常以每分鐘的脈沖數計算,在此上下文中縮寫為PPM。閾值標記為高 PPM 和低 PPM。

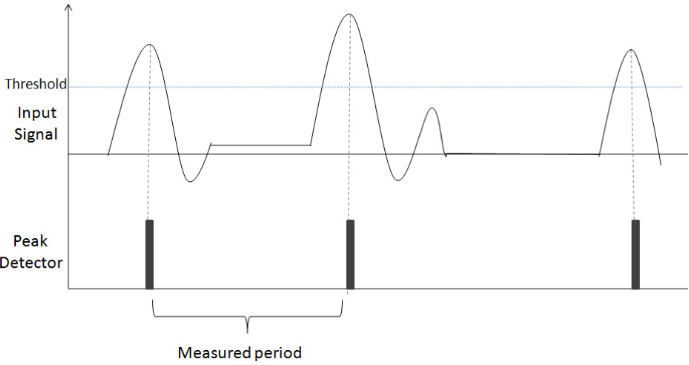

為了確保需要所有記錄的峰值,將每個峰值與預先存儲的電壓閾值進行比較,以便僅在峰值幅度大于所選閾值時才考慮峰值,并忽略短幅度信號。圖 1 顯示了工作過程。

(圖1:系統工作流程)

綠派設計

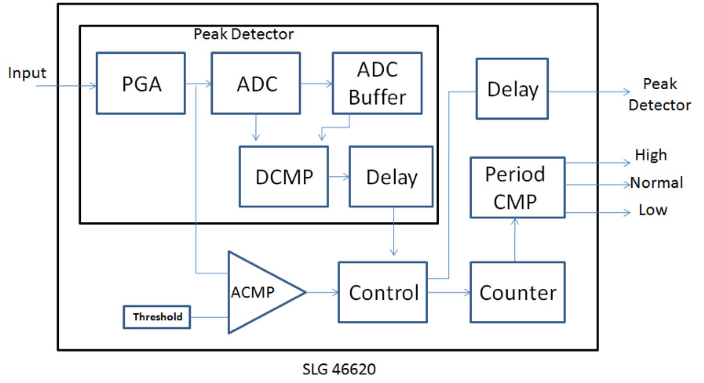

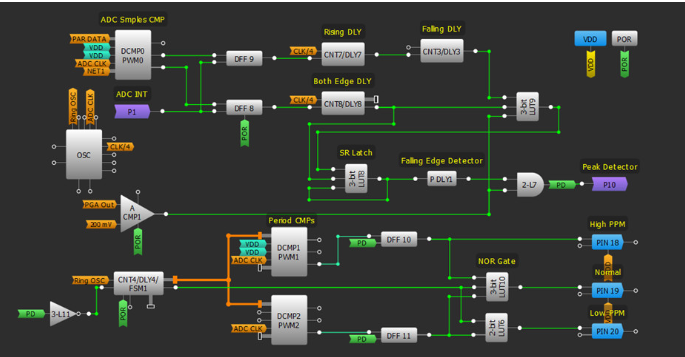

該設計由兩部分組成:峰值檢波器電路和頻率監控電路,后者包含一個定時器和閾值比較器。圖2顯示了該設計的框圖。

(圖2:電路框圖)

峰值檢測器

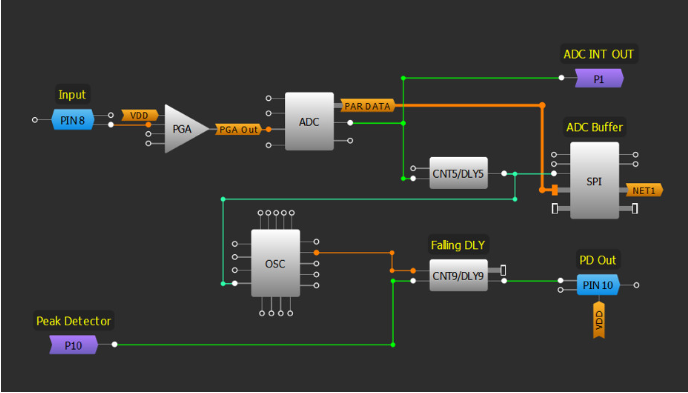

IC通過引腳8接收外部信號,該引腳配置為作為模擬輸入/輸出工作。然后,信號通過設置增益的可編程增益放大器(PGA)。ADC的工作模式為單端,并設置x1增益。然后,信號進入ADC模塊。

在此設計中,輸入信號為低頻,因此通過將時鐘周期除以16來降低采樣速率。采樣率相當于 97,6563 sps,以減少誤差值和尖峰。

采樣率 = PWM 和 ADC 時鐘 / 256 = 25k / 16 / 256

為了指示峰值,必須給出一個信號來指示模擬輸入是上升還是下降。為此,必須比較ADC輸出的兩個連續值。SLG46620V SPI模塊配置為作為ADC緩沖器運行。

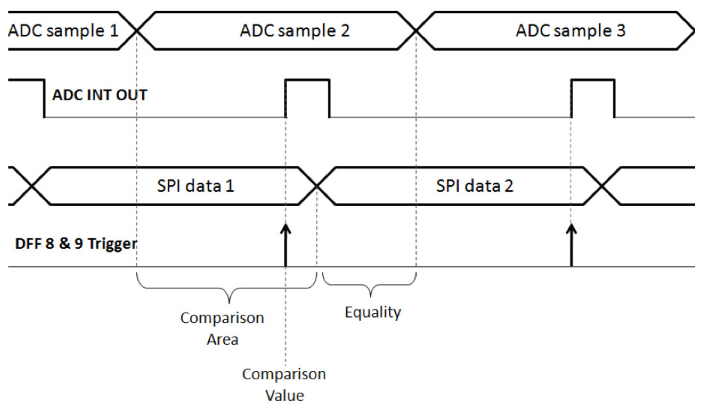

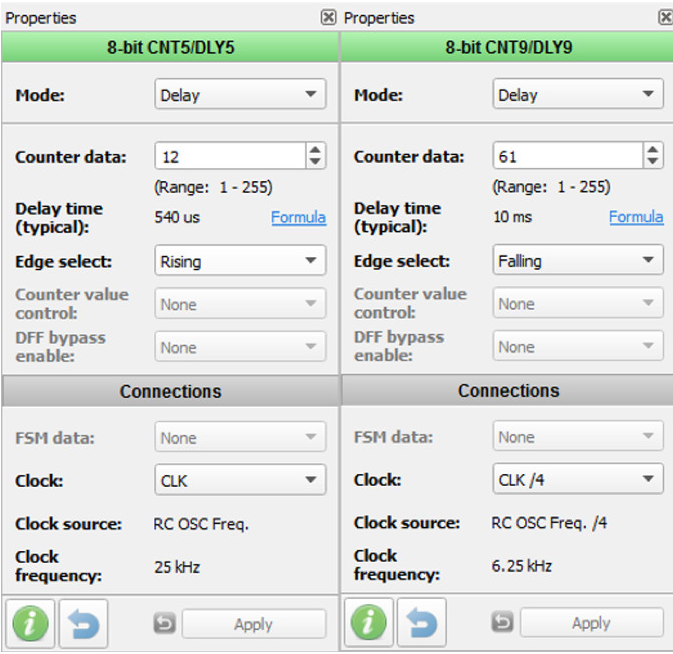

根據數據手冊中的ADC屬性,在ADC INT輸出激活之前,PAR數據可以使用幾個時鐘周期。利用這一特性,ADC INT輸出通過DLY5連接到SPI模塊的SCLK輸入,DLY5配置為作為上升沿延遲工作。因此,需要比較新的ADC值和具有ADC INT輸出信號上升沿的舊ADC值。延遲后,DLY5輸出觸發SPI將新值存儲在緩沖器中。工作時序圖如圖3所示。

(圖3.ADC、SPI 和 DFF 時序圖)

(圖4.綠色PAK設計矩陣0)

通過DCMP0將ADC值與緩沖值進行比較,其中IN+輸入從ADC [7:0]獲取其值,IN-輸入從SPI [7:0]獲取其值。均衡器和OUT+輸出分別連接到DFF8和DFF9。

如果 ADC 值大于 SPI 值,則 OUT+ = 1,EQ = 0。

如果ADC值小于SPI值,則OUT+ = 0,EQ = 0。

如果ADC值等于SPI值,則OUT+ = 0,EQ = 1。

EQ 和 OUT+ 輸出與 ADC INT 輸出信號的上升沿保持。為了確保每次比較時都不會記錄相等狀態,SPI將通過DLY5輸出觸發。因此,比較僅在兩個連續值之間進行,如圖 3 所示。

通過在系統運行期間監控EQ和OUT+輸出的狀態,會引入間歇脈沖,如果不考慮,會導致毛刺。為了防止這種情況并保持穩定的信號,CNT3、CNT7 和 CNT8 作為延遲運行以對系統進行去抖動。因此,可以防止尖峰對輸出狀態的影響。

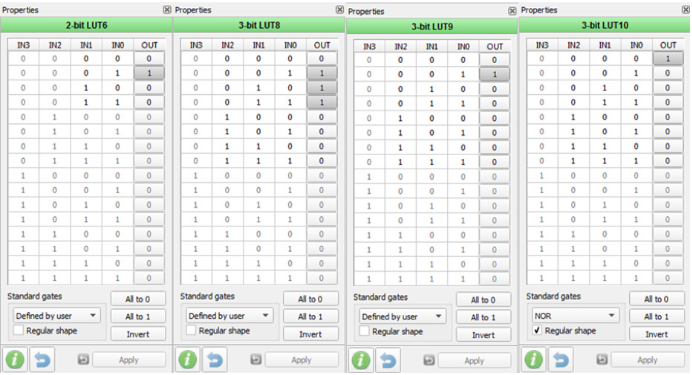

3 位 LUT8 用作 SR 鎖存器,其中來自 OUT+ 輸出的信號表示 Set,表示信號正在上升。復位來自3位LUT9,這意味著信號正在下降。

3L9配置為在OUT+ = 0、EQ = 0且ACMP1輸出為高電平時發出高信號。

優先考慮上升狀態,因為系統的目的是檢測振幅的最高值。

一旦信號在上升狀態后開始下降,3L8輸出將從高電平變為低電平,并通過P DLY1檢測下降沿。P DLY1輸出指示峰值(PD)的檢測。PD信號通過DLY9傳遞到Pin10,脈沖寬度增加,以適應任何外部設備的靈敏度。它還用于重置計數器。

ACMP1用于將PGA輸出與固定閾值進行比較,在本設計中選擇為200 mV。因此,如果峰值的幅度小于邊際值,則將忽略該峰值。

(圖5.綠色PAK設計矩陣1)

峰峰值頻率監視器設計

構建峰值檢波器設計后,我們將使用來自所述設計的PD信號來構建頻率監視器。

FSM1用作計算兩個峰值之間時間的計數器。由于預期信號是低頻,FMS1的時鐘源被選為LF OSC,除以16。因此,測量時間可以在 19 ms 到 2.35 s 之間,步長為 ~10 ms。通過使用低頻振蕩器,有源電流消耗被最小化。

DCMP1 和 DCMP2 將 FSM1 值與頻率上限和下限閾值進行比較。DCMP1將FSM1值與(1:1)寄存器值進行比較,在本設計中設置為500 ms,表示下限閾值。DCMP2將FSM1值與寄存器2值進行比較,在本設計中設置為897 ms。

比較值與PD信號的上升沿一起存儲在DFF10和DFF11中。Q輸出極性已配置為DFF11反相。

FSM1 數據 < 寄存器0 值 ---> DCMP1 輸出+ = 高 ---> DFF10 輸出 = 高 ---> 高 PPM

FSM1 數據 > 寄存器2 值 ---> DCMP2 輸出+ = 高 ---> DFF11 輸出 = 高 ---> 低 PPM

寄存器0 < FSM1 數據 < 寄存器2 ---> 3L10 輸出 = 高電平 --->正常

FSM1 通過 3L11 逆變器以 PD 信號的下降沿復位。如果周期超過 FSM1 工作范圍 2.35 s,FSM1 輸出向 3L10 和 2L6 提供高信號以關閉所有輸出。這種情況表明測量的周期大于預期。此功能可用于指示輸入中沒有脈沖或特定應用處于危險的低周期。FSM的時鐘源可以更改以適應要實現的應用。

(圖6.LUT 屬性)

(圖7.CNT5 & CNT9 Properties)

結果

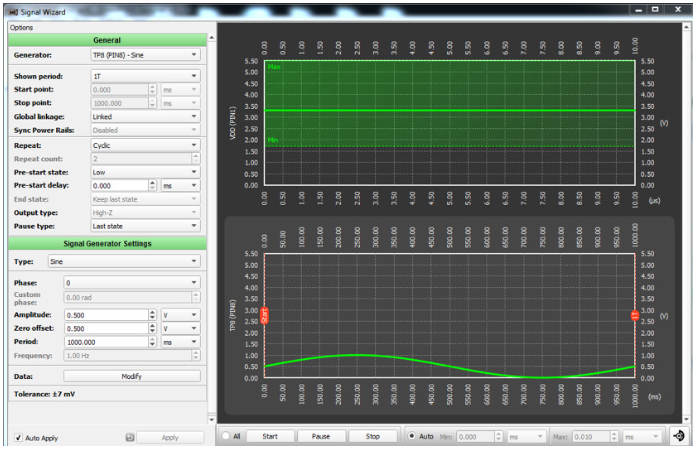

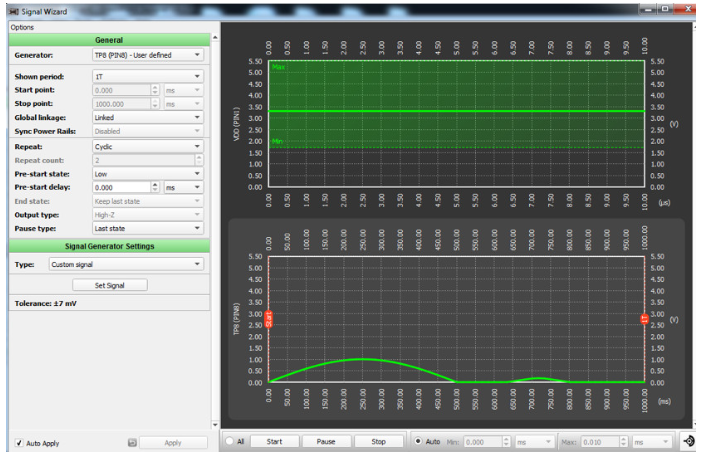

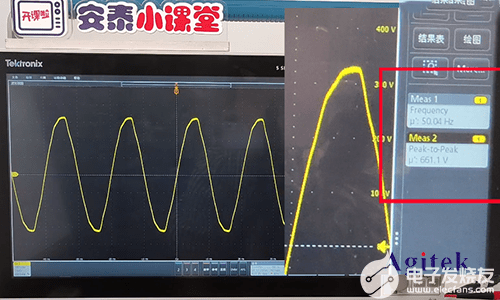

GreenPAK 設計器程序中包含的信號向導已用于檢查設計并確保其按預期工作。

信號向導對于設計檢查非常方便,無需使用外部信號發生器即可生成不同形狀的信號。信號頻率和幅度可以輕松控制。還可以生成自定義信號。

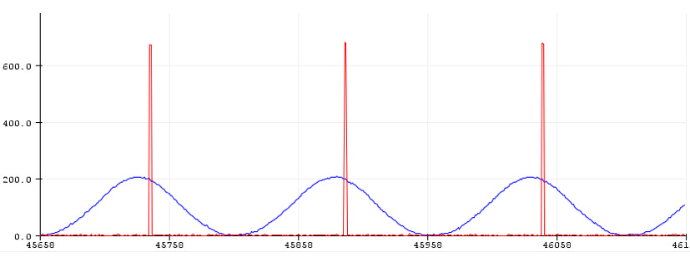

生成了幾個信號。PD信號如下圖所示。

(圖8.CNT5 & CNT9 Properties)

(圖9.藍色信號為輸入,紅色信號為PD輸出信號)

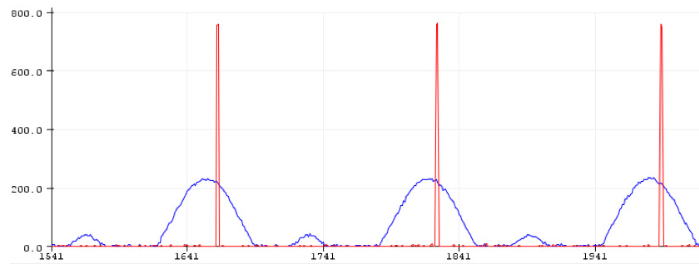

生成具有短不理想峰值的自定義信號。

(圖10.生成自定義信號)

(圖11.藍色信號為輸入,紅色信號為PD輸出信號)

對輸入應用了不同的周期。相應的輸出狀態如表1所示。

表 1:不同周期的輸出狀態

本文概述了如何構建峰值檢測電路,其中包括基于輸入信號峰峰值時間計算的頻率監控電路。該 IC 在集成多個功能方面表現出高效率,因為該項目需要這樣的功能。此外,所選電路的低成本和小面積特別適用于本應用描述中針對的便攜式和可穿戴解決方案。

審核編輯:郭婷

-

傳感器

+關注

關注

2551文章

51163瀏覽量

754120 -

adc

+關注

關注

98文章

6503瀏覽量

544856 -

信號發生器

+關注

關注

28文章

1476瀏覽量

108785

發布評論請先 登錄

相關推薦

想用ths3001id將頻率為25Mhz,峰峰值為3v的正弦波放大到15v峰峰值,請問可以實現嗎?

labview尋找峰峰值

峰峰值測量,模糊控制

信號峰峰值測量

峰峰值雜音測量方法介紹

峰峰值定義_示波器峰峰值怎么看

市電220V說的是峰峰值還是有效值呢

峰峰值頻率監測

峰峰值頻率監測

評論