本次分享華為公司的《大規模邏輯設計指導書》中的內容。

1 目的

本規范的目的是提高書寫代碼的可讀性 可修改性 可重用性 優化代碼綜合和仿真的結 果 指導設計工程師使用VerilogHDL規范代碼和優化電路 規范化公司的ASIC設計輸入從而做到- 邏輯功能正確

- 可快速仿真

- 綜合結果最優( 如果是hardware model)

- 可讀性較好

2 范圍

本規范涉及Verilog HDL編碼風格 編碼中應注意的問題 Testbench的編碼等本規范適用于Verilog model的任何一級 RTL ehavioral, gate_level) 也適用于出于仿真綜合或二者結合的目的而設計的模塊.3 定義

- Verilog HDL:Verilog 硬件描述語言

- FSM:有限狀態機

- 偽路徑:靜態時序分析 STA 認為是時序失敗 而設計者認為是正確的路徑。

4 引用標準和參考資料

下列標準包含的條文 通過在本標準中引用而構成本標準的條文 在標準出版時 所示版本均為有效 所有標準都會被修訂 使用本標準的各方應探討 使用下列標準最新版本的可能性。5規范內容

5.1 Verilog 編碼風格

本章節中提到的Verilog編碼規則和建議適應于 Verilog model的任何一級 RTL behavioral,gate_level) 也適用于出于仿真 綜合或二者結合的目的而設計的模塊5.1.1

選擇有意義的信號和變量名 對設計是十分重要的 命名包含信號或變量諸如出處 有效狀態等基本含義 下面給出一些命名的規則- 用有意義而有效的名字 有效的命名有時并不是要求將功能描述出來 如:

-

For( I = 0; I < 1024; I = I + 1) -

Mem[I] <= #1 32’b0;

-

用連貫的縮寫

長的名字對書寫和記憶會帶來不便 甚至帶來錯誤 采用縮寫時應注意同一信號在模塊中的一致性 縮寫的例子如下Addr :addressPntr :pointerClk :clockRst :reset -

用最右邊的字符下劃線表示低電平有效 高電平有效的信號不得以下劃線表示 短暫 的引擎信號建議采用高有效

如 Rst_ Trdy, Irdy Idsel. -

大小寫原則

名字一般首字符大寫 其余小寫 但parameter, integer 定義的數值名可全部用大寫兩個詞之間要用下劃線連接。如 Packetaddr, Datain, Memwr Memce_ -

全局信號名字中應包含信號來源的一些信息如 D_addr[7:2] 這里的 D 指明了地址是解碼模塊(Decoder module)中的地址

-

同一信號在不同層次應保持一致性

-

自己定義的常數 類型等用大寫標識

如 parameter CYCLE=100 -

避免使用保留字

如 in out x z等不能夠做為變量 端口或模塊名 -

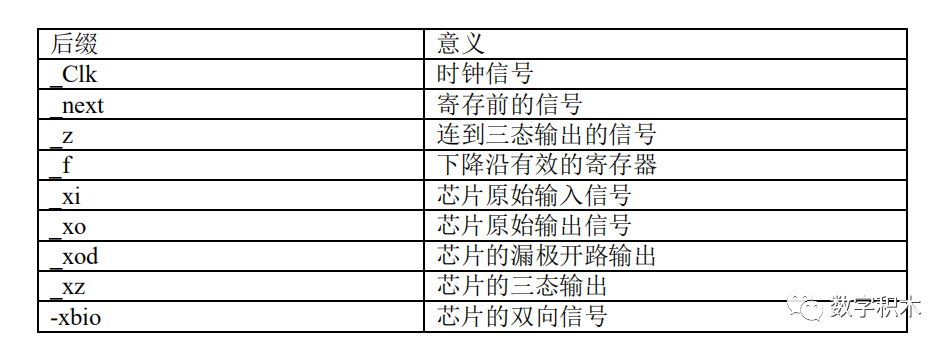

添加有意義的后綴 使信號名更加明確 常用的后綴如下:

5.1.2 Modules

-

頂層模塊應只是內部模塊間的互連

Verilog設計一般都是層次型的設計 也就是在設計中會出現一個或多個模塊 模塊間的調用在所難免 可把設計比喻成樹 被調用的模塊就是樹葉 沒被調用的模塊就是樹根 那么在這個樹根模塊中 除了內部的互連和模塊的調用外 盡量避免再做邏輯 如不能再出現對reg變量賦值等 這樣做的目的是為了更有效的綜合 因為在頂層模塊中出現中間邏輯 Synopsys 的design compiler 就不能把子模塊中的邏輯綜合到最優。 -

每一個模塊應在開始處注明文件名 功能描述 引用模塊 設計者 設計時間及版權信息等,如:

-

Filename﹕ RX_MUX.v -

Author﹕ -

Description﹕ -

Calledby﹕Topmodule -

RevisionHistory﹕99-08-01 -

Revision1.0 -

Email﹕ M@sz.huawei.com.cn -

Company﹕ HuaweiTechnology.Inc -

Copyright(c) 1999, HuaweiTechnologyInc, All right reserved

-

不要對Inpu t進行驅動, 在module 內不要存在沒有驅動的信號 更不能在模塊端口中出現沒有驅動的輸出信號,避免在仿真或綜合時產生warning 干擾錯誤定位。

-

每行應限制在80個字符以內 以保持代碼的清晰 美觀和層次感 一條語句占用一行 如果較長 超出80個字符 則要換行

-

電路中調用的 module名 用 Uxx 標 示 向量大小表 示要清晰 采用基于名字(namebased )的調用而非基于順序的(orderbased),如:

-

InstanceUInstance2( -

.DataOut(DOUT ), -

.DataIn(DIN ), -

.Cs_(Cs_) -

);

-

用一個時鐘的上沿或下沿采樣信號, 不能一會兒用上沿 ,一會兒用下沿 ,如果既要用上沿又要用下沿 ,則應分成兩個模塊設計。建議在頂層模塊中對Clock做一非門,在層次模塊中如果要用時鐘下沿就可以用非門產生的Posedge Clk_, 這樣的好處是在整個設計中采用同一種時鐘沿觸發, 有利于綜合。基于時鐘的綜合策略

-

在模塊中增加注釋

對信號 參量 引腳 模塊 函數及進程等加以說明 便于閱讀與維護 -

Module 名要用大寫標示 且應與文件名保持一致, 如

-

Module DFF_ASYNC_RST( -

Reset, -

Clk, -

Data, -

Qout -

);

-

嚴格芯片級模塊的劃分

只有頂層包括IO引腳(pads) 中間層是時鐘產生模塊 JTAG 芯片的內核(CORE)這樣便于對每個模塊加以約束仿真 對時鐘也可以仔細仿真 -

模塊輸出寄存器化

對所有模塊的輸出加以寄存 如圖1 使得輸出的驅動強度和輸入的延遲可以預測 從而使得模塊的綜合過程更簡單 -

輸出驅動的強度都等于平均的觸發器驅動強度

-

將關鍵路徑邏輯和非關鍵路徑邏輯放在不同模塊

- 將相關的組合邏輯放在同一模塊 有助于DC對其進行優化 因為DC通常不能越過模塊的邊界來優化邏輯。

-

Verilog

+關注

關注

28文章

1351瀏覽量

110074 -

HDL

+關注

關注

8文章

327瀏覽量

47376 -

編碼

+關注

關注

6文章

940瀏覽量

54814 -

代碼

+關注

關注

30文章

4779瀏覽量

68522

原文標題:【華為】verilog語言編寫規范(一)

文章出處:【微信號:ZYNQ,微信公眾號:ZYNQ】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

System Verilog常見問題及語言參考手冊規范

System Verilog問題和語言參考手冊規范

討論Verilog語言的綜合問題

Verilog硬件描述語言參考手冊免費下載

verilog語言編寫規范

verilog語言編寫規范

評論