1.時(shí)鐘樹綜合

2.布局規(guī)劃

3.布線

4.ECO技術(shù)

5.功耗分析

6.信號(hào)完整性的考慮

7.物理驗(yàn)證

8.可制造性設(shè)計(jì)/面向良品率的設(shè)計(jì)

1.時(shí)鐘樹綜合

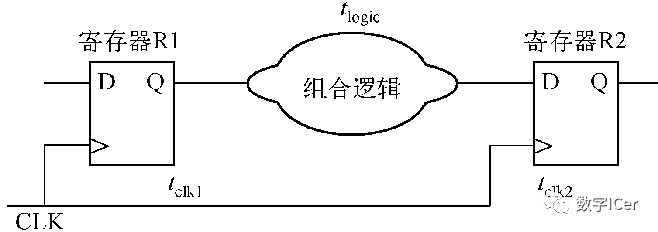

在同步電路中,時(shí)鐘信號(hào)連接所有的寄存器和鎖存器,是整個(gè)電路工作的基本保障。然而從時(shí)鐘的根節(jié)點(diǎn)到每個(gè)寄存器時(shí)鐘端的延時(shí),由于走的路徑不相同,到達(dá)的時(shí)間也不相同

對(duì)時(shí)鐘偏斜的要求

保持(Hold)時(shí)間約束

tclk1 + tcq + min(tlogic) > tclk2 + thold

建立(Setup)時(shí)間約束

T > tsetup + tcq + max(tlogic) - (tclk2 - tclk1)

在滿足保持時(shí)間約束時(shí),越小越好。而要滿足建立時(shí)間約束時(shí),越大越好,這樣可以降低時(shí)鐘周期,提高芯片頻率 。

如何平衡不同時(shí)鐘節(jié)點(diǎn)

時(shí)鐘樹方法的出現(xiàn)使得大型SoC中時(shí)鐘偏斜的問題得以解決在一個(gè)芯片上,沒有必要,也不可能完全消除時(shí)鐘偏斜,只要把時(shí)鐘偏斜控制在合理的范圍內(nèi)就可以了。

時(shí)鐘樹綜合(Clock Tree Synthesis)技術(shù)

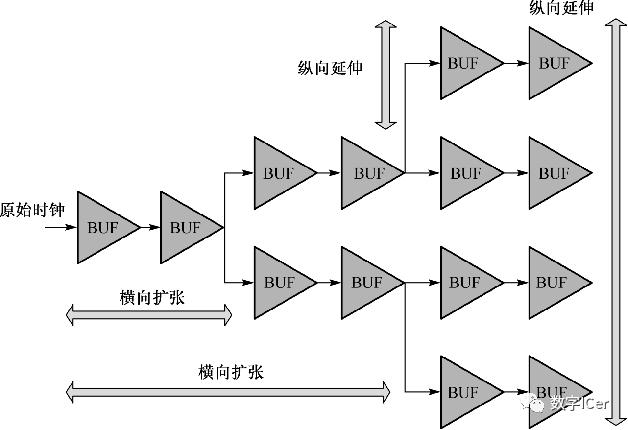

時(shí)鐘樹綜合是指使用EDA工具自動(dòng)生成時(shí)鐘樹,它包括時(shí)鐘緩沖器的插入與時(shí)鐘信號(hào)的布線。

時(shí)鐘緩沖器的插入:時(shí)鐘綜合工具根據(jù)寄存器的位置和數(shù)量,決定插入緩沖器的層數(shù)、驅(qū)動(dòng)力的大小和插入位置

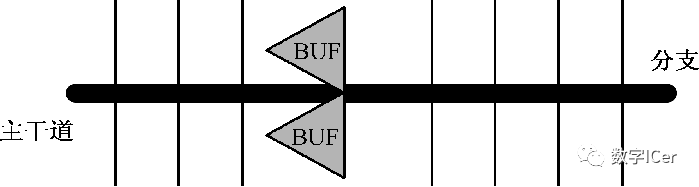

時(shí)鐘線的布線:由于時(shí)鐘線的優(yōu)先級(jí)高于一般信號(hào)線,所以應(yīng)先布時(shí)鐘線。這樣可以讓時(shí)鐘線以最短的路徑連接,避免延時(shí)過大,減少時(shí)鐘偏斜

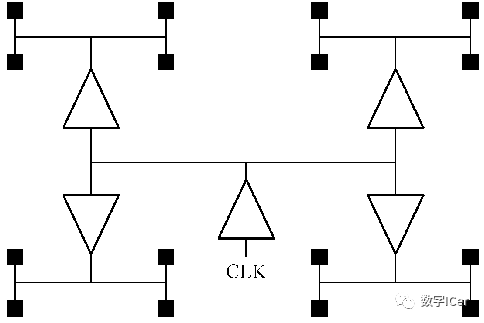

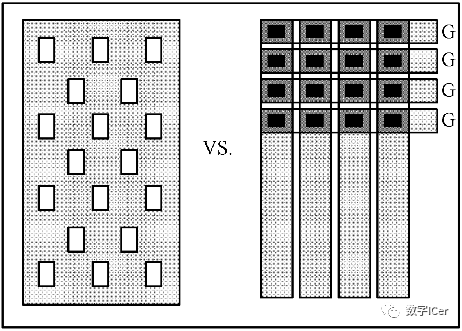

時(shí)鐘網(wǎng)格(Clock Mesh)技術(shù)

時(shí)鐘網(wǎng)格技術(shù)就是預(yù)先在整個(gè)設(shè)計(jì)上搭建時(shí)鐘網(wǎng)格。

時(shí)鐘網(wǎng)格與時(shí)鐘樹的最顯著不同在于,網(wǎng)格類似于主干道,在設(shè)計(jì)中可以用更寬的金屬線去繪制時(shí)鐘網(wǎng)格,同時(shí)設(shè)計(jì)者可以用多個(gè)緩沖器去驅(qū)動(dòng)網(wǎng)格 。

如何降低時(shí)鐘樹上的功耗

減少時(shí)鐘緩沖器的數(shù)量

時(shí)鐘緩沖器盡量插入到門控時(shí)鐘后面

門控時(shí)鐘的方法是將不需要時(shí)將時(shí)鐘關(guān)掉。在進(jìn)行時(shí)鐘樹綜合時(shí)為了降低功耗應(yīng)該盡量將時(shí)鐘信號(hào)緩沖器插在門控時(shí)鐘后

異步電路降低時(shí)鐘樹上的功耗

異步電路的工作模式是“事件驅(qū)動(dòng)”,電路只在需要時(shí)工作,消除了速度浪費(fèi),由于不需同步,沒有全局時(shí)鐘,因此也消除了全局時(shí)鐘樹的功耗。

時(shí)鐘樹設(shè)計(jì)考慮因素

檢查是否在時(shí)鐘通路上有延遲器件。這種器件會(huì)造成時(shí)鐘樹為了平衡最長的時(shí)鐘節(jié)點(diǎn)加過多的時(shí)鐘緩沖器。

檢查是否在時(shí)鐘通路上存在設(shè)為不被優(yōu)化(dont_touch)的器件。這些器件可能會(huì)影響時(shí)鐘樹綜合工具對(duì)時(shí)鐘樹的優(yōu)化。

芯片布局是否可以被調(diào)整使之更加利于時(shí)鐘樹綜合。存在時(shí)鐘相關(guān)的不同模塊應(yīng)該盡量放的近些。

檢查是否可以創(chuàng)建新的時(shí)鐘使之對(duì)時(shí)鐘樹綜合有益。如果在整個(gè)芯片中只有一個(gè)時(shí)鐘源,因?yàn)檫@個(gè)時(shí)鐘源的負(fù)載太大,往往時(shí)鐘通路會(huì)很長。如能在某些節(jié)點(diǎn)上創(chuàng)建不同的時(shí)鐘,可以減少時(shí)鐘樹上的延遲,也就減少了時(shí)鐘樹上的緩沖器數(shù)量。

檢查是否時(shí)鐘樹結(jié)點(diǎn)都是需要同步的。一定要確保時(shí)鐘樹綜合時(shí)只同步那些需要同步的節(jié)點(diǎn)。

在使用時(shí)鐘綜合工具中應(yīng)該盡量設(shè)置插入延時(shí)(Insertion Delay)和時(shí)鐘偏斜為最符合實(shí)際的值,而非0。

盡量只使用時(shí)鐘反相器而非時(shí)鐘緩沖器進(jìn)行時(shí)鐘樹綜合。

2.布局規(guī)劃

一個(gè)好的、提前的布局規(guī)劃會(huì)使得深亞微米設(shè)計(jì)的物理實(shí)現(xiàn)在設(shè)計(jì)周期和設(shè)計(jì)質(zhì)量上都受益匪淺。

從具體內(nèi)容上看,布局規(guī)劃包括版圖上的電源規(guī)劃和模塊的布局規(guī)劃。

電源規(guī)劃可以幫助確保片上單元具有足夠的電源與地連接。在很多情況下,尤其對(duì)于復(fù)雜的SoC設(shè)計(jì),設(shè)計(jì)規(guī)劃應(yīng)當(dāng)與源代碼開發(fā)并行進(jìn)行,布局和電源估計(jì)的優(yōu)化可以與代碼優(yōu)化一同完成。

布局規(guī)劃策略

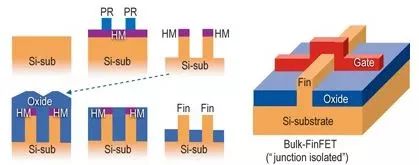

在進(jìn)行布局規(guī)劃時(shí),考慮一些制程工藝的基本特性是很重要的。

一個(gè)典型的基本單元庫定義的單元行是水平的,版圖上每層布線的方向遵循交互的圖案,第1層水平,第2層豎直等。由于第1層金屬常常用來在標(biāo)準(zhǔn)單元內(nèi)部布線,或者為單元行提供電源,所以它作為常規(guī)布線的能力是有限的。

當(dāng)為芯片和模塊建立金屬環(huán)(通常作為供電或噪聲隔離的需要)的時(shí)候,要給布線留下足夠的空間。將金屬線布進(jìn)模塊內(nèi)部的時(shí)候,設(shè)計(jì)者應(yīng)該留心模塊內(nèi)部的障礙情況,以避免模塊角落產(chǎn)生擁塞。

在任何物理設(shè)計(jì)工作中,理解目標(biāo)制程工藝的要求十分重要。例如,最大金屬線寬度的限制。電源環(huán)和地線環(huán)通常需要很寬,以滿足芯片各部分的供電需要。

為了避免最大金屬線寬度的限制,采用 “總線”式布線更可取。

應(yīng)用規(guī)劃步驟

芯片級(jí)布局規(guī)劃:從外圍的I/O開始做布局規(guī)劃具有一定的代表性(依賴于封裝設(shè)計(jì))。

模塊級(jí)布局規(guī)劃 :進(jìn)行初步的綜合以確定模塊中所有基本單元的面積。

電源預(yù)算:在貫穿設(shè)計(jì)的過程中計(jì)算模塊級(jí)的功率消耗以判斷設(shè)計(jì)是否滿足指定的功率預(yù)算是很重要的,而且在布局規(guī)劃中要估算電源網(wǎng)格的尺寸。

電源規(guī)劃和分析

3.布線

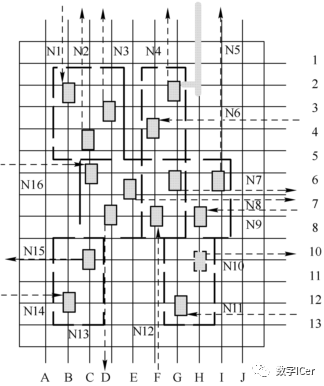

布線是在版圖上將已經(jīng)放好的單元連接在一起的過程。

布線工具根據(jù)布局的信息來連接單元。在通常情況下,布線工具需要縮短布線長度,均勻分布布線并滿足時(shí)序的要求。

布線是一個(gè)運(yùn)算密集型的處理,需要大量的細(xì)節(jié)數(shù)據(jù),并且在各種繞線策略間權(quán)衡。

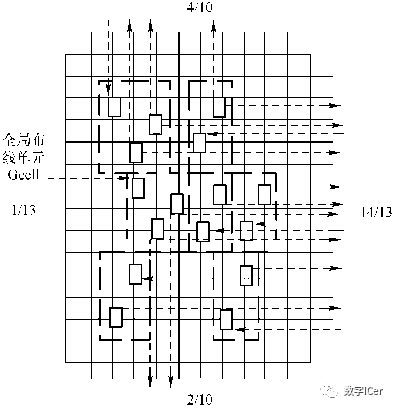

布線流程

全局布線

通道分配

詳細(xì)布線

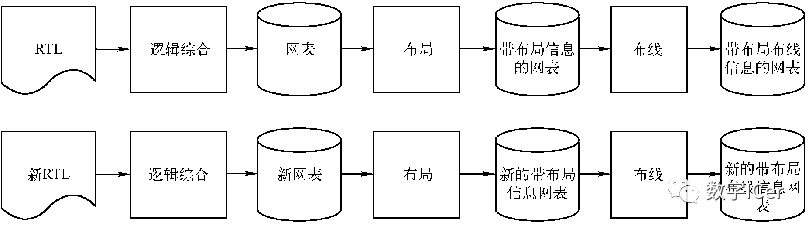

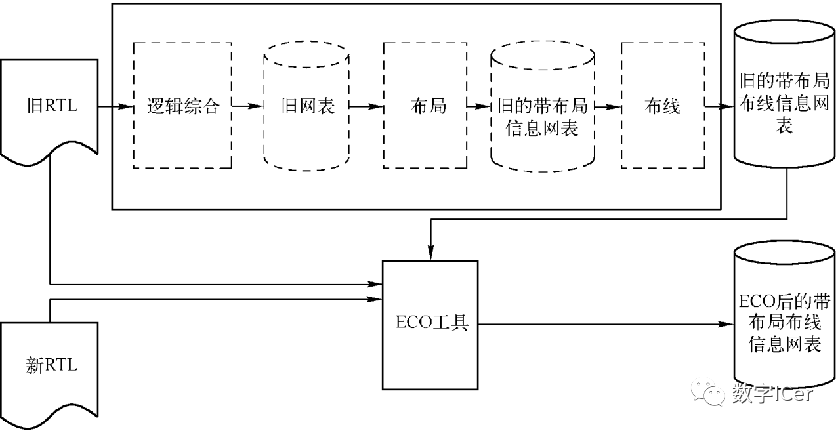

4.ECO技術(shù)

ECO(Engineering Change Order),主要是針對(duì)靜態(tài)時(shí)序分析和后仿真中出現(xiàn)的問題,對(duì)電路和單元布局進(jìn)行小范圍的改動(dòng)。

ECO分為兩種:功能性的ECO和非功能性的ECO。

ECO技術(shù)的設(shè)計(jì)流程

ECO技術(shù)的優(yōu)點(diǎn)

設(shè)計(jì)時(shí)間縮短,對(duì)局部范圍的功能調(diào)整不需要重新做一遍后端設(shè)計(jì)流程;

調(diào)整結(jié)果具備預(yù)測(cè)性,相對(duì)于重新做一遍后端設(shè)計(jì)流程,ECO方案可以基本確保大部分功能與原先的方案的一致性,從而降低后端設(shè)計(jì)失敗的風(fēng)險(xiǎn)。

詳情請(qǐng)查看:芯片設(shè)計(jì)中的ECO是什么?

5.功耗分析

功耗分析可以分成兩種:靜態(tài)功耗分析和動(dòng)態(tài)功耗分析。

靜態(tài)功耗分析可以根據(jù)標(biāo)準(zhǔn)單元及IP的靜態(tài)功耗參數(shù)估算出來。

動(dòng)態(tài)功耗分析與所用的測(cè)試向量有關(guān),需要在布線完成后進(jìn)行。

電壓降(IR Drop)分析

由于供電流在金屬線網(wǎng)上進(jìn)行傳導(dǎo),而金屬線網(wǎng)本身存在電阻值,在電流通過金屬網(wǎng)絡(luò)時(shí),必然帶來電壓降。

如果不進(jìn)行電壓降分析,若芯片某一個(gè)部分供電不足,將導(dǎo)致性能的惡化,從而導(dǎo)致整個(gè)芯片功能的錯(cuò)誤。通過電壓降分析,可以了解到整個(gè)電源網(wǎng)絡(luò)的供電情況,從而進(jìn)行合理的供電網(wǎng)絡(luò)規(guī)劃,以保證芯片功能不會(huì)因?yàn)楣╇妴栴}產(chǎn)生影響。

一般來說要把整個(gè)芯片的電壓降控制在電源電壓的10%以內(nèi)。

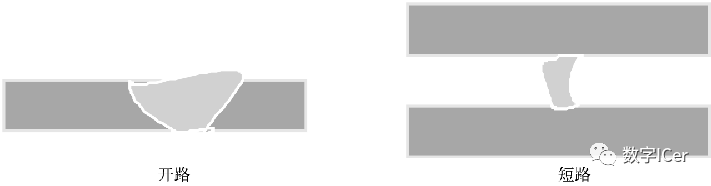

電遷移(Electromigration)分析

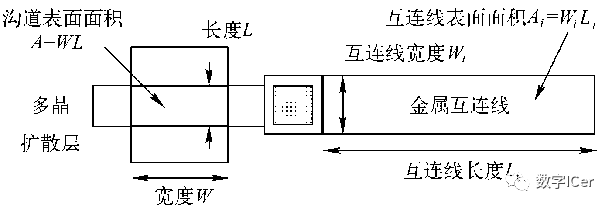

在決定供電網(wǎng)絡(luò)金屬線寬度的時(shí)候,需要滿足由代工廠工藝庫中提供的電流密度規(guī)則。

若電流密度過大,而金屬線寬過小,將導(dǎo)致電遷移現(xiàn)象出現(xiàn)。

而電遷移會(huì)導(dǎo)致金屬線的斷裂,損壞整個(gè)芯片,因此,對(duì)電遷移進(jìn)行分析,也是必須的一個(gè)步驟,對(duì)于不滿足EM規(guī)則的金屬線,需要加大線寬。

6.信號(hào)完整性的考慮

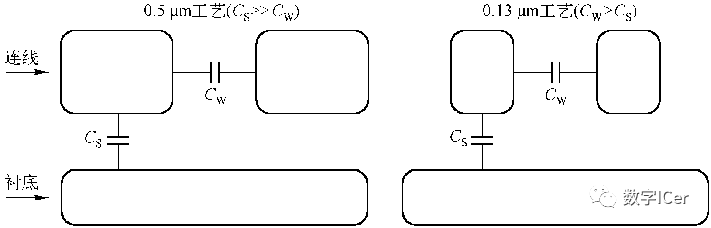

隨著先進(jìn)的深亞微米制程在不斷進(jìn)步,使得互連線上的耦合電容、電阻增大,同時(shí)更大的電流密度和更低的電壓引起的信號(hào)完整性問題成為新的挑戰(zhàn)。如果沒有得到充分重視,這些效應(yīng)會(huì)導(dǎo)致芯片功能失效和出現(xiàn)可靠性問題。

為了處理這些信號(hào)完整性的影響,在物理實(shí)現(xiàn)的每一個(gè)階段都需要引入大量的經(jīng)過優(yōu)化的物理互連拓?fù)浣Y(jié)構(gòu)和驅(qū)動(dòng)的模型。

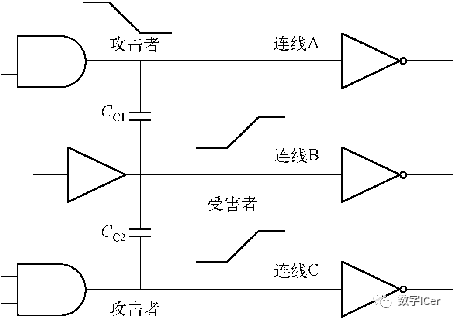

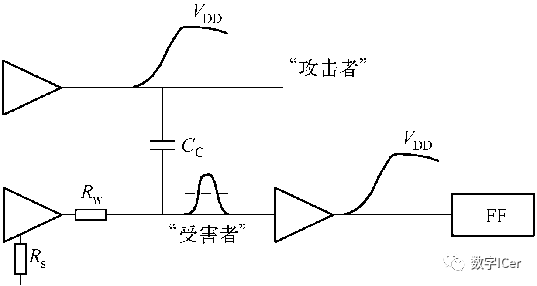

串?dāng)_

兩條緊鄰線路的翻轉(zhuǎn)時(shí)間在時(shí)間域上重疊的話,會(huì)導(dǎo)致串?dāng)_引起的延時(shí)。躍遷的相對(duì)方向決定了路徑比預(yù)先的變快還是變慢。

串?dāng)_引起的噪聲會(huì)給相鄰的線路中注入電壓針刺型干擾。如果干擾電壓超過了翻轉(zhuǎn)閾值,將會(huì)引起錯(cuò)誤的躍遷,造成潛在的錯(cuò)誤行為。

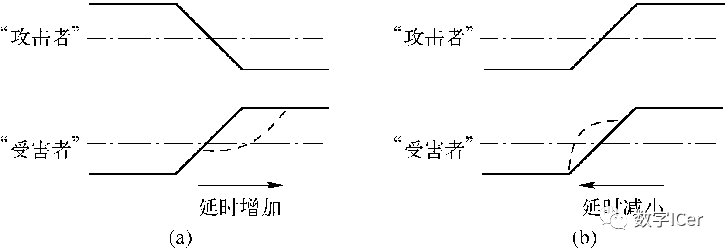

串?dāng)_引起的延遲

由于電容性的耦合,發(fā)生在攻擊者上的躍遷會(huì)部分傳遞給“受害者”,這會(huì)使“受害者”的躍遷波形發(fā)生意外的扭曲,從而導(dǎo)致“受害者”測(cè)量得到的延時(shí)發(fā)生變化。

轉(zhuǎn)換方向相反,延時(shí)增加,導(dǎo)致建立時(shí)間的錯(cuò)誤。

轉(zhuǎn)換方向相同,延時(shí)減小,導(dǎo)致保持時(shí)間的錯(cuò)誤。

串?dāng)_引起的噪聲

除了影響時(shí)序,耦合性的電容還可以造成功能失效。當(dāng)攻擊者在“受害者”附近翻轉(zhuǎn)時(shí),它會(huì)造成“受害者”上面意外的信號(hào)翻轉(zhuǎn)或者邏輯失效,這些被稱為串?dāng)_造成的噪聲

壓降和電遷移

壓降:電源網(wǎng)絡(luò)上的電阻和瞬間的電流抽取都會(huì)造成基本單元上的電壓下降。這種電壓上的降低會(huì)使單元的延時(shí)增大,潛在地造成建立時(shí)間錯(cuò)誤。

電遷移:在大電流密度下會(huì)產(chǎn)生電動(dòng)力,使電子在金屬晶格結(jié)構(gòu)中對(duì)原子產(chǎn)生很大的沖擊,產(chǎn)生電遷移現(xiàn)象。

7.物理驗(yàn)證

在將芯片版圖正式交付代工廠之前,還需要經(jīng)過一個(gè)重要的步驟,這就是物理驗(yàn)證。

通常所說的物理驗(yàn)證是指檢查其設(shè)計(jì)是否滿足設(shè)計(jì)規(guī)則(DRC,Design Rule Check)及確定版圖與邏輯門網(wǎng)表之間的一致性(LVS,Layout Vs Schematics)。

設(shè)計(jì)規(guī)則檢查(DRC)

常見的金屬規(guī)則如下:

金屬的最小寬度

同層金屬之間的最小間距

金屬包圍多晶或通孔的最小面積

金屬包圍多晶或通孔的最小延伸長度

金屬本身的最小面積

同層金屬的最小密度

常見的通孔規(guī)則如下:

通孔的最小面積

同層通孔之間的最小間距

版圖與原理圖的一致性檢查(LVS)

LVS是驗(yàn)證版圖與原理圖是否一致。工程師設(shè)計(jì)的版圖是根據(jù)原理圖在硅片上的具體幾何形狀的實(shí)現(xiàn)。在這里原理圖就是布線后導(dǎo)出的邏輯門網(wǎng)表,版圖就是同時(shí)導(dǎo)出的GDSII格式的版圖文件。

對(duì)于基于標(biāo)準(zhǔn)單元的設(shè)計(jì),LVS主要驗(yàn)證其中的單元有沒有供電,連接關(guān)系是否與邏輯網(wǎng)表一致。

8.可制造性設(shè)計(jì)/面向良品率的設(shè)計(jì)

DFM/DFY的基本概念

可制造性設(shè)計(jì)是指將工藝技術(shù)應(yīng)用于電路設(shè)計(jì)過程中,從而提高產(chǎn)品制造過程的可靠性,但可制造本身并不能保證高良品率。

面向良品率的設(shè)計(jì)是DFM的一部分,其解決方案是將良品率定義為一個(gè)設(shè)計(jì)指標(biāo),主要在版圖設(shè)計(jì)前后考慮電路的功能質(zhì)量問題,

通過將設(shè)計(jì)和生產(chǎn)工藝相結(jié)合,保證產(chǎn)品的高良品率。

DFM/DFY方法

掩模綜合工具(Mask Synthesis Tools)實(shí)施分辨率增強(qiáng)技術(shù)(RET)

光學(xué)臨近修正(OPC)和移相掩模(PSM)

變化圖像

前提是我們了解印刷工藝會(huì)導(dǎo)致圖像失真,而且了解失真的方式,然后按照失真相反的方向使原圖失真

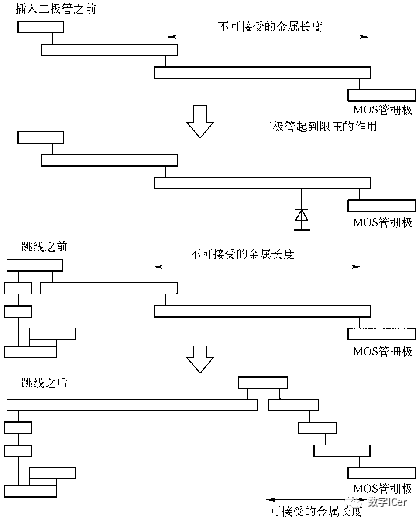

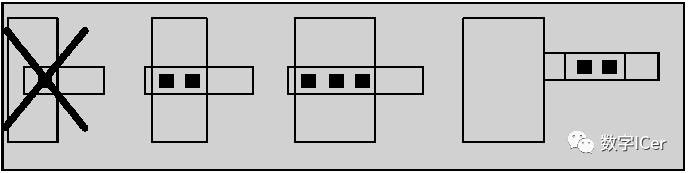

天線效應(yīng)

天線效應(yīng)主要是在互連線的制造過程中,產(chǎn)生負(fù)電荷的聚集,這些負(fù)電荷將傳到與其相連接的MOS管的氧化柵極擊穿使得MOS管的氧化柵極擊穿,影響到MOS管的工作。

解決天線效應(yīng)的方法

在違反規(guī)則的金屬所連接到的MOS管柵極上加一個(gè)二極管將制造過程中聚集到MOS的管柵極上的負(fù)電荷及時(shí)地釋放掉。

替換金屬層,即跳線,特別是要限制Metal1到MOS的管柵極的長度,以此來減少負(fù)電荷的聚集量。

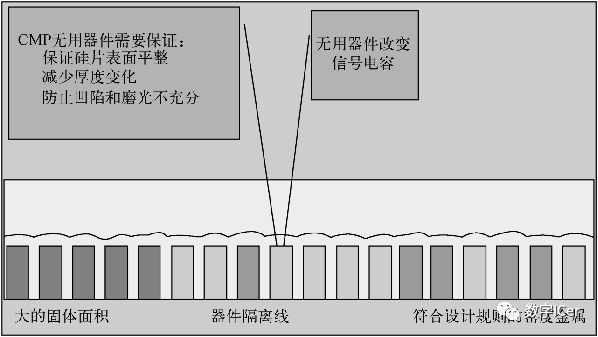

化學(xué)/機(jī)械拋光的考慮

在硅片制作過程中,需要完成化學(xué)/機(jī)械拋光(CMP,Chemical Mechanical Polish)的步驟。在布局密度有較大差異的不同區(qū)域,拋光程度也會(huì)相應(yīng)有所差別。

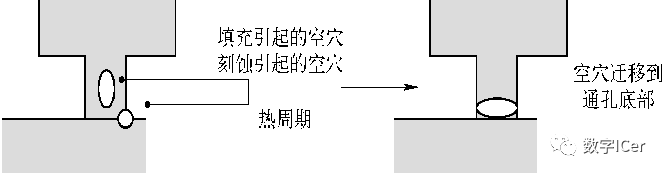

金屬通孔(VIA)失效影響

由于130 nm以下工藝采用銅互連線技術(shù),尺寸的進(jìn)一步減小,金屬導(dǎo)線上的空洞(Voids)在熱應(yīng)力的作用下會(huì)向金屬通孔(VIA)中流動(dòng),從而造成連接斷路。

多金屬通孔方法

用于加倍通孔而多出的金屬將會(huì)增加金屬的臨界面積,對(duì)于使用低介電常數(shù)材料的技術(shù),這一工藝步驟可能會(huì)導(dǎo)致應(yīng)力增加并最終使介電層開裂,良率也會(huì)下降

審核編輯:湯梓紅

-

布線

+關(guān)注

關(guān)注

9文章

773瀏覽量

84357 -

鎖存器

+關(guān)注

關(guān)注

8文章

906瀏覽量

41542 -

時(shí)鐘樹

+關(guān)注

關(guān)注

0文章

55瀏覽量

10774 -

時(shí)鐘網(wǎng)格

+關(guān)注

關(guān)注

0文章

3瀏覽量

5732

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字IC后端設(shè)計(jì)介紹,寫給哪些想轉(zhuǎn)IC后端的人!

介紹RTL設(shè)計(jì)引入的后端實(shí)現(xiàn)過程中的布線問題

后端系統(tǒng),后端系統(tǒng)是什么意思

數(shù)字后端關(guān)于Litho Grid基本概念介紹詳解

介紹數(shù)字后端概念--Shape Blockage

數(shù)字后端基本概念介紹

IC設(shè)計(jì)前后端流程與EDA工具介紹

如何理解Web前端和后端的工作內(nèi)容和區(qū)別?

Spring Microservices in Action,前端后端開發(fā)必備書籍

nodejs 后端技術(shù)介紹

數(shù)字后端基本概念介紹—FinFET Grid

后端基礎(chǔ)入門介紹

后端基礎(chǔ)入門介紹

評(píng)論