人們常常想當(dāng)然地為PCB的電路上電,殊不知這可能造成破壞以及有損或無損閂鎖狀況。這些問題可能并不突出,直到量產(chǎn)開始,器件和設(shè)計的容差接受檢驗時才被發(fā)現(xiàn),但為時已晚,項目和產(chǎn)品的時間及交貨將會受到極大影響,成本大幅攀升。為了解決這一階段中發(fā)現(xiàn)的錯誤,將需要進行大量修改,包括PCB布局變更、設(shè)計更改和額外的異常現(xiàn)象等。

隨著集成電路時代的到來,許多功能模塊被集成到一個IC中,因而需要利用多個電源為這些模塊供電。這些電源的電壓有時候相同,但更多時候是不同的。市場上的片上系統(tǒng)(SoC) IC越來越多,這就產(chǎn)生了對電源進行時序控制和管理的需求。

本應(yīng)用筆記討論設(shè)計工程師在新設(shè)計中必須考慮的某些更微妙的電源問題,特別是當(dāng)IC需要多個不同的電源時。目前,一些較常用的電源電壓是:+1.8V、+2.0V、+2.5V、+3.3V、+5V、?5V、+12V和?12V。

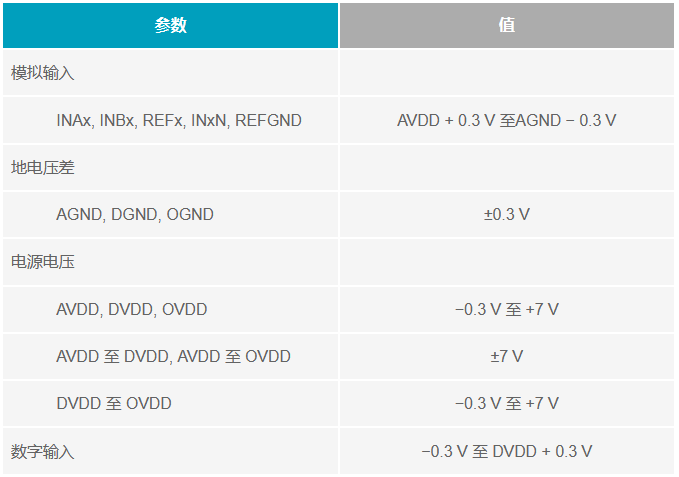

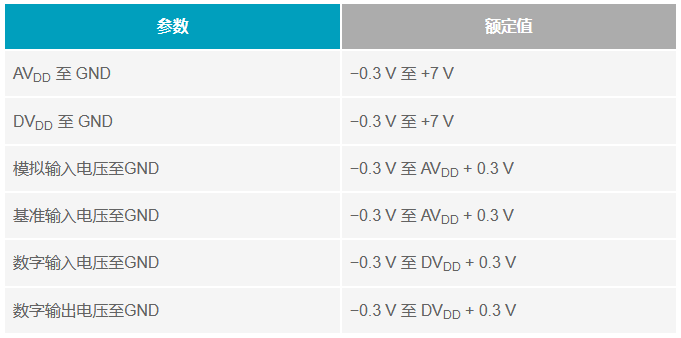

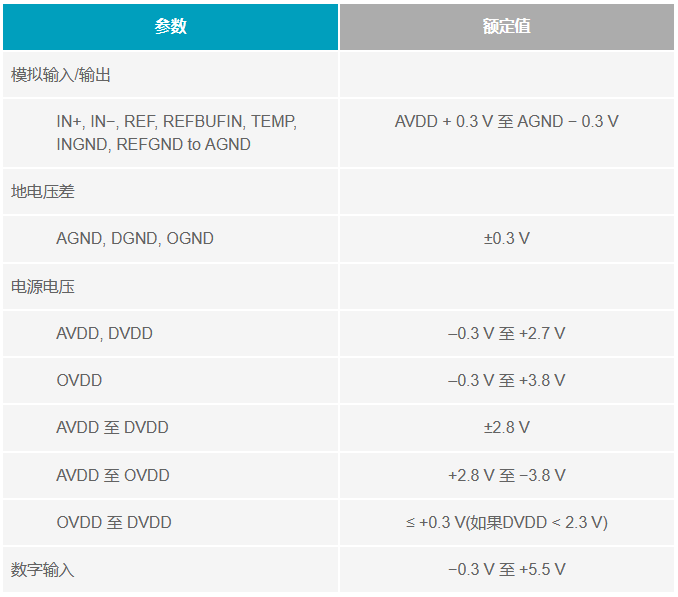

ADI公司的所有數(shù)據(jù)手冊都含有“絕對最大額定值”(AMR)部分,它說明為避免造成破壞,對引腳或器件可以施加的最大電壓、電流或溫度。AD7654PulSAR 16位ADC是采用三個(或更多)獨立電源的混合信號ADC的范例。這些ADC需要數(shù)字電源(DVDD)、模擬電源(AVDD)和數(shù)字輸入/輸出電源(OVDD)。它們是ADC,用于將模擬信號轉(zhuǎn)換成數(shù)字代碼,因此需要一個模擬內(nèi)核來處理傳入的模擬輸入。數(shù)字內(nèi)核負責(zé)處理位判斷過程和控制邏輯。I/O內(nèi)核用于設(shè)置數(shù)字輸出的電平,以便與主機邏輯接口(電平轉(zhuǎn)換)。ADC的電源規(guī)格可以在相應(yīng)數(shù)據(jù)手冊的“絕對最大額定值”部分找到。表1摘自AD7654 (Rev. B)數(shù)據(jù)手冊的“絕對最大額定值”部分。

表1. AD7654的絕對最大額定值(Rev. B)注意,表1中所有三個電源的范圍都是?0.3V至+7V。相對于DVDD和OVDD,AVDD的范圍是+7V至?7V,這就確認了AVDD和DVDD無論哪一個先上電都是可行的。此外,AVDD和OVDD無論哪一個先上電也是可行的。然而,DVDD與OVDD之間存在限制。技術(shù)規(guī)格規(guī)定,OVDD最多只能比DVDD高0.3V,因此DVDD必須在OVDD之前或與之同時上電。如果OVDD先上電(假設(shè)5V),則DVDD在上電時比OVDD低5V,這不符合“絕對最大額定值”要求,可能會損壞器件。模擬輸入INAx、INBx、REFx、INxN和REFGND的限制是:這些輸入不得超過AVDD +0.3V或AGND ?0.3V。這說明,如果模擬信號或基準(zhǔn)電壓源先于AVDD存在,則模擬內(nèi)核很可能會上電到閂鎖狀態(tài)。這通常是一種無損狀況,但流經(jīng)AVDD的電流很容易逐步升至標(biāo)稱電流的10倍,導(dǎo)致ADC變得相當(dāng)熱。這種情況下,內(nèi)部靜電放電(ESD)二極管變?yōu)檎M而使模擬電源上電。為解決這個問題,輸入和/或基準(zhǔn)電壓源在ADC上電時應(yīng)處于未上電或未連接狀態(tài)。

同樣,數(shù)字輸入電壓范圍為?0.3V至DVDD +0.3V。這說明,數(shù)字輸入必須小于DVDD +0.3V。因此,在上電時,DVDD必須先于微處理器/邏輯接口電路或與之同時上電。與上述模擬內(nèi)核情況相似,這些引腳上的ESD二極管也可能變?yōu)檎箶?shù)字內(nèi)核上電到未知狀態(tài)。

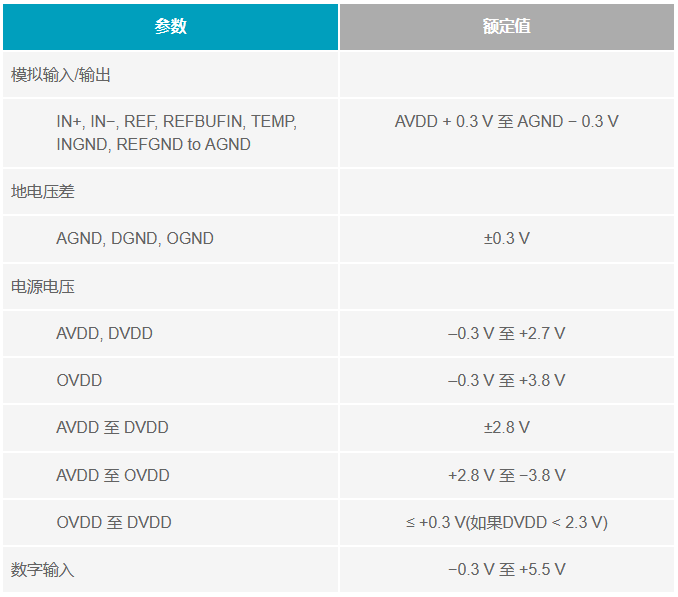

AD7621、AD7622、AD7623、AD7641和AD7643等PulSAR ADC速度更快,是該系列的新型器件,采用更低的2.5V電源(AD7654則采用5V電源)。AD7621和AD7623具有明確規(guī)定的上電序列。表2摘自AD7621 (Rev.0)數(shù)據(jù)手冊的“絕對最大額定值”部分。

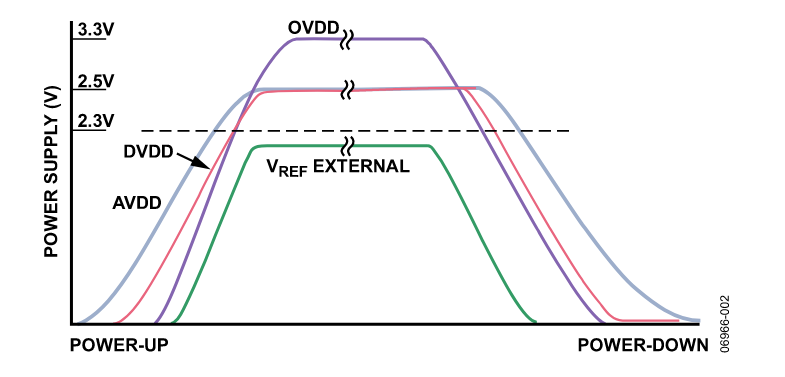

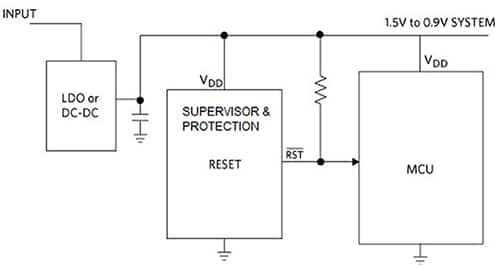

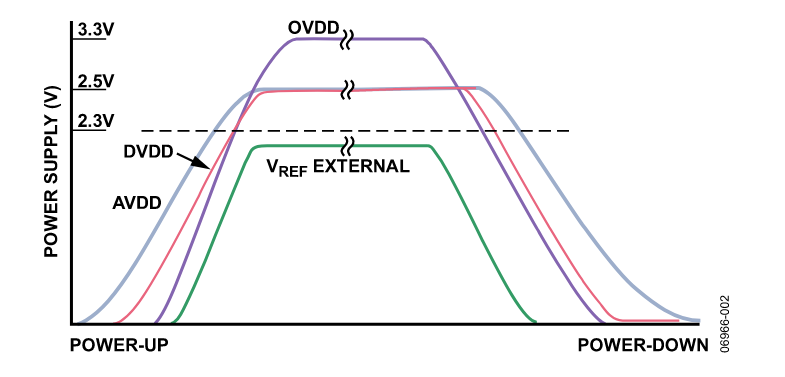

表2. AD7621的絕對最大額定值(Rev. 0)同樣,OVDD與DVDD之間存在限制。“絕對最大額定值”規(guī)定:OVDD必須小于或等于DVDD+0.3V,而DVDD則必須小于2.3V。一旦DVDD在上電期間達到2.3V,該限制便不再適用。如果不遵守該限制,AD7621(和AD7623)可能會受損(見圖1)。

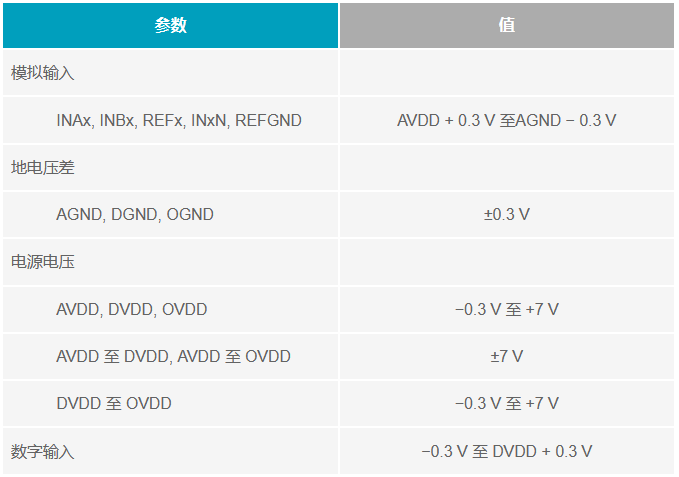

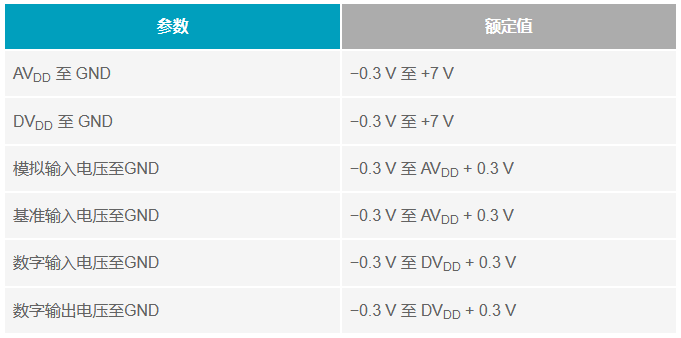

圖1. 可能的上電/關(guān)斷序列—AD7621 (Rev. 0)因此,一般上電序列可能是這樣的:AVDD、DVDD、OVDD、VREF。但是,每個應(yīng)用都不一樣,需要具體分析。注意,器件關(guān)斷與器件上電同樣重要,切記遵守同樣的規(guī)格要求。圖1所示為AD7621的典型上電/關(guān)斷序列。對于這些ADC,模擬輸入和基準(zhǔn)電壓源的情況與上文所述相同。對任何模擬輸入引腳施加電壓都可能導(dǎo)致ESD二極管變?yōu)檎瑥亩鼓M內(nèi)核上電到未知狀態(tài)。這些ADC的數(shù)字輸入和輸出略有不同,因為這些器件應(yīng)支持5 V數(shù)字輸入。這些ADC是AD7654的速度升級版本,數(shù)字輸入和輸出均與OVDD電源相關(guān),因為它能支持更高的3.3V電壓。注意:數(shù)字輸入限制為5.5V,而AD7654則為DVDD+0.3V。AD7794 Σ-Δ型24位ADC是另一個很好的例子。表3摘自AD7794 (Rev. D)數(shù)據(jù)手冊的“絕對最大額定值”部分。

表3. AD7794的絕對最大額定值(Rev. D)該ADC的問題與基準(zhǔn)電壓有關(guān),它必須小于AVDD+ 0.3 V。因此,AVDD必須先于基準(zhǔn)電壓或與之同時上電。

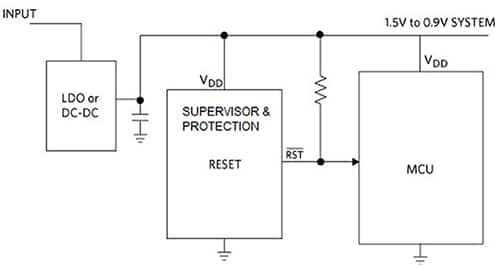

ADI公司提供許多電源時序控制器件。一般而言,其工作原理是:當(dāng)?shù)谝粋€調(diào)節(jié)器的輸出電壓達到預(yù)設(shè)閾值時,就會開始一段時間延遲,延遲結(jié)束后才會使能后續(xù)調(diào)節(jié)器上電。關(guān)斷期間的程序與此相似。時序控制器也可以用于控制電源良好信號等邏輯信號的時序,例如:對器件或微處理器施加一個復(fù)位信號,或者簡單地指示所有電源均有效。

如今大部分要求高速和低功耗的電路PCB上都需要多個電源,例如:+1.8V、+2.0V、+2.5V、+3.3V、+5V、?5V、+12V和?12V。為PCB上的這些電源供電并不是一件輕而易舉的事情。必須仔細分析,設(shè)計一個正確可靠的上電和關(guān)斷序列。采用分立設(shè)計變得越來越困難,解決之道就是采用電源時序控制IC,只要改變一下代碼就能改變上電順序,而不用變更PCB布局布線。

原文標(biāo)題:多電源IC的上電時序控制你搞明白了么?

文章出處:【微信公眾號:亞德諾半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

原文標(biāo)題:多電源IC的上電時序控制你搞明白了么?

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

相關(guān)推薦

變化,滿足了日益增長的音視頻系統(tǒng)應(yīng)用需求。 電源時序器1.0:基礎(chǔ)的時序控制 最初,電源

![的頭像]() 發(fā)表于

發(fā)表于 12-20 09:32

?123次閱讀

1、關(guān)于ADS8698有上電時序要求嗎?AVDD和DVDD 以及軟件配置引腳間的順序有時序要求嗎?

2、觸發(fā)內(nèi)部基準(zhǔn)電壓的條件有哪些?AVDD?還是有別的觸發(fā)源,如果內(nèi)部基準(zhǔn)觸發(fā)不了

發(fā)表于 11-19 06:12

連在一起,形成-5V提供給VA-;

難道這三路電源上電,有嚴(yán)格的時序要求嗎,為什么-5V,容易出現(xiàn)導(dǎo)致IC發(fā)熱不能正常工作,如何避免這個

發(fā)表于 10-30 07:03

按照TAS5711的datasheet中的上電時序進行上電,芯片正常工作,但是無法編輯寄存器,是時序

發(fā)表于 10-22 06:58

電子發(fā)燒友網(wǎng)站提供《雙電源電壓DSP的電源時序控制解決方案.pdf》資料免費下載

發(fā)表于 10-11 11:33

?0次下載

電子發(fā)燒友網(wǎng)站提供《FPGA電源時序控制.pdf》資料免費下載

發(fā)表于 08-26 09:25

?0次下載

有一個項目中用到OPA192這個放大器,有兩個問題:

1.V+是+12V供電的,V-是-12V供電的,想問下+12V和-12V這兩個電有沒有什么必須的上電時序需要

發(fā)表于 07-29 08:30

電源時序器和控制繼電器是兩種不同的電子設(shè)備,電源時序器通過控制繼電器實現(xiàn)對

![的頭像]() 發(fā)表于

發(fā)表于 07-08 14:30

?589次閱讀

電源時序器是一種電子設(shè)備,用于控制多個電源的開啟和關(guān)閉順序,以確保設(shè)備按照正確的順序啟動和關(guān)閉。電源時序

![的頭像]() 發(fā)表于

發(fā)表于 07-08 14:19

?757次閱讀

電源時序器是一種用于控制多個電源設(shè)備按照一定順序開啟或關(guān)閉的電子設(shè)備。它廣泛應(yīng)用于音響、舞臺燈光、電視廣播、工業(yè)自動化等領(lǐng)域。本文將介紹電源

![的頭像]() 發(fā)表于

發(fā)表于 07-08 14:16

?2397次閱讀

電源時序器是一種用于控制多個電源設(shè)備按照特定順序開啟或關(guān)閉的設(shè)備,廣泛應(yīng)用于音響、燈光、視頻等設(shè)備的控制中。然而,在使用過程中,

![的頭像]() 發(fā)表于

發(fā)表于 07-08 14:14

?2943次閱讀

電源時序器是一種用于控制多個電源設(shè)備按照特定順序開啟或關(guān)閉的設(shè)備。它廣泛應(yīng)用于音響、燈光、視頻等設(shè)備中,以確保設(shè)備在啟動和關(guān)閉過程中不會相互干擾,從而提高系統(tǒng)的穩(wěn)定性和可靠性。

![的頭像]() 發(fā)表于

發(fā)表于 07-08 14:11

?809次閱讀

之前上電,不過有些設(shè)計可能要求采用其他序列。正確的上電和關(guān)斷時序控制可以防止閂鎖引起的即刻損壞和

![的頭像]() 發(fā)表于

發(fā)表于 06-26 08:24

?1120次閱讀

你知道激光鉆孔技術(shù)有多牛嗎?看完這篇文章你就明白了

![的頭像]() 發(fā)表于

發(fā)表于 02-29 17:09

?997次閱讀

可能會開啟、鎖定或以不正確的模式開啟,因為這些器件試圖相互配合工作。面臨的更大挑戰(zhàn)是,上電時與時序和壓擺率相關(guān)的 IC 性能可能是溫度、相關(guān)電容器、機械應(yīng)力、老化和其他因素的函數(shù)。 當(dāng)

![的頭像]() 發(fā)表于

發(fā)表于 02-13 18:05

?1331次閱讀

多電源IC的上電時序控制你搞明白了么?

多電源IC的上電時序控制你搞明白了么?

評論