現(xiàn)在大型SoC設計中包含大量商業(yè)或自主開發(fā)的IP,且都基于復雜的行業(yè)標準接口協(xié)議。協(xié)議就好比一種語言,如果兩個人說的是同一種語言,就可以有效溝通。同樣,如果兩個硬件設備支持相同協(xié)議,它們就可以無縫通信。因此協(xié)議一致性已成為各芯片制造商的重點關注方向。 高級協(xié)議本身就已經(jīng)很復雜了,驗證這些協(xié)議的合規(guī)性也就更加復雜。新思科技擁有行業(yè)首創(chuàng)且不斷擴展的驗證IP(VIP)產(chǎn)品組合,再搭配VCS功能驗證解決方案和Verdi調(diào)試解決方案,可以幫助開發(fā)者高效實現(xiàn)硬件協(xié)議驗證。此外,新思科技還提供業(yè)界最廣泛的硬件輔助驗證產(chǎn)品組合,ZeBu硬件加速系統(tǒng)和HAPS FPGA原型系統(tǒng),來應對協(xié)議一致性和高級驗證的挑戰(zhàn)。 為什么高級協(xié)議驗證工作會這么難?開發(fā)者們所面臨的主要協(xié)議驗證挑戰(zhàn)都有哪些?他們又將如何應對復雜的高級協(xié)議驗證工作呢?

協(xié)議驗證有多難?

在典型的芯片設計中,數(shù)據(jù)流入芯片或其所在的系統(tǒng),或者在它們之間流動。必須正確布線、按照協(xié)議規(guī)范進行處理,并發(fā)送以進行進一步的分析、存儲或顯示。這套規(guī)則管理數(shù)據(jù)如何傳輸、使用什么命令以及如何確認傳輸?shù)耐ㄐ拧_@里我們稱之為協(xié)議。在概念上聽起來很簡單,但實現(xiàn)起來非常復雜。 行業(yè)中的不同協(xié)議太多了,而且其中大多數(shù)協(xié)議仍在迅速演變。設計團隊通常需要在所選標準完全獲批之前啟動設計周期并處理多個IP配置。 以PCIe為例,設計團隊要處理數(shù)千種彼此密切相關的配置,在這種情況下,需要設計并驗證所有數(shù)據(jù)路徑。除了各種互操作性測試外,對于新標準的了解不充分也是一個不小的挑戰(zhàn)。雖然設計團隊中可能有少數(shù)專家能夠運用現(xiàn)有技能來應對這些標準,但不是每個驗證團隊都具備相應的專業(yè)知識來及時驗證、調(diào)試和分析有缺陷的協(xié)議組件。 為了讓設計和驗證團隊有效構建符合嚴格協(xié)議規(guī)范的高性能SoC設計,必須及時提供端到端協(xié)議驗證解決方案,來支持各種驗證需求和每個標準規(guī)范的不同配置。

從簡單的接口IP

向子系統(tǒng)轉變

通常,大家都希望緊跟最新版本的標準,因此業(yè)內(nèi)最成功的協(xié)議是那些在升級同時保持向后兼容性的協(xié)議。例如USB標準,在過去二十年里已經(jīng)歷了數(shù)次演變,但每個新標準都能完美向后兼容。 而且現(xiàn)在很多協(xié)議已經(jīng)不僅僅是簡單的接口IP了,它們正在向子系統(tǒng)轉變。比如USB 4.0標準就是一個由USB、PCI和DisplayPort組成的子系統(tǒng),可以實現(xiàn)數(shù)據(jù)、視頻和多媒體文件的無縫傳輸和電力輸送。 向子系統(tǒng)架構的轉變大大增加了對所有IP模型進行詳盡的系統(tǒng)級驗證的復雜性。客戶根據(jù)4.0版本設計產(chǎn)品時,需確保接口仍能支持基于3.0、2.0和1.0版本的設計,并與其他兼容USB的設備進行互操作。 在需要大量數(shù)據(jù)的用例中,硬件加速成為確保設計和驗證團隊在存在完整軟件堆棧、設備驅動程序和更大的芯片生態(tài)系統(tǒng)的情況下驗證設計的關鍵推動力。

IP:半導體行業(yè)的樂高積木

開發(fā)高質(zhì)量的驗證IP和事務處理器需要多年的努力。及時了解最新的行業(yè)標準、精通協(xié)議、以及與經(jīng)驗豐富的團隊和IP設計團隊密切合作都必不可少。 越來越多負責制造高性能計算芯片的半導體公司不再自主開發(fā)協(xié)議IP,而是越發(fā)依賴商業(yè)IP和EDA公司提供的成熟IP。 導致這一市場變化的根本原因是什么呢? 雖然一些芯片公司擁有能夠自主實現(xiàn)IP集成的團隊,但他們同樣需要獲得盡可能多的幫助,對預先構建的IP模塊進行詳盡的設計和驗證。 新思科技等EDA公司不僅擁有數(shù)十年的專業(yè)知識和經(jīng)驗豐富的協(xié)議專家團隊,而且在為多個客戶和早期采用者部署各種協(xié)議兼容設計方面具經(jīng)驗十分豐富。是值得信賴的合作伙伴。通曉各個互連協(xié)議不一定能縮短驗證時間,但可以提高設計效率,并找出可能只有在最終消費者使用時才會發(fā)現(xiàn)的漏洞。

解決高級協(xié)議驗證難問題

有好的工具很重要

新思科技憑借行業(yè)首創(chuàng)、不斷擴展的驗證IP(VIP)產(chǎn)品組合,以及與標準組織和內(nèi)存供應商的密切合作,幫助設計和驗證開發(fā)者快速獲取并集成最新的互連技術,應對高速接口要求的所有驗證挑戰(zhàn)。 VIP可用于大多數(shù)基于不同接口的設計,包括PCIe、CXL、UCIe、DDR和USB,搭配新思科技的VCS功能驗證解決方案和Verdi調(diào)試解決方案,更好地實現(xiàn)硬件協(xié)議驗證。 此外,為進一步應對協(xié)議一致性和高級驗證日益嚴峻的挑戰(zhàn),新思科技還可提供業(yè)界最廣泛的硬件輔助驗證產(chǎn)品組合——ZeBu硬件加速系統(tǒng)和HAPS FPGA原型系統(tǒng):

-

適用于CXL 2.0、PCIe 5.0、USB3、UFS、SATA、以太網(wǎng)和NVMe的ZeBu虛擬主機和設備模型,支持使用真實操作系統(tǒng)、驅動程序和復雜SoC的應用軟件驗證主機到設備軟件堆棧。

-

ZeBu仿真加速技術,具有統(tǒng)一的測試平臺和設計編譯,以及專為速度優(yōu)化的協(xié)議事務處理器,仿真速度提高100倍,能夠實現(xiàn)更快的RTL回歸性能和環(huán)境搭建。

-

ZeBu速度適配器將新思科技ZeBu硬件加速系統(tǒng)連接到現(xiàn)實環(huán)境中,用于在線硬件加速(ICE)使用場景。基于可靠的新思科技IP,速度適配器支持PCIe、CXL 2.0、以太網(wǎng)、USB和SATA,與5G和網(wǎng)絡測試儀的連接以及特定客戶的硬件。

現(xiàn)在大型SoC設計將更多功能整合進芯片進行封裝,小芯片(Chiplet)使用芯片級IP整合重用技術,試圖將多個裸片(Die)通過內(nèi)部互聯(lián)技術集成在一個封裝內(nèi),對Die-to-Die標準的需求也不斷提高。新思科技高效的硬件驗證解決方案在推動互聯(lián)技術發(fā)展方面還將不斷拓展至更多的市場和應用中。

功能協(xié)議驗證已逐漸擴展到安全驗證的關鍵領域,這給集成了眾多軟硬件系統(tǒng)、IP協(xié)議、處理器的SOC系統(tǒng)驗證帶來了更高的復雜度。VIP會做更多細致的檢查,在驗證平臺植入VIP,可以加速驗證環(huán)境的搭建,幫助開發(fā)者有效規(guī)避風險,減少漏洞。

?

?

?

?

?

?

? ?

? ?

原文標題:擁有VIP,無懼芯片設計挑戰(zhàn)

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

-

新思科技

+關注

關注

5文章

797瀏覽量

50336

原文標題:擁有VIP,無懼芯片設計挑戰(zhàn)

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

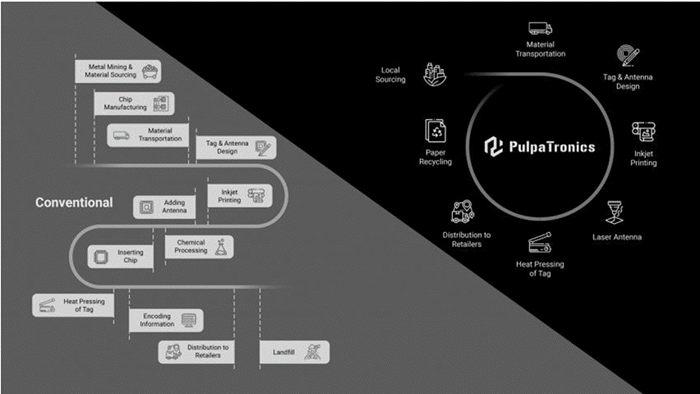

英國公司推出無芯片、無金屬的紙質(zhì)RFID標簽……

無懼戶外挑戰(zhàn),Amass XLB16系列連接器為太陽能路燈保駕護航!

SOC芯片設計的挑戰(zhàn)與解決方案

億鑄科技熊大鵬探討AI大算力芯片的挑戰(zhàn)與解決策略

當前主流的大模型對于底層推理芯片提出了哪些挑戰(zhàn)

深度解析 MS39233 無刷驅動芯片:技術的奧秘與應用前景

新思科技PCIe 7.0驗證IP(VIP)的特性

高危行業(yè)的安全守護者,頂堅防爆手機無懼挑戰(zhàn)

維信諾智能像素化ViP技術榮獲Best New Display Component獎

多核架構高性能電機控制芯片

芯片新戰(zhàn)場,EDA如何擁抱新挑戰(zhàn)?

MAX31790控制芯片無PWM輸出怎么解決?

維信諾ViP AMOLED產(chǎn)品特點

擁有VIP,無懼芯片設計挑戰(zhàn)

擁有VIP,無懼芯片設計挑戰(zhàn)

評論