電子發燒友網報道(文/程文智)三星電子今年7月25日在韓國京畿道華城園區V1生產線(EUV專用)為采用了新一代全環繞柵極(Gate All Around,簡稱GAA)晶體管制程節點的3nm芯片晶圓代工產品舉行了出廠儀式。才過4個月不到,韓國媒體Naver就爆出,三星3nm制程的良率非常低,不足20%。而且其5nm和4nm節點的良率問題也遲遲沒有得到改善。

其實,三星電子從2000年初就已經開始了對GAA晶體管結構的研究。自2017年開始,將其正式應用到3納米工藝,并于今年6月宣布啟動利用GAA技術的3納米工藝的量產。是全球首家將GAA晶體管結構用于晶圓制造的代工企業。據悉,我國的一家礦機芯片企業PanSemi(磐矽半導體)是三星電子的第一家客戶,目前也可能是其唯一的客戶。

據報道,三星電子為了解決良率問題,找到了美國的Silicon Frontline Technology,向這家企業尋求幫助。據說目前進展情況還不錯。

那么,三星電子在GAA上花的時間超過了20年,為何良率問題遲遲沒有得到解決呢?問題究竟出在了哪里?我們先從芯片的最基礎單元------晶體管結構的發展說起,然后看看有什么應對之策。

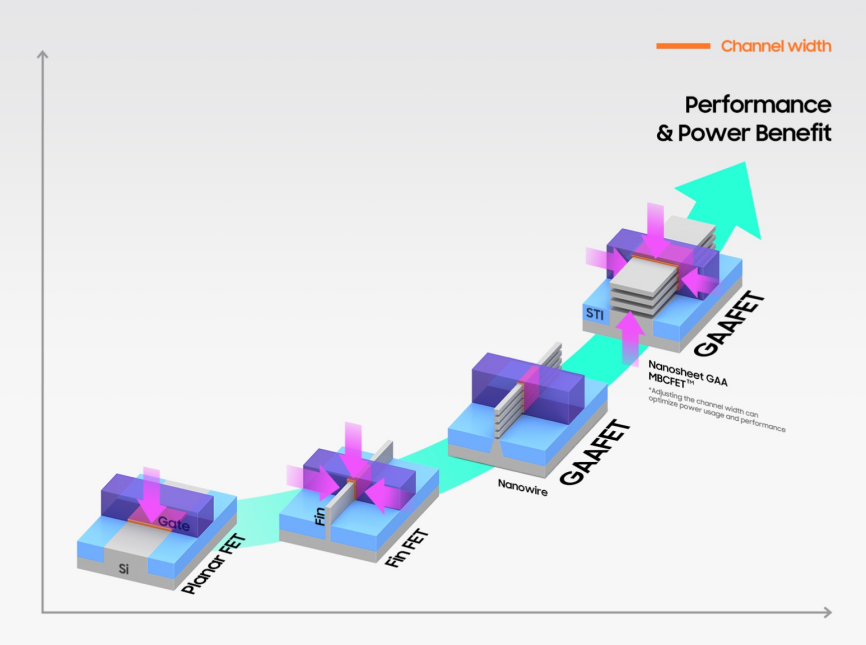

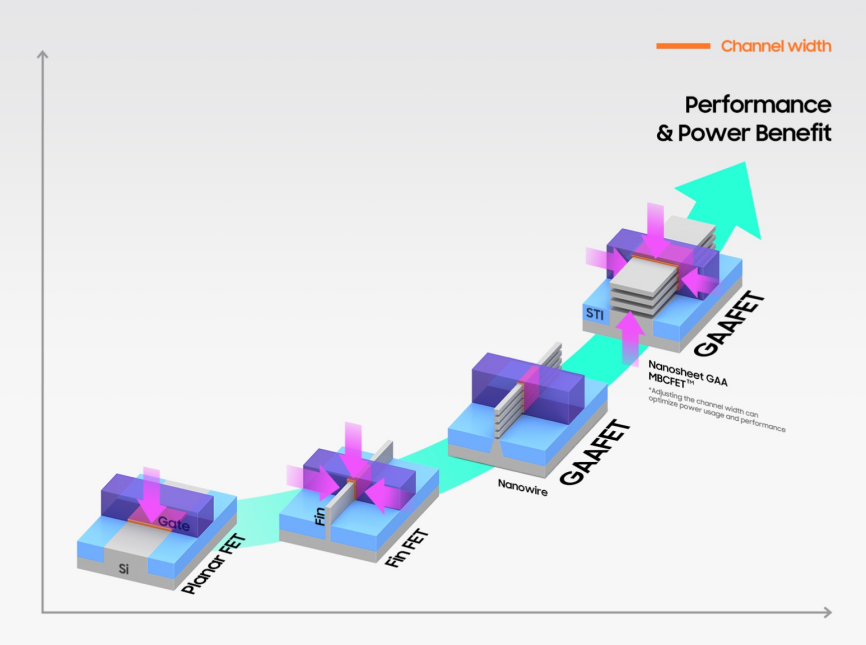

半導體芯片其實是眾多晶體管(Transistor)的集合,而晶體管其實就是一個小的開關。一個晶體管就代表了一個0或者1,也就是所謂的一個位元。在20nm以上的制程中,使用的晶體管被稱為金屬氧化物半導體場效應管(MOSFET:Metal Oxide Semiconductor FET);20nm~3nm,采用的是鰭式場效應晶體管(Fin FET:Fin Field Effected Transistor);3nm以下,采用的則是全環繞柵極場效應晶體管(GAAFET:Gate All Around Field Effect Transistor)。

為何會如此演進呢?主要是因為晶體管的工作原理,在晶體管內部,科學家定義了一個柵極長度(Gate Length)的概念,這是電子流通的方向,而其短邊就是所謂的制程。原理是在金屬柵極上加一個電壓來控制電子的導通和關閉。電子能夠導通過去就代表1,如果關斷則代表0。這個開關就是靠柵極施加電壓來造成電場來控制的,可電場的主要影響在接觸面上,如果柵極的長度越做越小,粉色的接觸面積就會越來越小,當小到一個程度,要關住電子的時候,就會關不住。鎖不住的電子就會偷偷溜過去。因此,先進制程中漏電流就會變大。解決這個問題的辦法就是增大柵極與電子通道的接觸面積,接觸面積越大,控制效果越好。所以到20nm以下就改用鰭式場效應晶體管,加電壓的時候就變成粉色這部分面積就增加了,所以效果會比較好。電場的作用比較強,可以鎖住電子不會漏電。到了3nm以下,實在太小了,接觸面積又不夠了,怎么辦呢?只好上下左右,統統把它包起來,用柵極把電子通道包起來,成為了GAAFET,這樣的控制效果會比較好。就目前來說,每一家晶圓代工廠大概都是用這樣的方式去制作。三星電子這次先于臺積電推出3nm制程,但情況并沒有好轉,良率不足20%,這成本就有點高了。加上此前就由于在4nm和5nm制程良率無法得到改善,而讓大客戶高通和英偉達等大客戶轉單臺積電了。此次要是還不能解決良率問題,可能大客戶就此失去了。為了能夠更好地解決良率問題,三星電子此次找上了美國廠商Silicon Frontline Technology,讓他們幫忙協助其提高3nm GAA結構的良率。根據Silicon Frontline Technology官網信息,該公司位于加利福尼亞州圣何塞,主要提供半導體設計和驗證解決方案。該公司為布局后驗證提供有保證的準確和有保證的快速電阻、電容、ESD 和熱分析,其產品已被70多家客戶使用,其中包括全球前25家半導體供應商中的12家,得到領先代工廠的認可和使用,并已用于500多種設計中。而且,客戶已經使用他們的技術解決了10nm、14nm、28nm、40nm、ADC、Serdes、敏感模擬電路、圖像傳感器、存儲器、定制數字設計和電源設備的問題。其主要的經驗在于為晶圓廠提供靜電放電(ESD)預防技術,而靜電放電是晶圓生產過程中產生缺陷的主要原因,據悉也是三星3nm GAA技術的良率過低的重要原因之一。Silicon Frontline Technology公司已經藉由水質和靜電放電(ESD)預防技術降低生產過程中的缺陷,以提高晶圓的生產良率。雖然三星號稱已經透過整合其合作伙伴使用的技術獲得了積極成果,但實際成果還需要在未來幾個月內持續觀察。據了解,目前市面上所做的失效分析中,90%以上的失效都是靜電放電所造成的。根據電測結果,失效模式包含開路、短路或漏電、參數漂移、功能失效等。根據失效原因,失效模式可以分為電力過應、靜電放電導致的失效、制造工藝不良導致的失效等。靜電放電是如何產生的呢?在芯片的制造過程中,半導體設備與芯片上的金屬層之間,在制造過程中可能會發生靜電放電。靜電放電失效可以歸結為兩種情形,一是靜電放電直接作用在了芯片上;二是靜電放電干擾了生產的設備正常運行,或者是干擾了外部電路環境。上圖就是所謂的充電誘導損傷(CID,Charging Induced Damage),就是當芯片在生產過程中,跟半導體設備接觸或者接近,可能產生充電誘導損傷,這個圖是晶圓表面被靜電打壞的照片,仔細放大看,就會發現,實際上就是里面的某一個晶體管被損傷了,如果用顯微鏡仔細看,就會發現這顆IC基本上被打壞了。上圖中左圖表示的是一個被靜電打壞的現象。從側面看,你會發現,多層金屬導線當發生靜電打壞的現象,這個地方就會有缺陷,這時候,這顆芯片就壞掉了。通過分析可以發現在晶圓的某些位置,特別容易發生靜電放電損壞芯片的現象。比入上圖右圖所示的紅點,就是實驗室中,科研人員測得的在某個條件下,某些位置容易打傷芯片。三星遇到的一直都是良率的問題,所以這次,他們想通過Silicon Frontline Technology提供的靜電放電模擬軟件協助其找到原因,進而解決良率的問題。如果此次他們能夠成功解決良率問題,那么在未來的先進制程競爭中超越臺積電。畢竟臺積電目前的3nm制程采用的仍然是FinFET技術,到2025年2nm時,他們才會采用GAAFET技術。而三星此次如果解決了良率問題,那么在2nm競爭時,將會比臺積電多出3年的實踐經驗。因此,兩家公司的決戰點應該會在2025年之后。

聲明:本文由電子發燒友原創,轉載請注明以上來源。如需入群交流,請添加微信elecfans999,投稿爆料采訪需求,請發郵箱huangjingjing@elecfans.com。- 最高漲幅25%,AMD宣布上調Xilinx FPGA售價,供應短缺讓TOP 2廠商受益

- 時隔20年,莫斯科人汽車再次復產,背后全是中國車企的影子

- 歐盟超430億歐元投向芯片領域,對上游半導體設備有何影響?

- 24W以下電源,新型自供電BJT方案將全面取代其他方案?

- 車用芯片不再缺?芯片大廠表示有所緩解,真實情況究竟如何呢?

原文標題:芯片制程到3nm后如何突破良率難題?

文章出處:【微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:芯片制程到3nm后如何突破良率難題?

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

相關推薦

電子發燒友網報道(文/李彎彎)近日消息,聯發科、高通新一波5G手機旗艦芯片將于第四季推出,兩大廠新芯片都以臺積電3nm制程生產,近期進入投片階段。 ? 在臺積電

![的頭像]() 發表于

發表于 07-09 00:19

?5231次閱讀

,導致Exynos 2500良率不佳的原因是,這顆SoC基于三星第二代3nm GAA制程工藝——SF3工藝,然而目前第二代SF

![的頭像]() 發表于

發表于 06-25 00:04

?3649次閱讀

)計劃從2025年1月起對3nm、5nm先進制程和CoWoS封裝工藝進行價格調整。 先進制程2025年喊漲,最高漲幅20% 其中,對3nm、

![的頭像]() 發表于

發表于 01-03 10:35

?56次閱讀

臺積電近期成為了高性能芯片代工領域的明星企業,其產能被各大科技巨頭瘋搶。據最新消息,臺積電的3nm和5nm工藝產能利用率均達到了極高水平,其中3nm將達到100%,而5

![的頭像]() 發表于

發表于 11-14 14:20

?369次閱讀

聯發科正式宣告,將于10月9日盛大揭幕其新一代MediaTek天璣旗艦芯片發布會,屆時將震撼推出天璣9400移動平臺。這款芯片不僅是聯發科迄今為止最為強大的手機處理器,更標志著安卓陣營正式邁入3nm工藝時代,成為業界首顆采用臺積

![的頭像]() 發表于

發表于 09-24 15:15

?616次閱讀

臺積電近期迎來3nm制程技術的出貨高潮,預示著其在半導體制造領域的領先地位進一步鞏固。隨著蘋果iPhone 16系列新機發布,預計搭載的A18系列處理器將采用臺積電3nm工藝,這一消息直接推動了臺積電

![的頭像]() 發表于

發表于 09-10 16:56

?671次閱讀

據業內手機晶片領域的資深人士透露,臺積電計劃在明年1月1日起對旗下的先進工藝制程進行價格調整,特別是針對3nm和5nm工藝制程,而其他工藝制程

![的頭像]() 發表于

發表于 07-04 09:22

?708次閱讀

近期,三星電子在半導體制造領域遭遇挑戰,其最新的Exynos 2500芯片在3nm工藝上的生產良率持續低迷,目前仍低于20%,遠低于行業通常要求的60%量產標準。這一情況引發了業界對三

![的頭像]() 發表于

發表于 06-24 18:22

?1535次閱讀

近日,全球芯片代工領域掀起了不小的波瀾。據媒體報道,臺積電在3nm制程的芯片代工價格上調5%之后,依然收獲了供不應求的訂單局面。而與此同時,韓國的三星電子在

![的頭像]() 發表于

發表于 06-22 14:23

?1177次閱讀

據外媒最新報道,全球知名的處理器大廠英特爾在周三宣布了一個重要的里程碑:其先進的3nm級制程工藝技術“Intel 3”已在兩個工廠正式投入大批量生產。這一技術的突破,無疑將為英特爾在超

![的頭像]() 發表于

發表于 06-21 09:31

?545次閱讀

在近日于比利時微電子研究中心(imec)舉辦的2024年全球技術論壇(ITF World 2024)上,AMD首席執行官蘇姿豐透露了公司的最新技術動向。她表示,AMD將采用先進的3nm GAA(Gate-All-Around)制程技術來量產其下一代

![的頭像]() 發表于

發表于 05-31 09:53

?653次閱讀

李時榮聲稱,“客戶對代工企業的產品競爭力與穩定供應有嚴格要求,而4nm工藝已步入成熟良率階段。我們正積極籌備后半年第二代3nm工藝及明年2nm

![的頭像]() 發表于

發表于 03-21 15:51

?651次閱讀

據韓國媒體報道稱,三星電子旗下的3納米工藝良品比例仍是一個問題。報道中僅提及了“3nm”這一籠統概念,并沒有明確指出具體的工藝類型。知情者透露,盡管有部分分析師認為其已經超過60%

![的頭像]() 發表于

發表于 03-07 15:59

?789次閱讀

來源:EETOP,謝謝 編輯:感知芯視界 Link 近期韓媒DealSite+報道,表示三星的3nm GAA生產工藝存在問題,在嘗試生產適用于Galaxy S25 /S25+手機的Exynos

![的頭像]() 發表于

發表于 02-04 09:31

?811次閱讀

3nm制程行業資訊

北京中科同志科技股份有限公司

發布于 :2024年02月01日 09:29:15

芯片制程到3nm后如何突破良率難題?

芯片制程到3nm后如何突破良率難題?

評論