作者:Jingjing Sun, Ling Jiang, and Henry Zhang

介紹

對于電源轉換器,具有最小寄生參數的熱回路PCB布局可以提高電源效率,降低電壓振鈴,并減少電磁干擾(EMI)。本文討論如何通過最小化PCB等效串聯電阻(ESR)和等效串聯電感(ESL)來優化熱回路布局設計。本文研究并比較了影響因素,包括去耦電容位置、功率FET尺寸和位置以及過孔布局。通過實驗驗證了分析的有效性,總結了最小化PCB ESR和ESL的有效方法。

熱回路和PCB布局寄生參數

開關模式功率轉換器的熱回路定義為由HF電容和相鄰功率FET形成的關鍵高頻(HF)交流電流環路。它是功率級PCB布局中最關鍵的部分,因為它包含高dv/dt和di/dt噪聲成分。設計不佳的熱回路布局會受到高水平的PCB寄生參數的影響,包括ESL、ESR和等效并聯電容(EPC),這些參數對功率轉換器的效率、開關性能和EMI性能有重大影響。

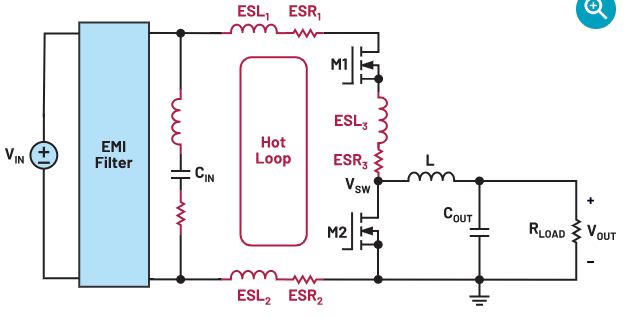

圖1所示為同步降壓DC-DC轉換器原理圖。熱回路由MOSFET M1和M2以及去耦電容C形成在.M1 和 M2 的開關動作會產生高頻 di/dt 和 dv/dt 噪聲。C在提供低阻抗路徑以旁路HF噪聲成分。然而,寄生阻抗(ESR,ESL)存在于元件封裝內和熱回路PCB走線中。通過ESL的高di/dt噪聲會導致HF振鈴,進而產生EMI。存儲在ESL中的能量在ESR上耗散,導致額外的功率損耗。因此,應盡量減少熱回路PCB的ESR和ESL,以減少HF振鈴并提高效率。

準確提取熱回路ESR和ESL有助于預測開關性能并改進熱回路設計。元件的封裝和PCB走線都會影響總環路寄生參數。這項工作主要集中在PCB布局設計上.用戶可以使用一些工具來提取PCB寄生參數,例如Ansys Q3D,FastHenry/FastCap,StarRC等。Ansys Q3D等商用工具可提供精確的仿真,但通常價格昂貴。FastHenry/FastCap是一款基于部分單元等效電路(PEEC)數值建模的免費工具1并且可以通過編程提供靈活的仿真,以探索不同的布局設計,盡管需要額外的編碼。FastHenry/FastCap中寄生參數提取的有效性和準確性已經過驗證,并與Ansys Q3D進行了比較,結果一致。2,3在本文中,FastHenry 被用作提取 PCB ESR 和 ESL 的經濟高效的工具。

圖1.具有熱回路 ESR 和 ESL 的降壓轉換器。

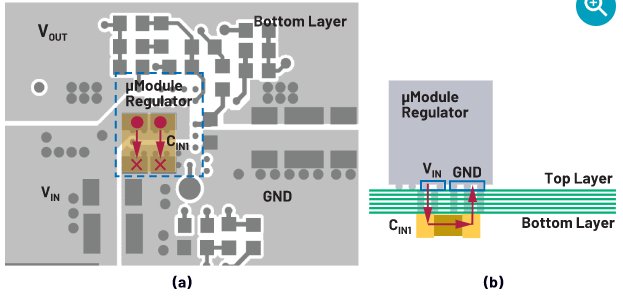

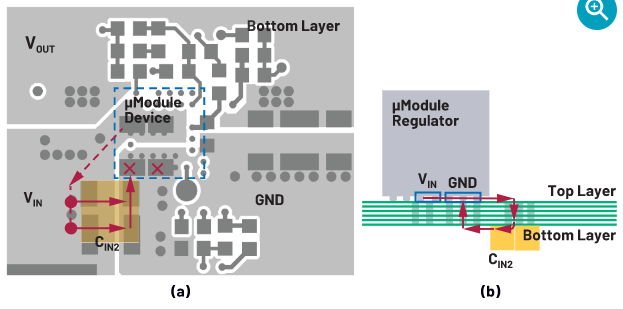

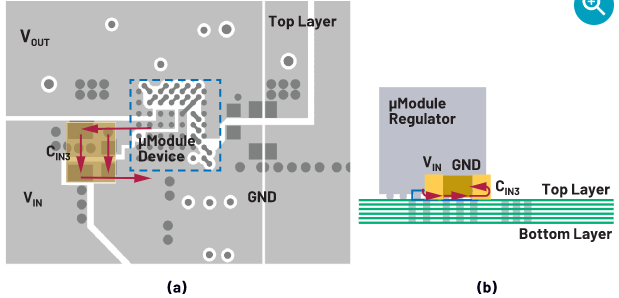

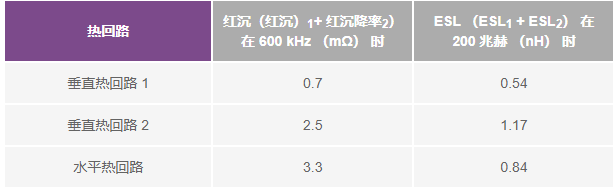

熱回路 PCB ESR 和 ESL 與去耦電容器位置的關系

在本節中,C 的影響在基于ADI公司的LTM4638μModule穩壓器演示板DC2665A-B對位置進行了研究。LTM4638 是一款集成式 20 V?在、15 A 降壓型降壓轉換器模塊,采用微型 6.25 mm × 6.25 mm × 5.02 mm BGA 封裝。它具有高功率密度、快速瞬態響應和高效率。該模塊集成了一個小型HF陶瓷C在內部,雖然還不夠,但受模塊封裝尺寸的限制。圖 2 至 4 顯示了演示板上的三種不同熱回路以及額外的外部 C在.第一個是垂直熱回路 1(圖 2),其中 C合1放置在μModule穩壓器正下方的底層。The μModule V在和接地 BGA 引腳連接到 C合1直接通過過孔。這些連接提供了演示板上最短的熱回路路徑。第二個熱回路是垂直熱回路 2(圖 3),其中 CHNS仍放置在底層,但移至μModule穩壓器的側面區域。因此,在熱回路中增加了一條額外的PCB走線,與垂直熱回路1相比,預計ESL和ESR更大。第三個熱回路選項是水平熱回路(圖 4),其中 CHNR放置在靠近μModule穩壓器的頂層。The μModule V在和 GND 引腳連接到 CHNR通過頂層銅而不通過過孔。盡管如此,V在頂層的銅寬受另一個引腳排列的限制,導致與垂直熱回路1相比,環路阻抗增加。表1比較了FastHenry提取的PCB ESR和熱回路的ESL。正如預期的那樣,垂直熱回路 1 具有最低的 PCB ESR 和 ESL。

圖2.垂直熱回路 1:(a) 頂視圖和 (b) 側視圖。

圖3.垂直熱回路 2:(a) 頂視圖和 (b) 側視圖。

圖4.水平熱回路:(a) 頂視圖和 (b) 側視圖。

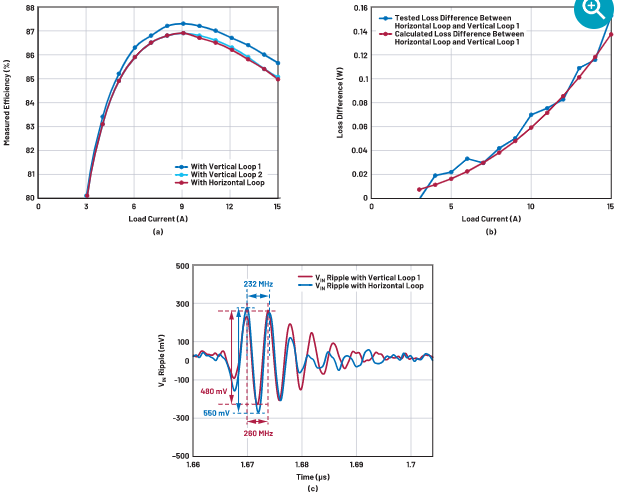

為了實驗驗證不同熱回路中的ESR和ESL,演示板效率和V在測試12 V至1 V CCM操作下的交流紋波。從理論上講,較低的ESR導致更高的效率,而較小的ESL導致更高的V西 南部振鈴頻率和較低的V在漣漪幅度。圖5a顯示了測得的效率。垂直熱回路 1 提供與最低 ESR 相對應的最高效率。水平熱回路和垂直熱回路1之間的損耗差也是基于提取的ESR計算的,這與圖5b所示的測試結果一致。五世在圖5c中的HF紋波波形是跨C測試的在.水平熱回路具有更高的V在紋波幅度和較低的振鈴頻率,從而驗證了與垂直熱回路 1 相比更高的環路 ESL。此外,由于環路ESR較高,V在水平熱回路中的波紋比垂直熱回路 1 中的波紋衰減得更快。此外,較低的V在紋波可降低 EMI,并允許更小的 EMI 濾波器尺寸。

圖5.演示板測試結果:(a) 效率,(b) 水平環路和垂直環路 1 之間的損耗差異,以及 (c) V在M1 導通期間紋波,輸出電流為 15 A。

| 4% |

熱回路 PCB ESR 和 ESL 與 MOSFET 的尺寸和位置

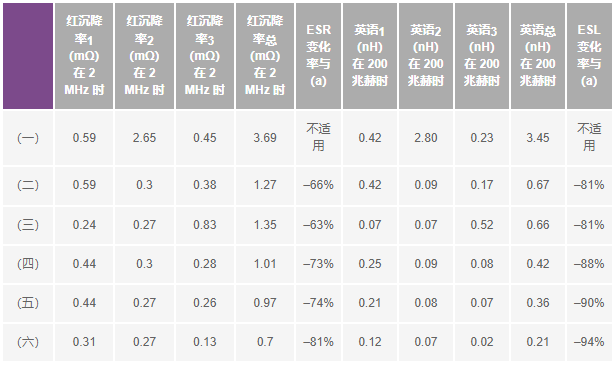

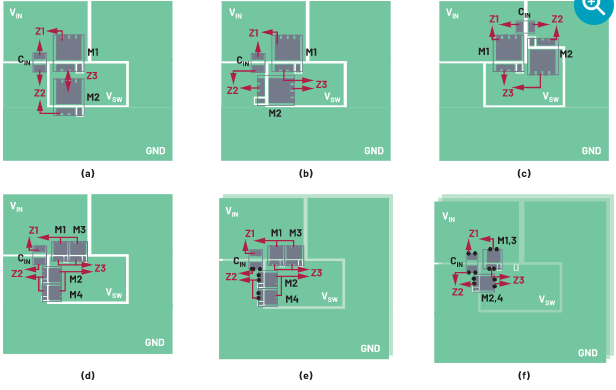

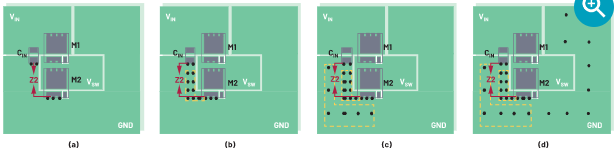

對于分立式設計,功率FET的布局和封裝尺寸也會對熱回路ESR和ESL產生重大影響。典型的半橋熱回路,功率FET M1和M2以及去耦電容C在在本節中建模和調查。如圖6所示,比較了常用的功率FET封裝尺寸和放置位置。表 2 顯示了每種情況下提取的 ESR 和 ESL。

案例(a)至(c)展示了三種流行的功率FET布局,分別采用5 mm×6 mm MOSFET。熱回路的物理長度決定了寄生阻抗。因此,案例 (b) 中的 90° 形狀放置和案例 (c) 中的 180° 形狀設備放置都會導致 ESR 降低 60% 和 ESL 降低 80%,因為與案例 (a) 中的環路路徑相比更短。由于 90° 形狀放置顯示出好處,因此根據案例 (b) 研究了更多案例,以進一步降低環路 ESR 和 ESL。在情況(d)中,5 mm × 6 mm MOSFET被兩個并聯的3.3 mm ×3.3 mm MOSFET取代。由于 MOSFET 占位面積更小,環路長度進一步縮短,從而將環路阻抗降低了 7%。在案例(e)中,當在熱回路層下放置接地層時,與案例(d)相比,熱回路ESR和ESL進一步降低了2%。原因是在接地層產生渦流,從而感應出相反的磁場并等效地降低環路阻抗。在情況(f)中,另一個熱回路層被構造為底層。如果將兩個并聯的MOSFET對稱放置在頂層和底層并通過過孔連接,則由于并聯阻抗,熱回路PCB ESR和ESL降低更為明顯。因此,在頂層和底層具有對稱 90° 形狀或 180° 形狀放置的較小尺寸器件可實現最低的 PCB ESR 和 ESL。

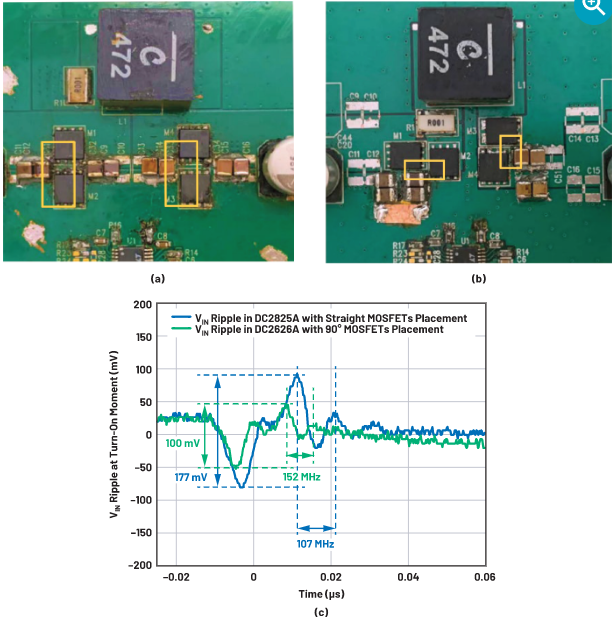

為了通過實驗驗證MOSFET布局的影響,使用了ADI公司的高效率、4開關同步降壓-升壓控制器演示板LT8390/DC2825A和LT8392/DC2626A.4如圖7a和圖7b所示,DC2825A具有直MOSFET布局,DC2626A具有90°形狀MOSFET布局。為了進行公平比較,兩款演示板配置了相同的MOSFET和去耦電容,并在36 V至12 V/10 A、300 kHz降壓操作下進行了測試。圖 7c 顯示了測試的 V在M1導通時刻的交流紋波。通過 90° 形狀的 MOSFET 放置,V在紋波具有較低的幅度和較高的諧振頻率,因此由于熱回路路徑較短,驗證了較小的PCB ESL。相反,由于更長的熱回路和更高的ESL,直MOSFET的放置導致更高的V在紋波幅度和較慢的諧振頻率。根據Cho和Szokusha研究中的EMI測試結果,較高的輸入電壓紋波也會導致更嚴重的EMI發射。4

圖6.熱回路多氯聯苯型號:(a) 5 mm × 6 mm MOSFET,直線放置;(b) 5毫米×6毫米MOSFET,呈90°形狀放置;(c) 180°形狀放置的5毫米×6毫米MOSFET;(d) 兩個平行的3.3毫米×3.3毫米MOSFET,呈90°形狀放置;(e) 兩個平行的3.3毫米×3.3毫米MOSFET,與接地層呈90°形狀放置;(f) 在頂層和底層以 90° 形狀放置對稱的 3.3 毫米× 3.3 毫米 MOSFET。

圖7.(a) LT8390/DC2825A 熱回路,具有直 MOSFET 放置;(b) LT8392/DC2626A 熱回路,放置 90° MOSFET;(c) 五在M1導通時的紋波波形。

圖8.熱回路 PCB 型號,(a) 五個 GND 過孔靠近 C在和 M2;(b) 14 個 GND 過孔放置在 C 之間在和 M2;(c) 根據(b)在GND上再放置6個過孔;(d) 根據 (c) 在 GND 區域再放置 9 個過孔。

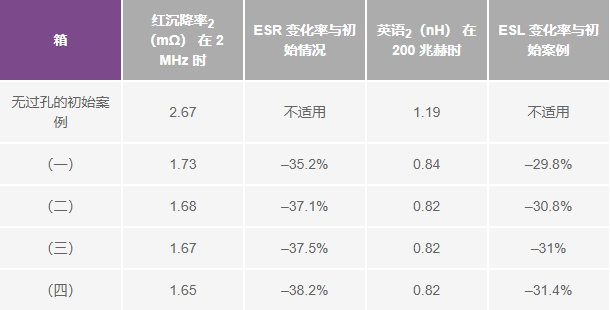

熱回路 PCB ESR 和 ESL 與通孔貼裝

熱回路中的過孔位置對環路ESR和ESL也有關鍵影響。如圖8所示,對具有兩層PCB結構和直功率FET放置的熱回路進行了建模。FET放置在頂層,第二層是接地層。寄生阻抗Z2在C之間在GND焊盤和M2源焊盤是熱回路的一部分,并作為示例進行研究。Z2 提取自 FastHenry。表3總結并比較了模擬的ESR2和 ESL2具有不同的過孔位置。

通常,增加更多過孔會降低PCB寄生阻抗。然而,ESR的降低2和 ESL2與過孔數量不成線性比例。靠近端子焊盤的通孔可最明顯地降低 PCB ESR 和 ESL。因此,對于熱回路布局設計,必須將幾個關鍵過孔放置在靠近C焊盤的位置在和 MOSFET,以最大限度地降低 HF 環路阻抗。

結論

降低熱回路的寄生參數有助于提高電源效率、降低電壓振鈴并降低EMI。為了最小化PCB寄生參數,研究并比較了具有不同去耦電容位置、MOSFET尺寸和位置以及通孔布局的熱回路布局設計。較短的熱回路路徑、更小尺寸的 MOSFET、對稱的 90° 形狀和 180° 形狀 MOSFET 布局以及靠近關鍵元件的通孔有助于實現最低的熱回路 PCB ESR 和 ESL。

審核編輯:郭婷

-

電源

+關注

關注

185文章

18423瀏覽量

257330 -

轉換器

+關注

關注

27文章

9141瀏覽量

152532 -

PCB

+關注

關注

1文章

2129瀏覽量

13204

發布評論請先 登錄

評論