我們生活在一個(gè)模擬世界中,盡管數(shù)字技術(shù)占主導(dǎo)地位。在域之間移動會導(dǎo)致量化錯(cuò)誤;這是不可避免的。工程師的工作是使這種過渡盡可能無縫,這就是ADC和DAC的用武之地。

模數(shù)轉(zhuǎn)換(ADC)可以采取多種形式,并有許多折衷方案。從根本上說,關(guān)鍵品質(zhì)因數(shù)是準(zhǔn)確性和速度。更復(fù)雜的是,這兩個(gè)參數(shù)通常是相反的;更高的精度需要更多的位,但添加更多的位會降低采樣率。更快的轉(zhuǎn)換通常以有效位數(shù)為代價(jià)。從廣義上講,選擇由Δ-Σ轉(zhuǎn)換拓?fù)洌ǜ叻直媛剩L延遲)或閃存轉(zhuǎn)換器(高速,但以功耗和面積為代價(jià))結(jié)束。介于這兩個(gè)極端之間的是逐次逼近寄存器或SAR轉(zhuǎn)換器。這種“金發(fā)姑娘”技術(shù)在分辨率和速度之間提供了很好的折衷,但它也有其局限性。

一般來說,SAR轉(zhuǎn)換器一直是無線通信中使用的模擬前端(AFE)的不錯(cuò)選擇,這要?dú)w功于它們兼具精度和速度。隨著物聯(lián)網(wǎng)的覆蓋范圍從核心進(jìn)一步延伸,將邊緣永遠(yuǎn)向外推,對AFE的需求不斷增長,AFE能夠以更高的頻率(因此更高的采樣率)處理更復(fù)雜的協(xié)議,但功耗更低。我們不要稱其為問題,而是將其稱為機(jī)會,以找到一種技術(shù),可以在無線連接需要安裝到足夠小的東西中佩戴在耳朵中的時(shí)代實(shí)現(xiàn)更小,更快,更低功耗的AFE,并且可能由從其操作環(huán)境中收集的能量供電。

特區(qū)的一些背景

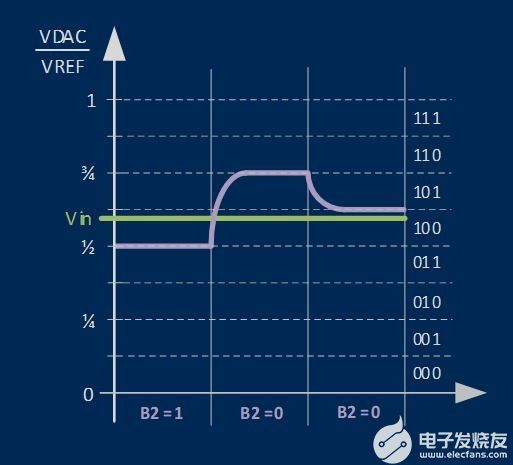

顧名思義,SAR的工作原理是連續(xù)近似模擬輸入的值,反復(fù)將輸入電壓與反復(fù)減半的基準(zhǔn)電壓進(jìn)行比較,直到基準(zhǔn)電壓源和源極之間的差異無法區(qū)分或滿足設(shè)計(jì)要求。每次比較都會生成一個(gè)“更高”或“更低”的結(jié)果,該結(jié)果在數(shù)字輸出中形成一個(gè)位,從最高有效位開始。這種情況一直持續(xù)到轉(zhuǎn)換器以足夠的精度產(chǎn)生足夠的位來表示模擬輸入。

圖 1:3 位 SAR ADC 示例

由于所有步驟都需要在采樣周期內(nèi)完成,因此可能的位數(shù)將主要取決于電路中需要更改的元件的響應(yīng)時(shí)間。這包括用于與輸入電壓進(jìn)行比較的基準(zhǔn)電壓(通常存儲在由開關(guān)和電容器組成的采樣保持電路中)。反過來,該基準(zhǔn)電壓(通常)由數(shù)模轉(zhuǎn)換器或DAC產(chǎn)生。因此,SAR轉(zhuǎn)換器的采樣速率將在一定程度上由用于產(chǎn)生基準(zhǔn)電壓和控制邏輯的DAC決定,但通常SAR性能實(shí)際上受到比較器速度的限制。輸入端的開關(guān)電容(實(shí)際上是一個(gè)低通濾波器)引入了一個(gè)較高的頻率閾值,但由于開關(guān)的電阻較低,電容很小,這意味著轉(zhuǎn)換器通常可以處理數(shù)百M(fèi)Hz或更高的信號;特區(qū)的另一個(gè)積極特征。

就整體精度而言,而不僅僅是分辨率,重要的是DAC產(chǎn)生的基準(zhǔn)電壓(而不是比較器的DAC產(chǎn)生的電壓)也盡可能準(zhǔn)確,因?yàn)樗衅渌麥y量值都與此相關(guān)。盡可能多地集成整體解決方案的SAR,包括開關(guān)電容S&H和DAC參考電壓發(fā)生器,將提供最佳性能。

克服SAR轉(zhuǎn)換器的局限性

流水線ADC具有多個(gè)級,每個(gè)級處理轉(zhuǎn)換過程的一部分。隨著每個(gè)階段完成其操作,它可以自由地接受下一個(gè)樣品。流水線ADC提供的主要優(yōu)勢之一是其速度;一旦管道完全啟動,它就可以在新樣本“推送”數(shù)據(jù)時(shí)生成新的輸出。SAR 的架構(gòu)通常基于多次使用的單級,而流水線轉(zhuǎn)換器使用并行性來加快速度。

將SAR和流水線方法相結(jié)合,可以產(chǎn)生所謂的SAR輔助流水線ADC。Adesto的工程師已經(jīng)實(shí)施了這種方法,以創(chuàng)建一個(gè)ADC,該ADC可以在高帶寬下以最大的速度和精度運(yùn)行,但需要最小的功率和面積。

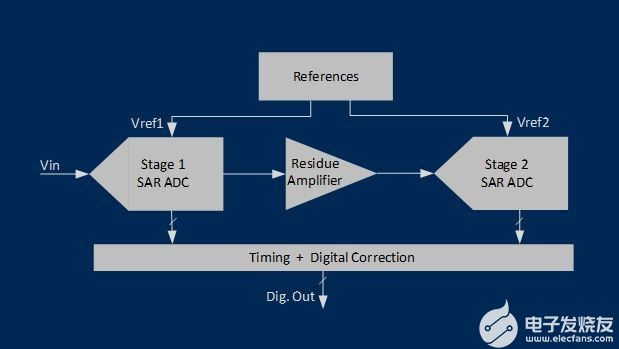

阿德斯托開發(fā)的轉(zhuǎn)換器使用兩個(gè)SAR級;第一級處理輸出的最高有效位,而第二級處理最低有效位。通過添加數(shù)字模塊來處理時(shí)序和校正(見圖2),SAR輔助流水線轉(zhuǎn)換器生成結(jié)果的時(shí)間不到同類SAR轉(zhuǎn)換器的一半,而不會受到傳統(tǒng)流水線ADC相關(guān)的損失(包括物理尺寸和功耗)。

圖 2:SAR 輔助流水線 ADC 架構(gòu)

簡單來說,一旦第一個(gè)SAR階段完成轉(zhuǎn)換,它就可以接受新樣本,而第二個(gè)SAR階段完成第一個(gè)樣品的轉(zhuǎn)換。兩級之間的放大器增益放寬了對第二個(gè)SAR的要求,從而形成了比SAR本身更節(jié)能的解決方案。

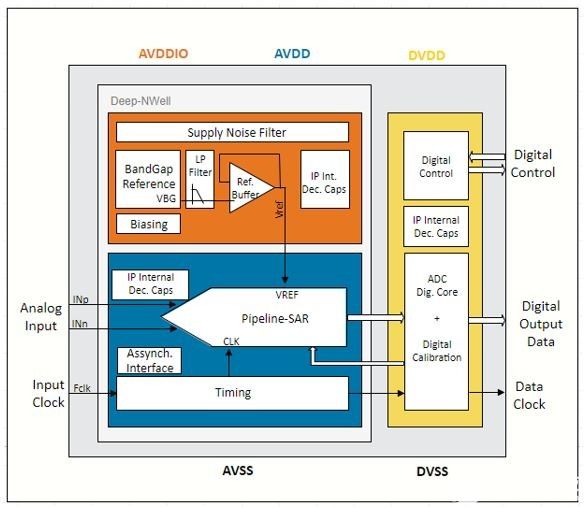

圖3顯示了Adesto的SAR輔助管道ADC的框圖。

圖 3:Adesto 的單通道 SAR 輔助流水線 ADC

如圖3所示,Adesto開發(fā)的IP集成了所有關(guān)鍵功能,包括基準(zhǔn)電壓發(fā)生器、定時(shí)和控制邏輯、數(shù)字校準(zhǔn)以及去耦電容。對所有模擬模塊使用深n阱技術(shù)可提供對基板噪聲的抗擾度,當(dāng)IP被許可供客戶在可能沒有專用模擬電源的設(shè)計(jì)中使用時(shí),這一點(diǎn)尤其重要。該設(shè)計(jì)非常全面,因?yàn)樗恍枰獠炕鶞?zhǔn)電壓源或穩(wěn)壓器。

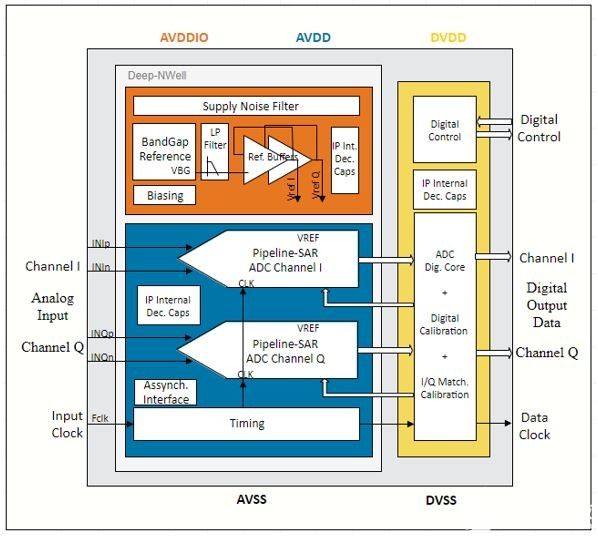

相同的內(nèi)核 IP 已用于開發(fā)針對正交 I/Q 調(diào)制架構(gòu)的雙通道解決方案(圖 4)。可以看出,某些功能可以在兩個(gè)通道之間共享,同時(shí)包括單獨(dú)的基準(zhǔn)電壓緩沖器和時(shí)鐘樹,以最大程度地減少通道之間的串?dāng)_。

圖 4:Adesto 的雙通道 SAR 輔助流水線 ADC

這種方法提供的主要優(yōu)點(diǎn)之一是其低功耗操作。Adesto部署在現(xiàn)已上市的批量IP中,包括采用28nm工藝的雙通道解決方案,每個(gè)通道提供160M樣本/秒,總功耗僅為18mW。該ADC的總芯片面積僅為0.055mm2,因此具有極高的面積效率。盡管集成度如此之高,但它可以提供63.1dB的SNDR,通道之間的串?dāng)_低于-80.0dB。

同一轉(zhuǎn)換器的八通道版本可以同時(shí)處理四個(gè)I/Q通道,工作速率為122.88Msamples/s,功耗僅為45mW。它的有效位數(shù)(ENOB)為10.2位,但仍然只需要0.3mm2的芯片面積。Adesto還可以提供12位SAR輔助流水線ADC,在僅0.05mm2的芯片面積內(nèi)實(shí)現(xiàn)200M采樣/秒的采樣速率,耗散10mW。

AFE在很大程度上依賴于ADC的性能,而不起眼的SAR是工程師可用的最可靠和最通用的架構(gòu)之一。這只是Adesto提供的IP的一個(gè)例子,該IP已經(jīng)過優(yōu)化,可滿足最新應(yīng)用的需求。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8741瀏覽量

147715 -

adc

+關(guān)注

關(guān)注

99文章

6531瀏覽量

545407 -

物聯(lián)網(wǎng)

+關(guān)注

關(guān)注

2912文章

44889瀏覽量

375755

發(fā)布評論請先 登錄

相關(guān)推薦

不同時(shí)期的硬件工程師,最怕發(fā)生的事 #電子工程師 #硬件工程師 #內(nèi)容過于真實(shí) #YXC晶振 #揚(yáng)興科技

當(dāng)硬件工程師穿越到霸總劇: 以他性格肯定忍不到第二集? #硬件工程師 #電路設(shè)計(jì) #晶振 #揚(yáng)興科技

當(dāng)你的工程師朋友失聯(lián)時(shí),別氣,ta真的是在忙工作 #搞笑 #電子愛好者 #硬件工程師 #晶振 #揚(yáng)興科技

硬件工程師VS軟件工程師|硬件工程師看到這都淚目了!#硬件設(shè)計(jì) #硬件工程師 #電子工程師 #軟件工程師

FPGA算法工程師、邏輯工程師、原型驗(yàn)證工程師有什么區(qū)別?

干硬件這一行,各種辛酸只有同行才懂吧 ? #電路設(shè)計(jì) #電子愛好者 #硬件工程師 #電子工程師

嵌入式軟件工程師和硬件工程師的區(qū)別?

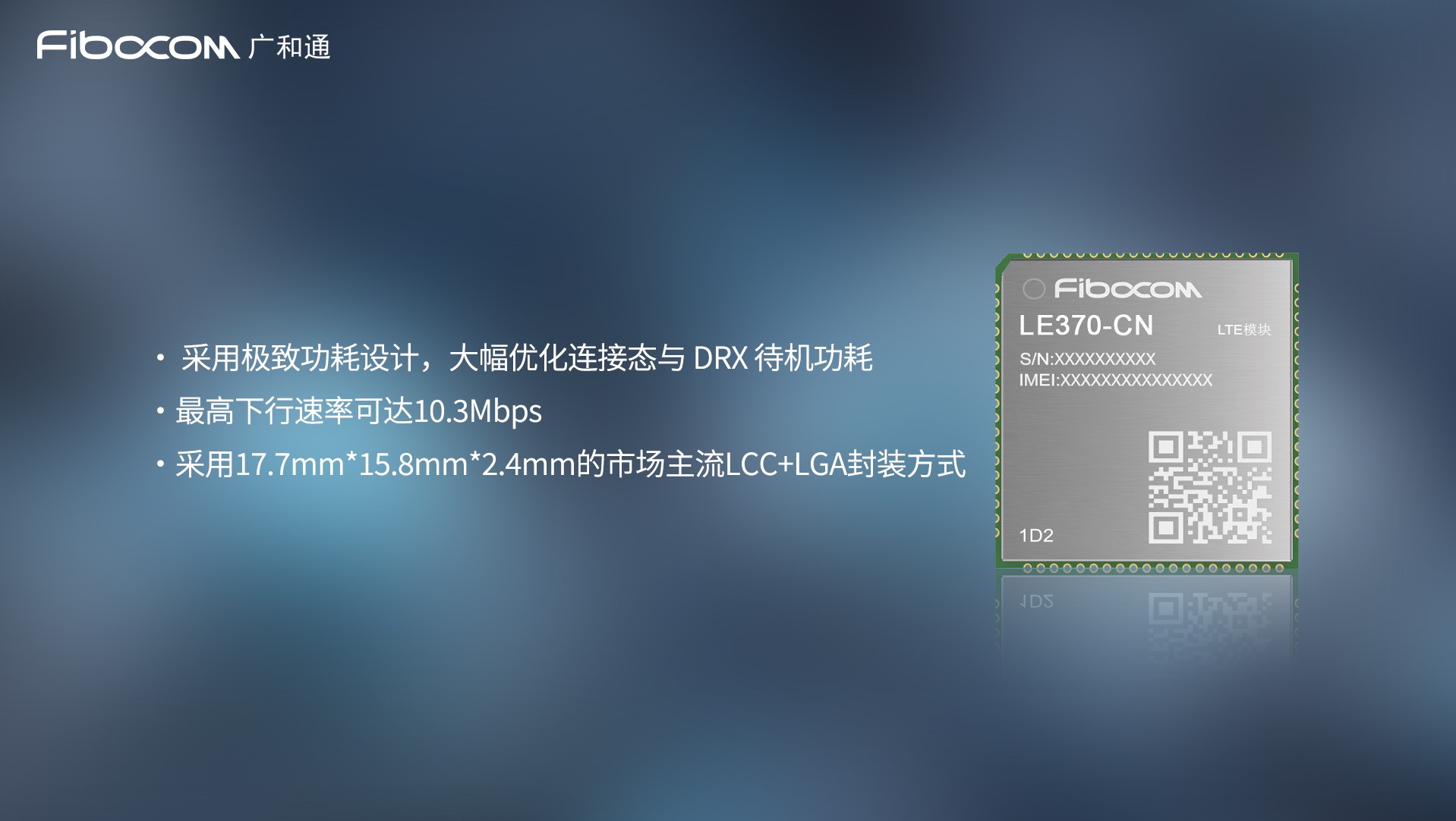

更低功耗、更低價(jià)格!廣和通Cat.1 bis模組LE370-CN規(guī)模量產(chǎn)

更低功耗、更低價(jià)格!廣和通Cat.1 bis模組LE370-CN規(guī)模量產(chǎn)

“班長!說好畢業(yè)后當(dāng)硬件工程師,你怎么..." #搞笑 #電子行業(yè) #電子工程師 #晶振 #揚(yáng)興科技

工程師對以更低功耗實(shí)現(xiàn)更快采樣的回答

工程師對以更低功耗實(shí)現(xiàn)更快采樣的回答

評論