什么是當今吸引人們注意的流行先進技術?相信以下的專業(yè)用詞都經(jīng)常出現(xiàn)在周遭與新聞、文章之中,如人工智能(Artificial Intelligence)、深度學習(Deep Learning)、云端計算(Cloud Computing)、超級計算機(Supercomputer)、自動駕駛、智能語音識別等。

包括Google、Amazon、Intel、Nvidia或是AMD等,從這些世界級技術巨型企業(yè)的策略中可以發(fā)現(xiàn),不約而同的都正積極投下巨額資金,來開發(fā)前述的這些軟硬件技術和相關的應用。

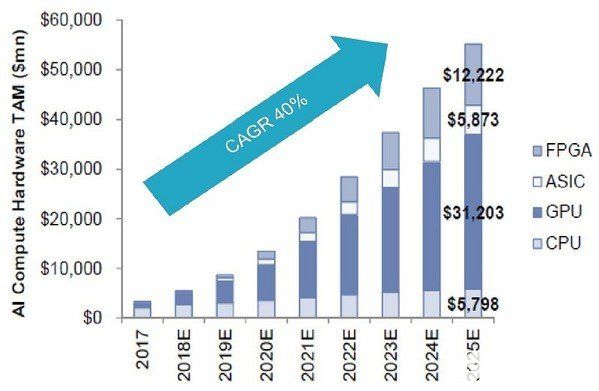

據(jù)九芯電子研究顯示,組成人工智能機能應用所需要的硬件,例如特殊應用語音識別IC(Speech recognition IC)、繪圖處理芯片(GPU)、中央處理器(CPU)、場域可程序化門陣列(FPGA)等組件,在未來數(shù)年間的全球市場規(guī)模,將會以40%年平均成長率急速擴大。

語音芯片封裝高度整合的關鍵:異質(zhì)整合技術

由于算法、大數(shù)據(jù)和高效能語音識別芯片的進步,是扮演推動這一新世代科技浪潮的大動力。因此隨著終端電子產(chǎn)品快速發(fā)展,智慧家居、平板計算機與穿戴裝置等產(chǎn)品不斷朝輕薄短小、多功能、高效能、低成本、低功耗,及小面積等要求發(fā)展的情況下,需將把多種不同功能的ic芯片整合于單一語音模塊中。因此,包括晶圓代工廠、IC設計公司等語音IC制造廠家,相繼投入先進封裝技術領域。根據(jù)Yole數(shù)據(jù)顯示,2017~2021年全球先進封裝規(guī)模從250億美元增至310億美元,年復合成長率約7%。

而這些先進技術的應用與能力,都在近幾年內(nèi)取得了令人驚訝的巨大進展,然而在這些看似不同領域技術或科學的背后,都有一個共同的特點,那就是都采用了異質(zhì)整合(Heterogeneous Integration)的語音IC設計。

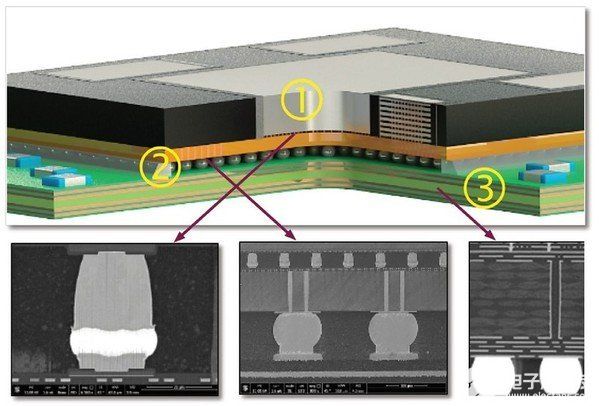

例如,近來出現(xiàn)了另一種稱為「chiplet(小芯片)」的設計概念。所謂chiplet,就是具備特殊用途或單一功能的KGD(known good die)或IP區(qū)塊;然后,在開發(fā)高效能系統(tǒng)時,透過搭配選用適當chiplet的堆棧累積,來達成所需的系統(tǒng)效能。目前的封裝技術是以并排的方式朝2.5D技術發(fā)展,透過中介層(interposer)和重分布層(RDL)設計來進行整合。而3D封裝則是把多顆芯片向上堆棧,除了底層芯片之外,所有芯片都需要透過TSV (硅穿孔)來傳遞訊號。

英特爾(Intel)在CES 2019主題演講中,發(fā)表了采用3D芯片封裝技術的處理器(Lakefield),引起眾人的注目,也讓3D異整合質(zhì)封裝正式邁入商品化的程度。Intel利用堆棧設計,整合各式芯片、I/O、結構等,進而提升IC芯片設計的靈活性,也大幅減少多核處理器所需的芯片空間,讓體積縮小到僅有12mm×12mm。

透過新世代的封裝技術突破摩爾定律

根據(jù)2018年所發(fā)表的IRDS Roadmap(International Roadmap for Devices and Systems),到2030年IC芯片制程技術將達到1.5 nm。但是在半導體前段制程中,根據(jù)摩爾定律應該在5nm左右就難以再突破了,但是隨著技術進步到28nm之后,成本反而會逐漸下降。這似乎違背了產(chǎn)業(yè)中的基礎常識。

例如臺積電(TSMC)不斷地將組件的制程持續(xù)縮小,從14 nm、10 nm、7 nm甚至于目前新開發(fā)的3nm,不僅僅提升CMOS組件的運作速度,同時也大幅度增加了邏輯閘數(shù)。雖然目前3nm制程技術仍在早期研發(fā)階段,臺積電也沒有發(fā)表例如效能及功耗指標等等任何技術細節(jié)(如,和5nm制程相較能提升多少效能),只描述3nm將會是一個全新的制程技術,所以必然也會有新的架構、技術、材料等。而不是5nm制程的提升。

這相當于每經(jīng)過18-24個月的時間,可以在同一空間中,讓組件數(shù)增加一倍,除了加快ic芯片本身的運作速度外,還有兩個因素變得越來越重要。

一個是采用高帶寬儲存(HBM;High Bandwidth Memory)的架構,不僅可提高計算能力之外,還可以降低系統(tǒng)總功耗和增加儲存的帶寬;另一個則為了達到高速數(shù)據(jù)收發(fā)的串行化或解串行化(serializer/deserializer),也就是SerDes。SerDes IO的模塊可以整合到主芯片中,也可以作為單獨的芯片生產(chǎn)制造。

而要如何將這些高速性能進行整合?其中一個關鍵點,就是讓先進的2.5D異質(zhì)整合結構芯片封裝技術來扮演這個角色。但是為什么需要采用2.5D封裝技術,以目前來說,2.5D封裝是一種高階的IC芯片封裝技術,可實現(xiàn)各種IC芯片的高速整合。

審核編輯:湯梓紅

-

封裝

+關注

關注

126文章

7933瀏覽量

143044 -

語音芯片

+關注

關注

12文章

1762瀏覽量

36562 -

九芯電子

+關注

關注

0文章

108瀏覽量

1663

發(fā)布評論請先 登錄

相關推薦

Flash語音芯片相比OTP語音芯片的優(yōu)勢

N9300-S16語音芯片:提升電梯播報體驗,實現(xiàn)導航聲音播報提示

芯片知識:如何將語音精確燒錄至語音芯片

NVC系列-語音提示芯片在智能臺燈上的應用案例

愛普生語音芯片產(chǎn)品特點與應用市場

異質(zhì)整合推動語音芯片封裝前往新境界

異質(zhì)整合推動語音芯片封裝前往新境界

評論