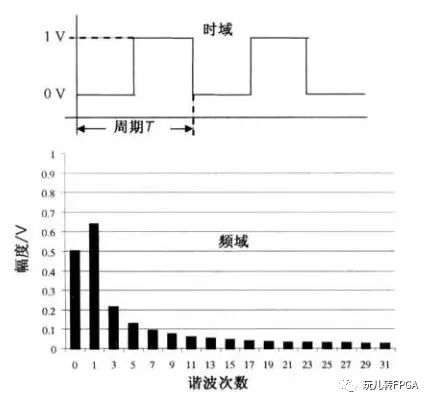

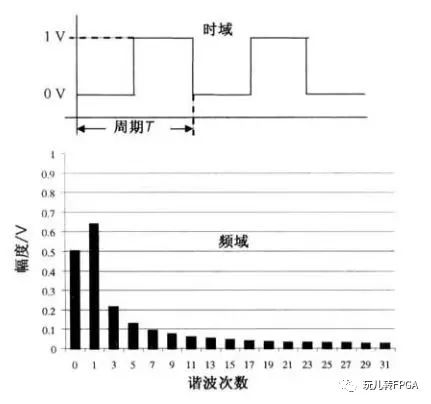

方波時域與頻域

假設方波頻率為f0。橫軸諧波次數為0的柱狀圖代表直流分量的幅值,也就是方波的平均電壓(與占空比有關),諧波次數為1代表頻率為f0的正弦波分量的幅值,3代表,3*f0的正弦波分量幅值,以此類推。

可以看出,諧波只有奇數次的分量,1次諧波開始頻率越高,幅值越低,對波形影響也就越小。

那么,此時如果此方波過一個低通濾波器,將1,3,5,7...次諧波通通濾掉會如何?

結果就會只有一個0次諧波,也就是0.5V(50%占空比)的直流分量。那么此時我們IO輸出占空比變為40%,輸出電壓就是0.4V,占空比80%,輸出就是0.8V,這不就實現了DAC的功能嗎?

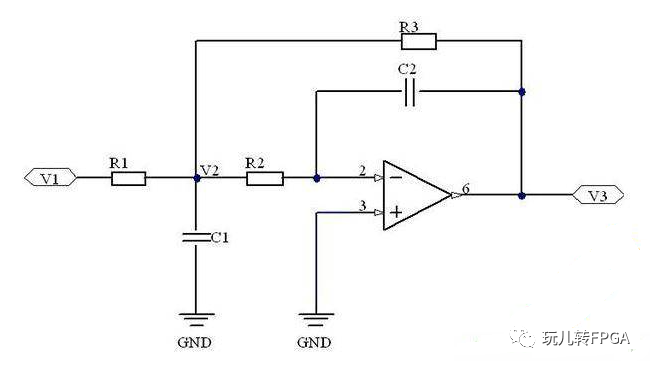

模擬濾波器

二階有源低通濾波器

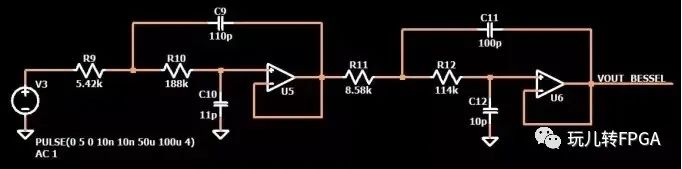

貝塞爾濾波器

除了上圖的濾波器外,如果不追求精度,可以直接LC低通濾波器,簡單實用,親測有效。

Matlab分析方波頻譜代碼

fs=10000; %采樣頻率

t=0:1/fs:1;

subplot(211);

plot(t,x);

subplot(212);

pspectrum(x); %顯示功率譜密度

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603009 -

dac

+關注

關注

43文章

2291瀏覽量

190980 -

模擬濾波器

+關注

關注

0文章

33瀏覽量

13406 -

數字IO

+關注

關注

0文章

8瀏覽量

8066

原文標題:FPGA數字IO如何實現DAC功能

文章出處:【微信號:HaveFunFPGA,微信公眾號:玩兒轉FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DAC3161在應用中若要使用IO TEST該怎么用?

FPGA的IO

如何設計基于FPGA的多功能數字鐘?

將Kintex 7 FPGA與CMOS輸入DAC連接如何實現?

請問CPLD或者FPGA能夠實現任意的IO口對聯嗎?

FPGA實現數字時鐘

基于FPGA和Quartus II的多功能數字鐘設計與實現

FPGA設計中DAC控制的Verilog實現圖文稿

FPGA設計中DAC控制的Verilog實現

FPGA設計中DAC控制的Verilog實現修訂稿

FPGA 結構分析 -IO 資源

基于TXS0108實現FPGA IO Bank接不同外設IO接口電壓轉換

請問FPGA數字IO如何實現DAC功能呢?

FPGA數字IO如何實現DAC功能

FPGA數字IO如何實現DAC功能

評論