最近ChatGPT大火,成功破圈,到底是什么?怎么使用?

簡單說,它是一個模型,一個語言模型!

它是以對話方式與人進行交互的AI語言模型!

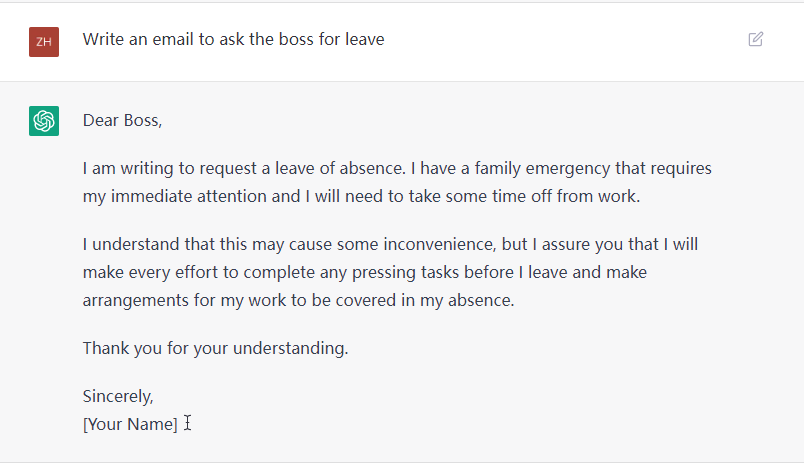

但它能做的事情太多了,可以用它來寫一封請假郵件:

image-20221208210153673

image-20221208210153673還有人用它來學(xué)英語、向它提各種問題,甚至可以用它來寫程序,很多軟件工程師都嘗試過用它來寫Python、Java等編程語言,這里我們就不再嘗試了。

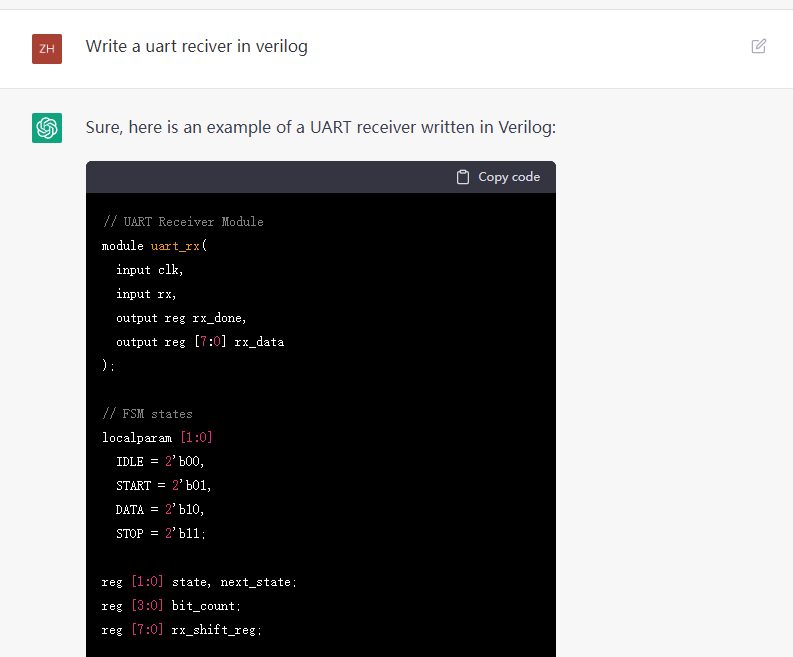

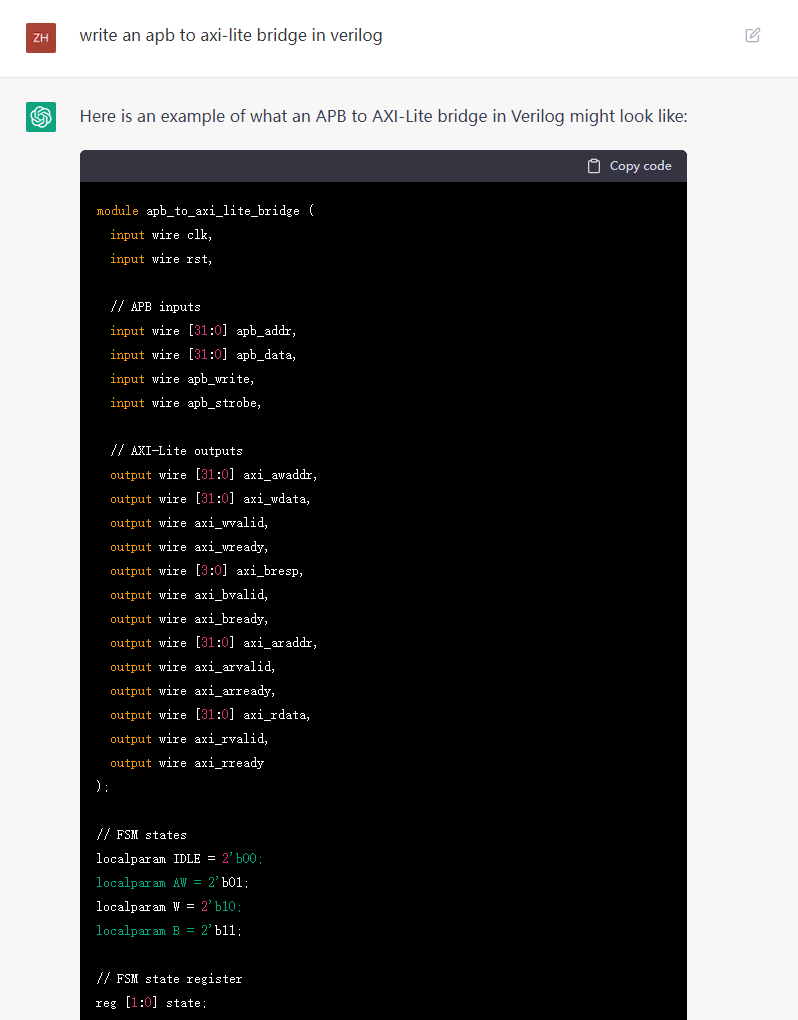

作為FPGA工程師,我們肯定想讓它幫我們寫Verilog!看看效果怎么樣?

image-20221208210533770

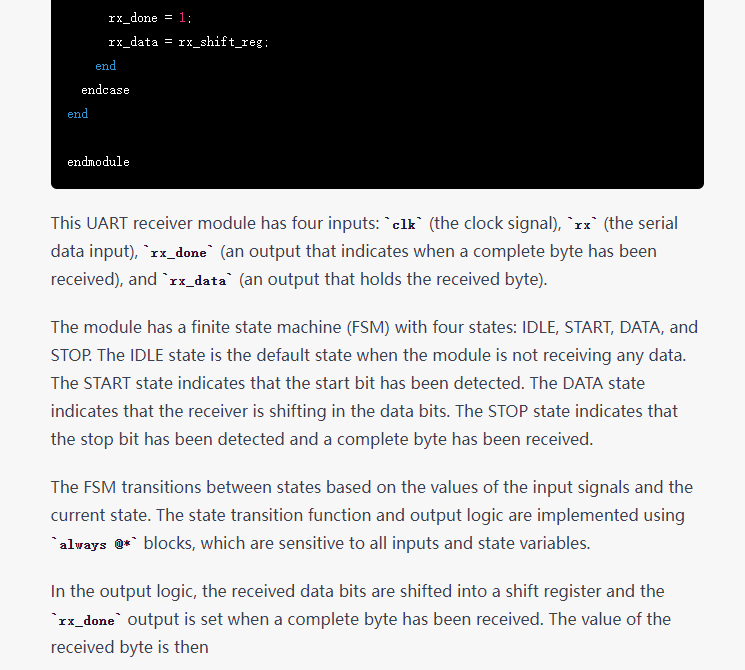

image-20221208210533770在代碼后面甚至還有解釋:

image-20221208210631379

image-20221208210631379完整代碼如下:

//UARTReceiverModule

moduleuart_rx(

inputclk,

inputrx,

outputregrx_done,

outputreg[7:0]rx_data

);

//FSMstates

localparam[1:0]

IDLE=2'b00,

START=2'b01,

DATA=2'b10,

STOP=2'b11;

reg[1:0]state,next_state;

reg[3:0]bit_count;

reg[7:0]rx_shift_reg;

//Initializeoutputs

always@*begin

rx_done=0;

rx_data=0;

end

//Statetransitionlogic

always@(posedgeclk)begin

state<=?next_state;

end

//Statetransitionfunction

always@*begin

case(state)

IDLE:begin

if(rx)next_state=START;

elsenext_state=IDLE;

end

START:begin

if(rx)next_state=DATA;

elsenext_state=IDLE;

end

DATA:begin

if(bit_count==0)next_state=STOP;

elseif(rx)next_state=DATA;

elsenext_state=IDLE;

end

STOP:begin

if(rx)next_state=IDLE;

elsenext_state=STOP;

end

endcase

end

//Outputlogic

always@*begin

case(state)

IDLE:begin

bit_count=4;

rx_shift_reg=0;

end

START:begin

bit_count=3;

end

DATA:begin

bit_count=bit_count-1;

rx_shift_reg={rx_shift_reg[6:0],rx};

end

STOP:begin

rx_done=1;

rx_data=rx_shift_reg;

end

endcase

end

endmodule

雖然沒有驗證這個功能是否正確,但這個代碼的邏輯看起來應(yīng)該是沒有錯的。

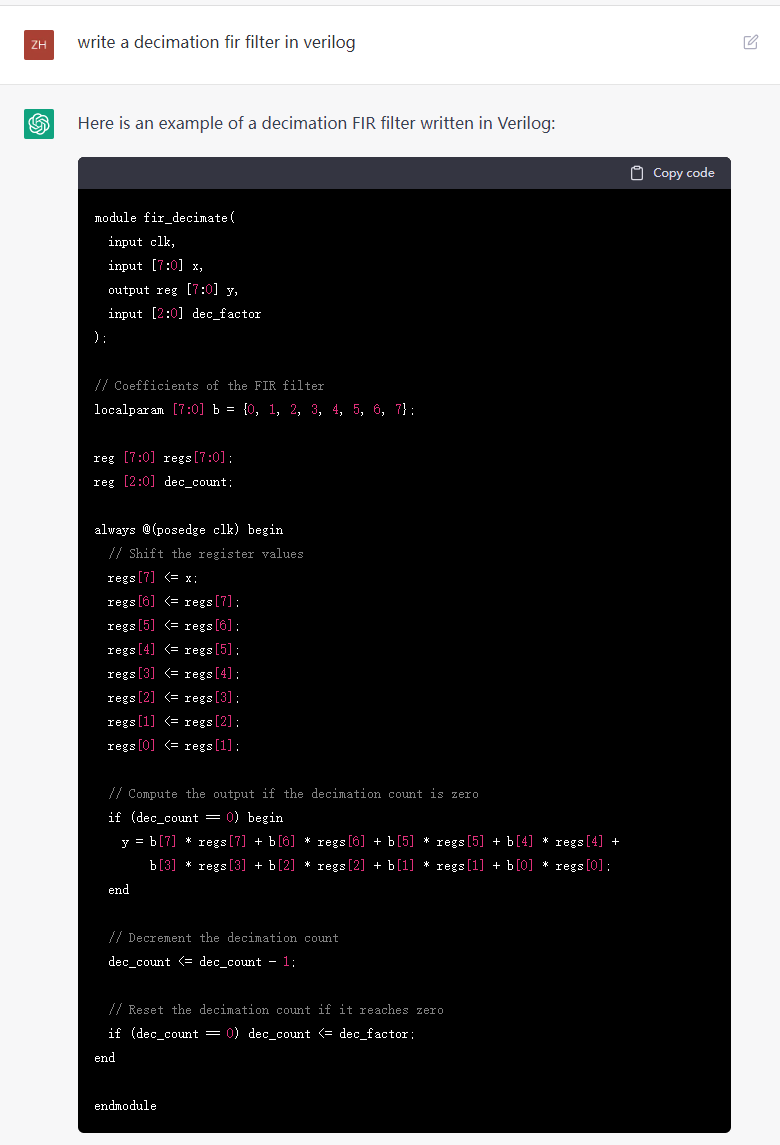

再寫個稍微復(fù)雜一點但仍然是標(biāo)準的協(xié)議:apb轉(zhuǎn)axi-lite的bridge。

完整代碼很長,我也并沒有驗過,但大概看下來,功能基本都有。

對于過于復(fù)雜的,就無能為力了,比如:以太網(wǎng)協(xié)議棧。

但有個更有意思的現(xiàn)象,當(dāng)我第一次讓它寫以太網(wǎng)協(xié)議棧時,它提示太難了,寫不出來。

把對話復(fù)位后,再讓它寫,它就會寫一個大概的module,里面只有些接口,后面又復(fù)位對話后再重新讓它寫了,寫出來的程序就更多了。

說明它的學(xué)習(xí)能力一直在增長。

可能現(xiàn)在它的功能還并不是很完善,但作為工程師,看到這么強大的功能,不禁有些感慨,我們的核心競爭力是什么?如果真的有一天,AI可以幫我們寫代碼了,我們該去做什么?

(抖個機靈:是不是到時候只需要驗證工程師了?)

最后補充一點,這個網(wǎng)站的注冊是需要一個國外的手機號,可能很多人弄不到,所以,如果你有什么有趣的功能想嘗試,可以跟我聯(lián)系,我來幫你試。

審核編輯 :李倩

-

Verilog

+關(guān)注

關(guān)注

29文章

1367瀏覽量

112355 -

AI

+關(guān)注

關(guān)注

88文章

35306瀏覽量

280635 -

語言模型

+關(guān)注

關(guān)注

0文章

562瀏覽量

10809

原文標(biāo)題:如何用AI來寫Verilog代碼?

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

HarmonyOS AI輔助編程工具(CodeGenie)代碼智能解讀

HarmonyOS AI輔助編程工具(CodeGenie)代碼續(xù)寫

Verilog 與 ASIC 設(shè)計的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog 測試平臺設(shè)計方法 Verilog FPGA開發(fā)指南

Verilog與VHDL的比較 Verilog HDL編程技巧

騰訊申請注冊“騰訊云AI代碼助手”商標(biāo)

Verilog硬件描述語言參考手冊

如何利用Verilog-A開發(fā)器件模型

評論