硬盤是大家都很熟悉的設備,一路走來,從HDD到SSD,從SATA到NVMe,作為NVMe SSD的前端接口,PCIe再次進入我們的視野。作為x86體系關鍵的一環,PCIe標準歷經PCI,PCI-X和PCIe,走過近30年時光。其中Host發現與查找設備的方式卻一脈沿襲,今天我們先來聊一聊PCIe設備在一個系統中是如何發現與訪問的。

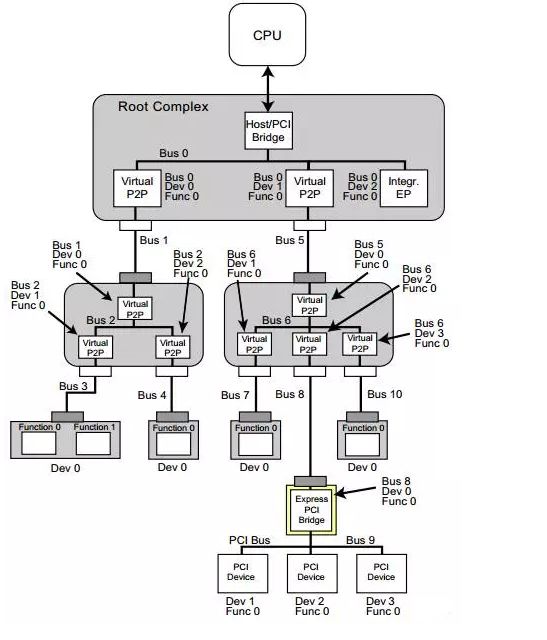

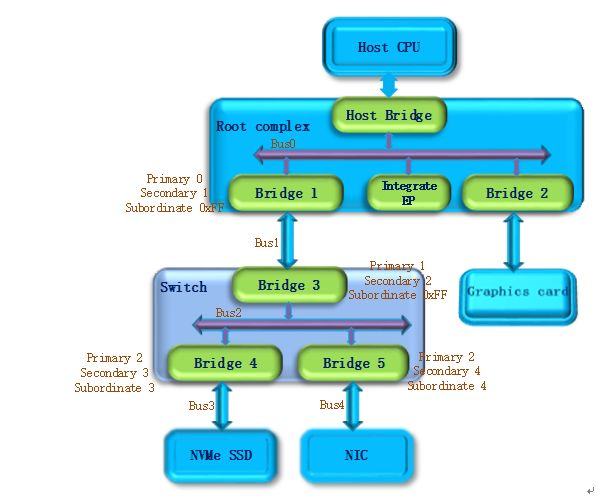

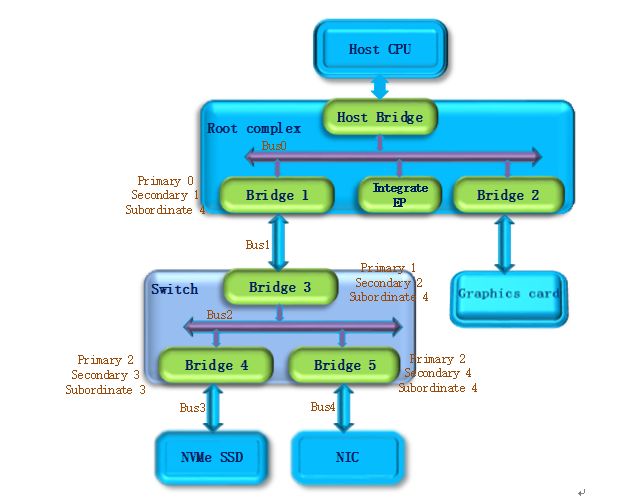

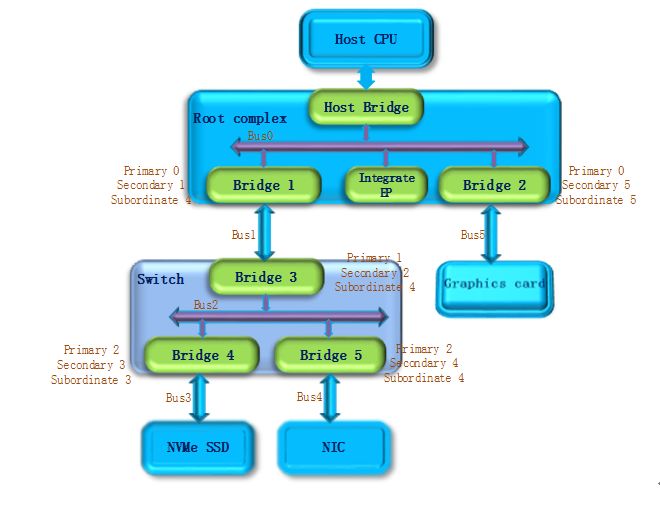

首先我們來看一下在x86系統中,PCIe是什么樣的一個體系架構。下圖是一個PCIe的拓撲結構示例,PCIe協議支持256個Bus, 每條Bus最多支持32個Device,每個Device最多支持8個Function,所以由BDF(Bus,device,function)構成了每個PCIe設備節點的身份證號。

PCIe體系架構一般由root complex,switch,endpoint等類型的PCIe設備組成,在root complex和switch中通常會有一些embeded endpoint(這種設備對外不出PCIe接口)。這么多的設備,CPU啟動后要怎么去找到并認出它們呢? Host對PCIe設備掃描是采用了深度優先算法,其過程簡要來說是對每一個可能的分支路徑深入到不能再深入為止,而且每個節點只能訪問一次。我們一般稱這個過程為PCIe設備枚舉。枚舉過程中host通過配置讀事物包來獲取下游設備的信息,通過配置寫事物包對下游設備進行設置。

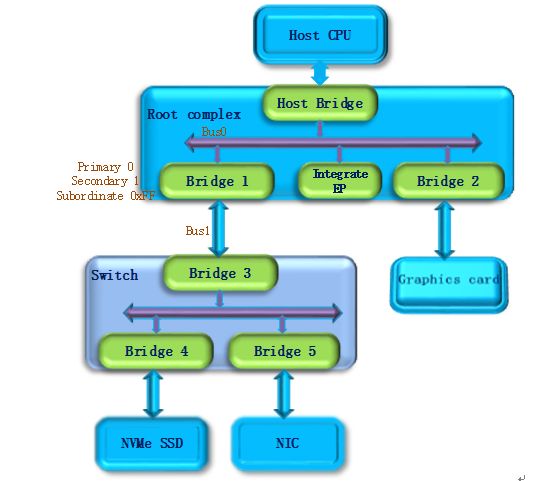

第一步,PCI Host主橋掃描Bus 0上的設備(在一個處理器系統中,一般將Root complex中與Host Bridge相連接的PCI總線命名為PCI Bus 0),系統首先會忽略Bus 0上的embedded EP等不會掛接PCI橋的設備,主橋發現Bridge 1后,將Bridge1 下面的PCI Bus定為 Bus 1,系統將初始化Bridge 1的配置空間,并將該橋的Primary Bus Number 和 Secondary Bus Number寄存器分別設置成0和1,以表明Bridge1 的上游總線是0,下游總線是1,由于還無法確定Bridge1下掛載設備的具體情況,系統先暫時將Subordinate Bus Number設為0xFF。

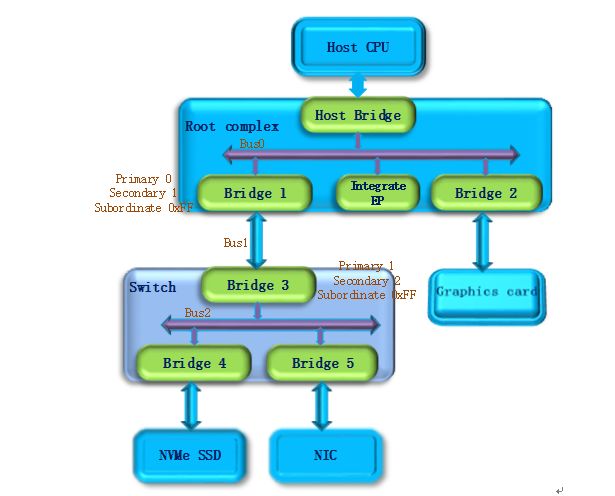

第二步,系統開始掃描Bus 1,將會發現Bridge 3,并發現這是一個switch設備。系統將Bridge 3下面的PCI Bus定為Bus 2,并將該橋的Primary Bus Number 和 Secondary Bus Number寄存器分別設置成1和2,和上一步一樣暫時把Bridge 3 的Subordinate Bus Number設為0xFF。

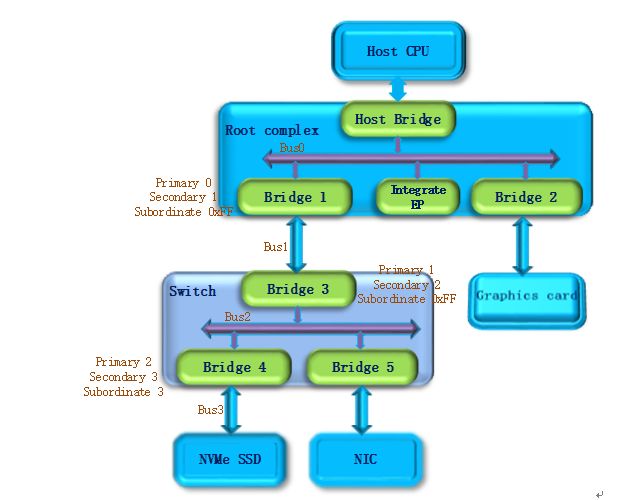

第三步,系統繼續掃描Bus 2,將會發現Bridge 4。繼續掃描,系統會發現Bridge下面掛載的NVMe SSD設備,系統將Bridge 4下面的PCI Bus定為Bus 3,并將該橋的Primary Bus Number 和 Secondary Bus Number寄存器分別設置成2和3,因為Bus3下面掛的是端點設備(葉子節點),下面不會再有下游總線了,因此Bridge 4的Subordinate Bus Number的值可以確定為3。

第四步,完成Bus 3的掃描后,系統返回到Bus 2繼續掃描,會發現Bridge 5。繼續掃描,系統會發現下面掛載的NIC設備,系統將Bridge 5下面的PCI Bus設置為Bus 4,并將該橋的Primary Bus Number 和 Secondary Bus Number寄存器分別設置成2和4,因為NIC同樣是端點設備,Bridge 5的Subordinate Bus Number的值可以確定為4。

第五步,除了Bridge 4和Bridge 5以外,Bus2下面沒有其他設備了,因此返回到Bridge 3,Bus 4是找到的掛載在這個Bridge下的最后一個bus號,因此將Bridge 3的Subordinate Bus Number設置為4。Bridge 3的下游設備都已經掃描完畢,繼續向上返回到Bridge 1,同樣將Bridge 1的Subordinate Bus Number設置為4。

第六步,系統返回到Bus0繼續掃描,會發現Bridge 2,系統將Bridge 2下面的PCI Bus定為Bus 5。并將Bridge 2的Primary Bus Number 和 Secondary Bus Number寄存器分別設置成0和5, Graphics card也是端點設備,因此Bridge 2 的Subordinate Bus Number的值可以確定為5。

至此,掛在PCIe總線上的所有設備都被掃描到,枚舉過程結束,Host通過這一過程獲得了一個完整的PCIe設備拓撲結構。

系統上電以后,host會自動完成上述的設備枚舉過程。除一些專有系統外,普通系統只會在開機階段進行進行設備的掃描,啟動成功后(枚舉過程結束),即使插入一個PCIe設備,系統也不會再去識別它。

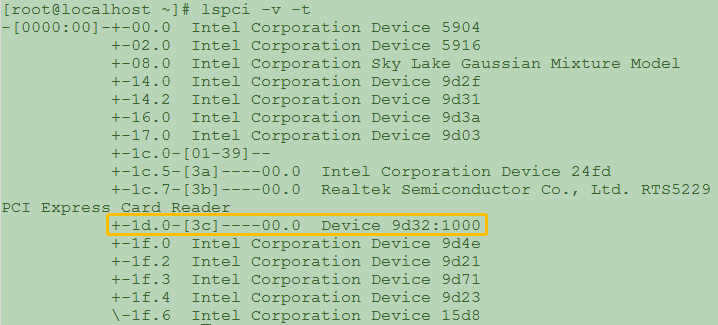

在linux操作系統中,我們可以通過lspci –v -t命令來查詢系統上電階段掃描到的PCIe設備,執行結果會以一個樹的形式列出系統中所有的pcie設備。如下圖所示,其中黃色方框中的PCIe設備是北京憶芯科技公司(Bejing Starblaze Technology Co., LTD.)推出的STAR1000系列NVMe SSD主控芯片,圖中顯示的9d32是Starblaze在PCI-SIG組織的注冊碼,1000是設備系列號。

STAR1000設備的BDF也可以從上圖中找出,其中bus是0x3C,device是0x00,function是0x0,BDF表示為3C:00.0,與之對應的上游端口是00:1d.0。

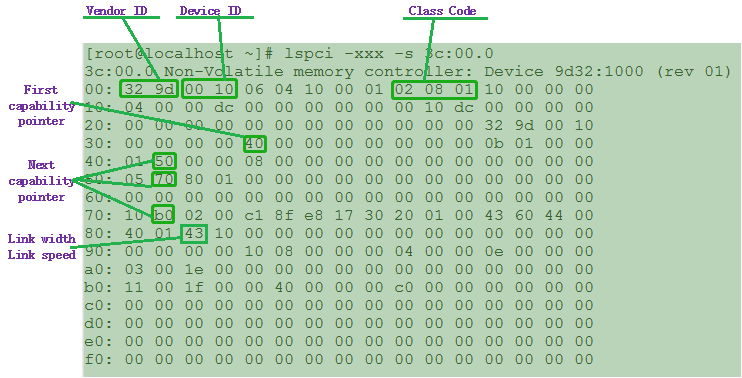

我們可以通過“lspci –xxx –s 3C:00.0”命令來列出該設備的PCIe詳細信息(技術發燒友或數字控請關注該部分)。這些內容存儲在PCIe配置空間,它們描述的是PCIe本身的特性。如下圖所示(低位地址0x00在最左邊),可以看到這是一個非易失性存儲控制器,0x00起始地址是PCIe的Vendor ID和Device ID。Class code 0x010802表示這是一個NVMe存儲設備。0x40是第一組capability的指針,如果你需要查看PCIe的特性,就需要從這個位置開始去查詢,在每組特征的頭字段都會給出下一組特性的起始地址。從0x40地址開始依次是power management,MSI中斷,鏈路控制與狀態,MSI-X中斷等特性組。這兒特別列出了鏈路特征中的一個0x43字段,表示STAR1000設備是一個x4lane的鏈接,支持PCIe Gen3速率(8Gbps)。

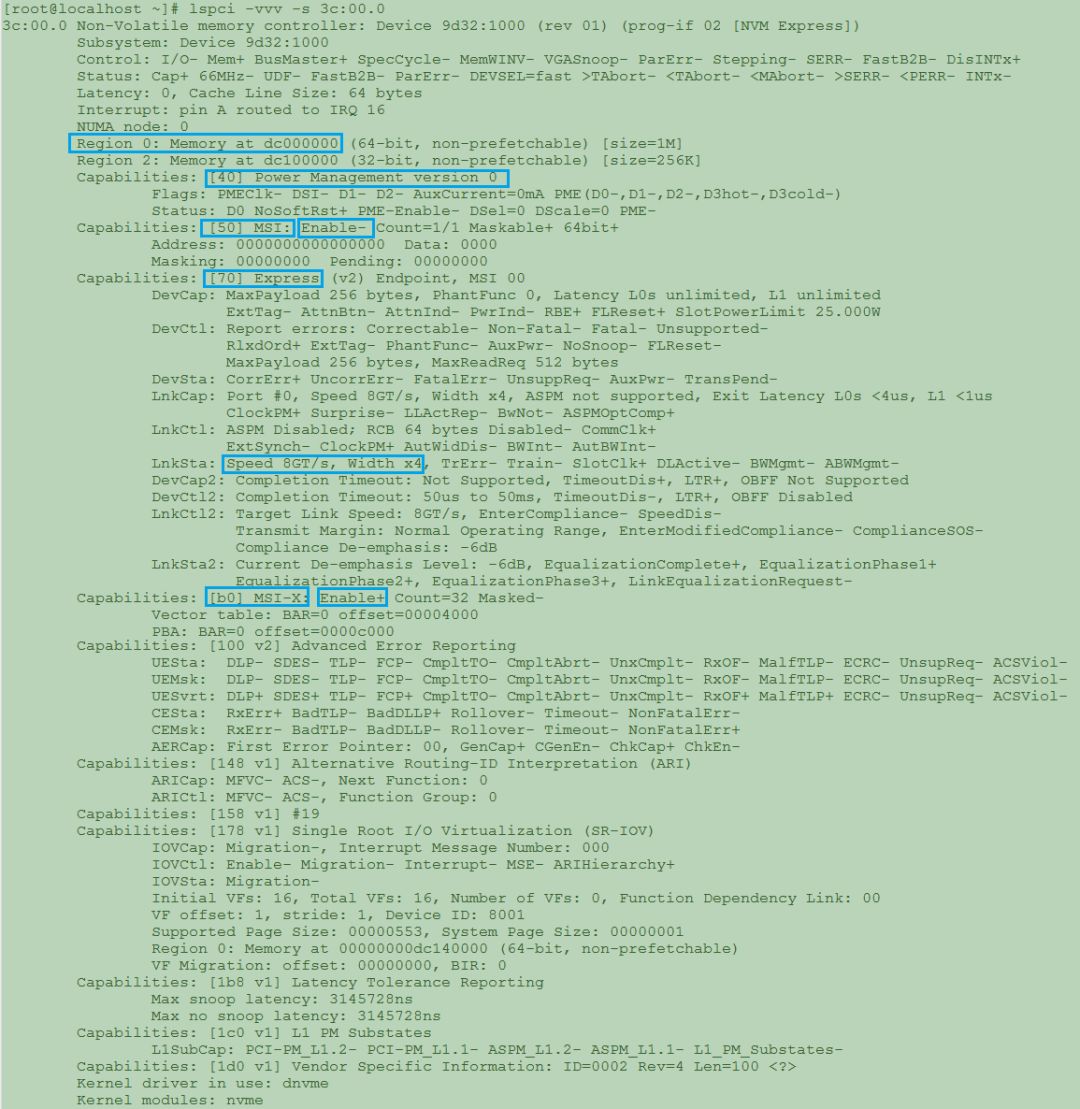

當然也可以使用lspci –vvv –s 3C:00.0命令來查看設備特性,初學者看到下面的列表也就一目了然了。

Host在枚舉設備的同時也會對設備進行配置,每個PCIe設備都會指定一段CPU memory訪問空間,從上面的圖中我們可以看到這個設備支持兩段訪問空間,一段的大小是1M byte,另一段的大小是256K byte,系統會分別指定它們的基地址。基地址配置完成以后,Host就可以通過地址來對PCIe memory空間進行訪問了。

PCIe memory空間關聯的是PCIe設備物理功能,對于STAR1000系列芯片而言,物理功能是NVMe,memory中存放的是NMVe的控制與狀態信息,對于NMVe的控制以及工作狀態的獲取,都需要通過memory訪問來實現。

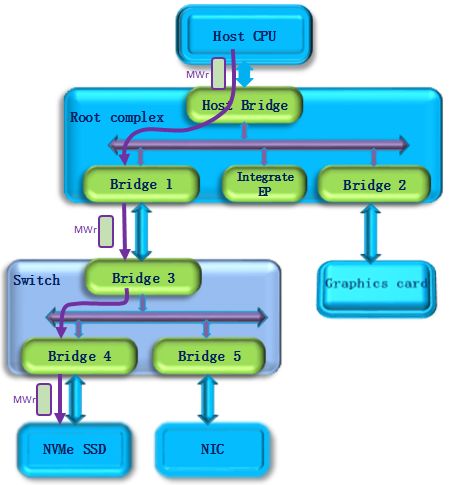

下面以NVMe命令下發為例簡單描述PCIe設備的memory訪問。NVMe命令下發的基本操作是1)Host寫doorbell寄存器,此時使用PCIe memory寫請求。如下圖所示,host發出一個memory write(MWr)請求,該請求經過switch到達要訪問的NVMe SSD設備。

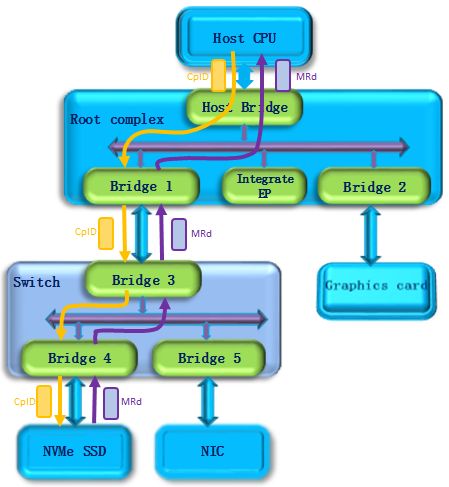

這個請求會被端點設備接收并執行2)NVMe讀取命令操作。如下圖所示,此時NVMe SSD作為請求者,發出一個memory read(MRd)請求,該請求經過Switch到達Host,Host作為完成者會返回一個完成事物包(CplD),將訪問結果返回給NVMe SSD。

這樣,一個NVMe的命令下發過程就完成了。同樣,NVMe的其他操作比如各種隊列操作,命令與完成,數據傳輸都是通過PCIe memory訪問的方式進行的,此處不再詳述。

通過上面的描述,相信能夠幫助大家了解PCIe的設備枚舉和memory空間訪問。以后會繼續與大家探討PCIe的其他內容,比如PCIe的協議分層,鏈路建立,功耗管理等等。目前PCIe協議還正在不斷的快速演進中,2017年發布的PCIe Gen4標準,每條Serdes支持的速率已經達到16Gbps,Gen5也在加速制定中,其速率會再翻一倍達到32Gbps。Starblaze會緊跟技術的發展趨勢,提供速率更高,性能更好更穩定的NVMe SSD系列產品。

審核編輯:湯梓紅

-

SSD

+關注

關注

21文章

2857瀏覽量

117370 -

PCIe

+關注

關注

15文章

1234瀏覽量

82584 -

nvme

+關注

關注

0文章

221瀏覽量

22621

原文標題:聊聊PCIe設備在系統如何發現與訪問?

文章出處:【微信號:架構師技術聯盟,微信公眾號:架構師技術聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

windows xp無法正常掃描和安裝驅動PCIE設備

如何使用pcie鏈接從外部處理器訪問bram?

如何訪問內部寄存器空間或PCIe?

無法訪問s32v234板中的PCIe是怎么回事?

PCIe設備在一個系統中是如何發現與訪問的

聊聊PCIe Bus(PCIe總線)

PCI/PCIe最容易訪問的設備是什么

聊聊PCIe設備在系統如何發現與訪問?

聊聊PCIe設備在系統如何發現與訪問?

評論