隨著嵌入式設備的智能化需求越來越高,對MCU的性能要求也越來越高。一方面可以通過提高MCU的主頻來提升MCU的性能,但是這會使MCU的設計變得更復雜。另一方面可以通過多核的方式來提升MCU的性能,目前多核MCU已在市場上廣泛應用。隨著多核MCU的出現,多核調試變得越來越重要。

本文主要介紹如何在IAR Embedded Workbench for Arm中進行多核調試。

多核的基本概念

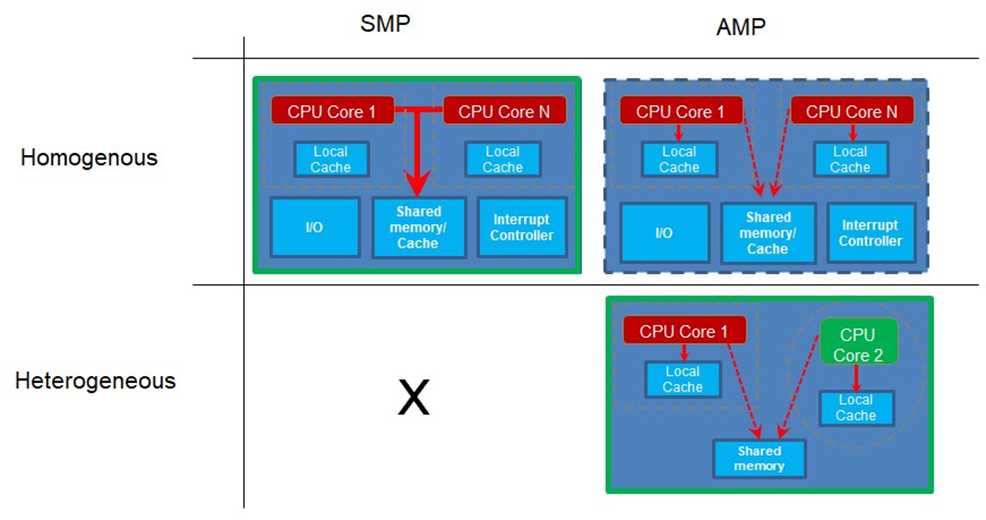

同構多核(Homogeneous)vs 異構多核(Heterogeneous)

從硬件設計上,多核可以分為同構多核和異構多核:同構多核指的是所有的核具用相同的架構,比如NXP的S32K3(Cortex-M7)和芯馳科技的E3(Cortex-R5)。異構多核指的是核具用不同的架構,比如Infineon的Traveo T2G (Cortex-M0+ + Cortex-M4/Cortex-M7)和ST的STM32H7 (Cortex-M4 + Cortex-M7)。

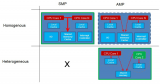

對稱多處理(SMP)vs 非對稱多處理(AMP)

從軟件設計上,多核可以分為對稱多處理(SMP)和非對稱多處理(AMP):SMP指的是所有的核運行同一套程序(一般通過CoreID來實現不同的核執行不同的操作),AMP指的是不同的核運行不同的程序。

注意:只有同構多核才能實現SMP,同構多核也可以實現AMP,異構多核只能實現AMP:

在IAR Embedded Workbench for Arm中進行多核調試

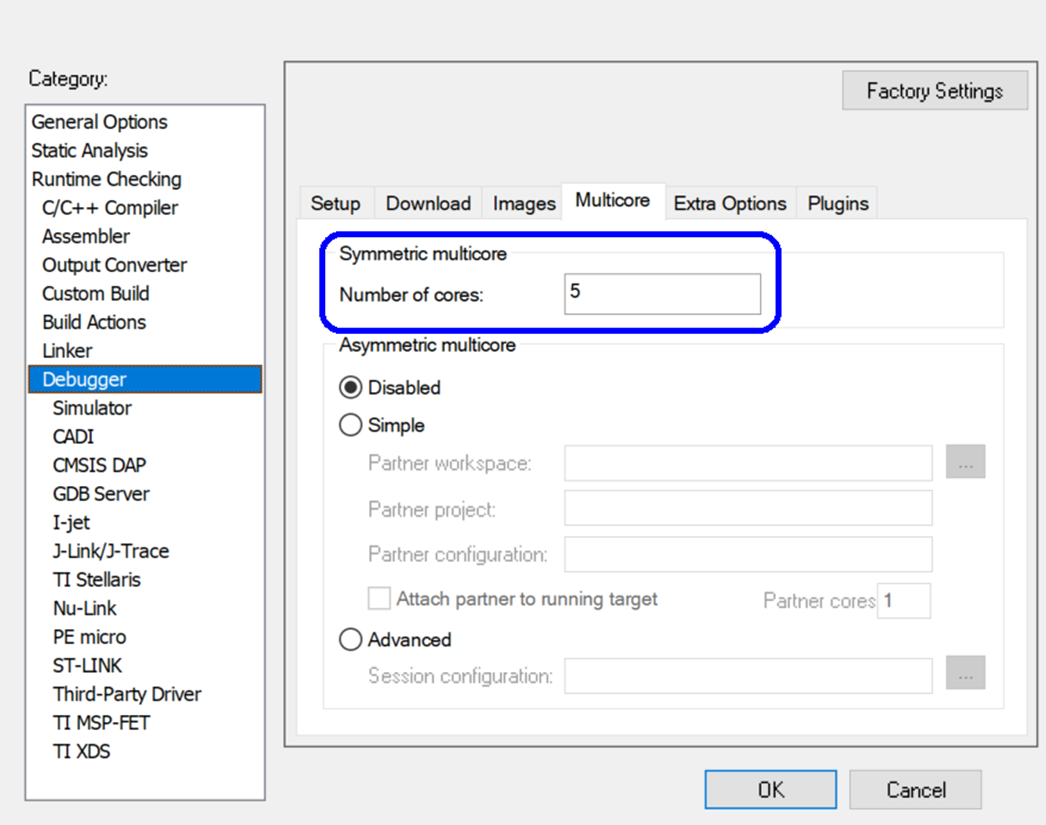

同構多核SMP多核調試

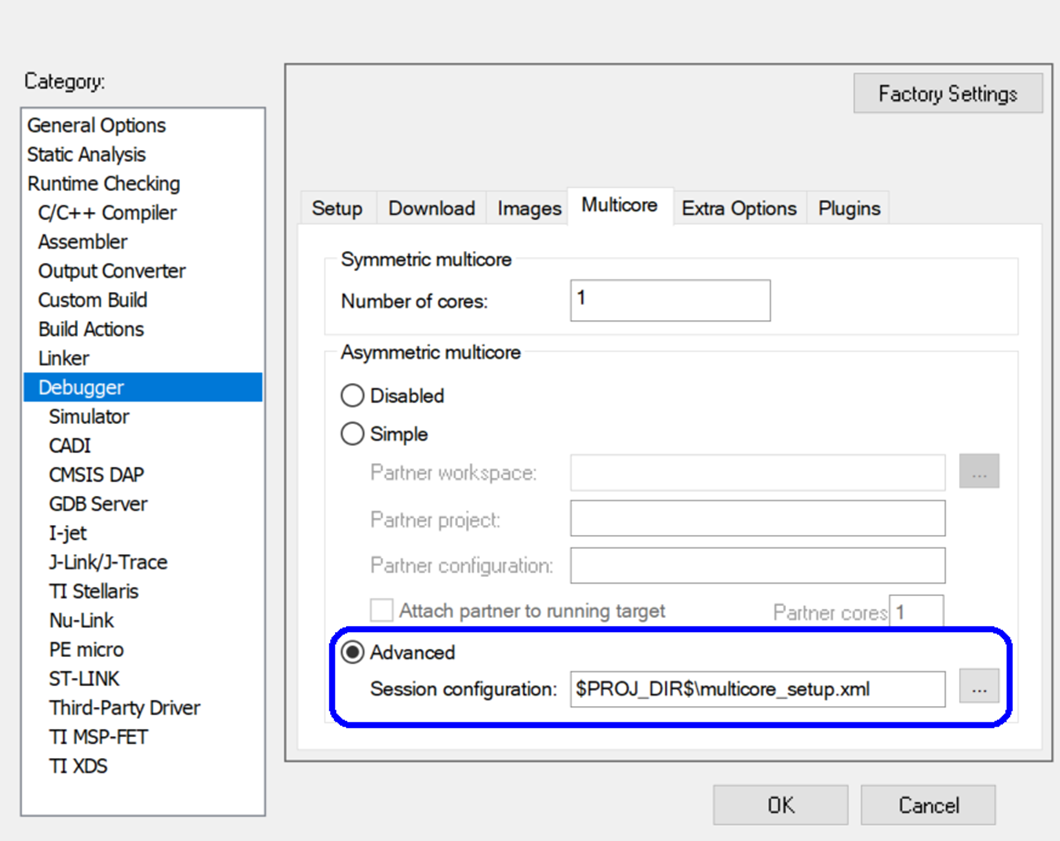

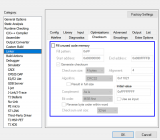

對于同構多核SMP多核調試,需要在Debugger > Multicore > Symmetric multicore > Number of cores中輸入對應核的數量:

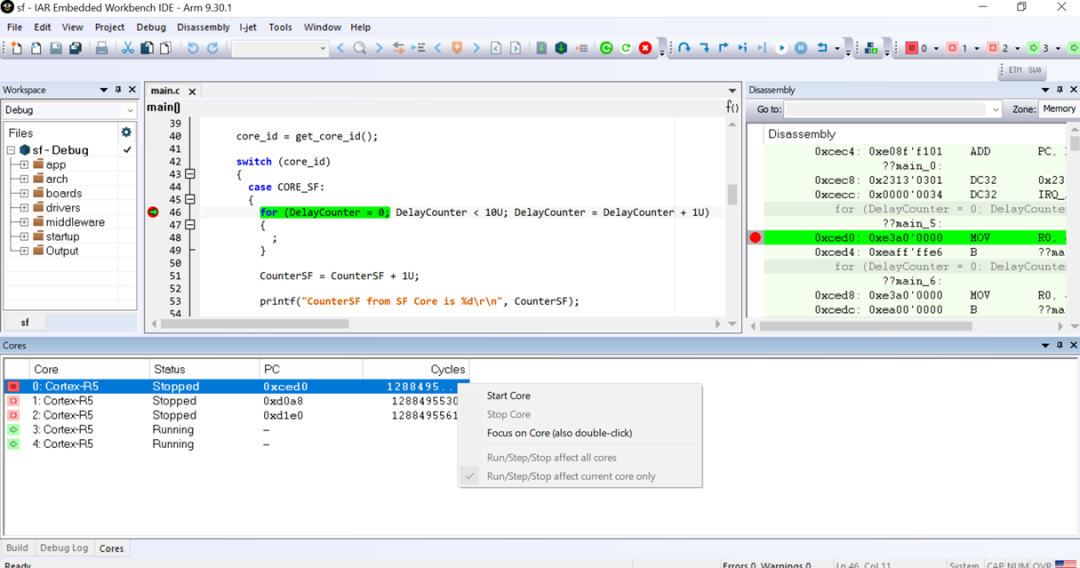

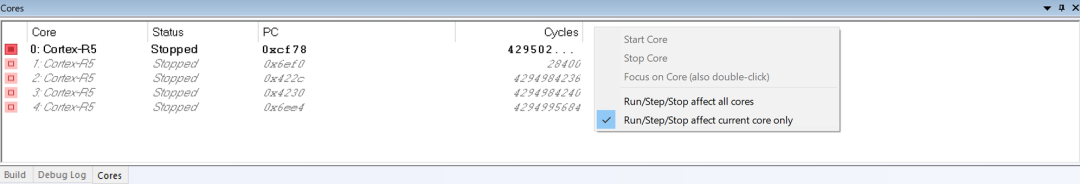

由于SMP中所有的核運行同一套程序,調試的時候只會開啟一個IAR Embedded Workbench IDE。可以通過View > Cores可以打開對應的Cores窗口來查看和操作對應Core的狀態:

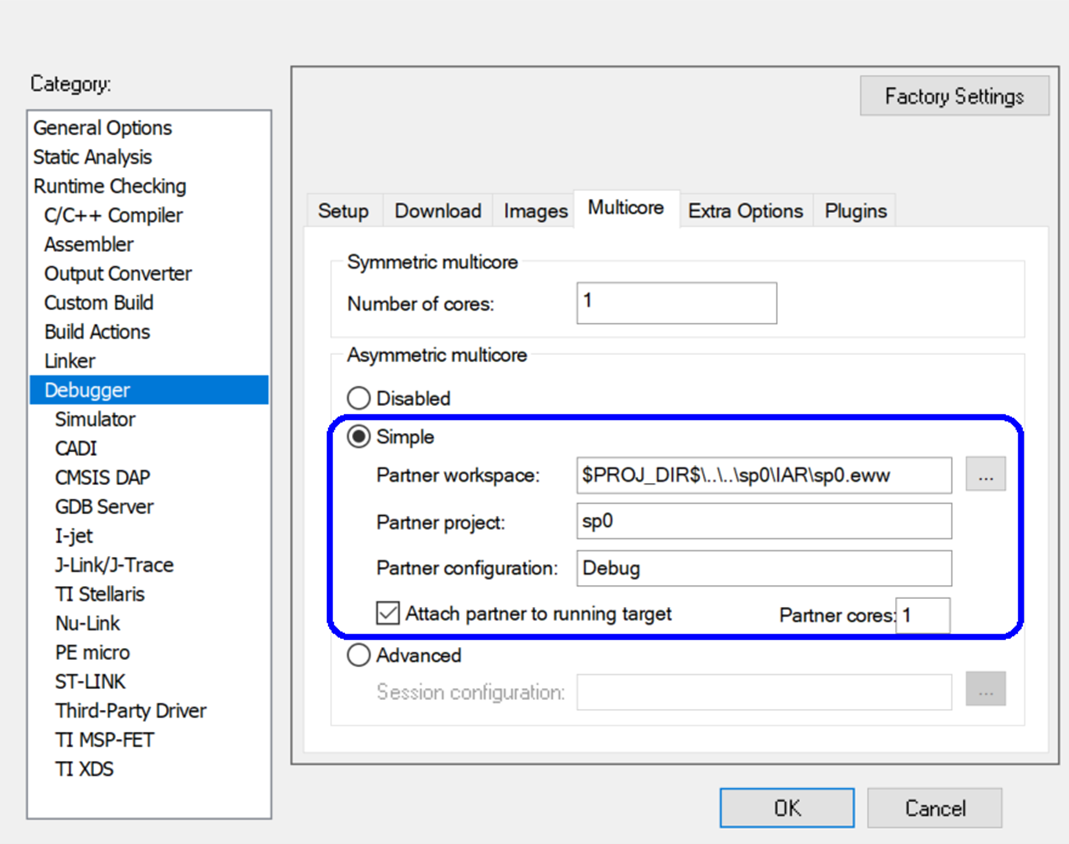

同構多核AMP多核調試

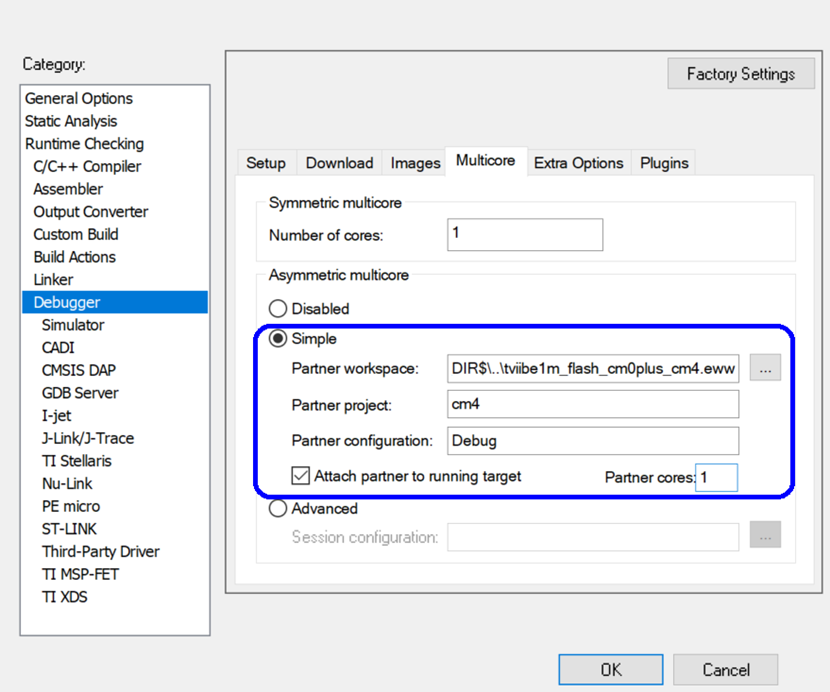

對于同構多核AMP多核調試,如果只有一個Partner工程,可以在Debugger > Multicore > Asymmetric multicore > Simple中輸入對應Partner工程的配置:

對于異構多核AMP多核調試,如果有多個Partner工程,可以在Debugger > Multicore > Asymmetric multicore > Advanced中輸入對應Partner工程的xml配置文件(一個Partner工程也可以使用這種方式):

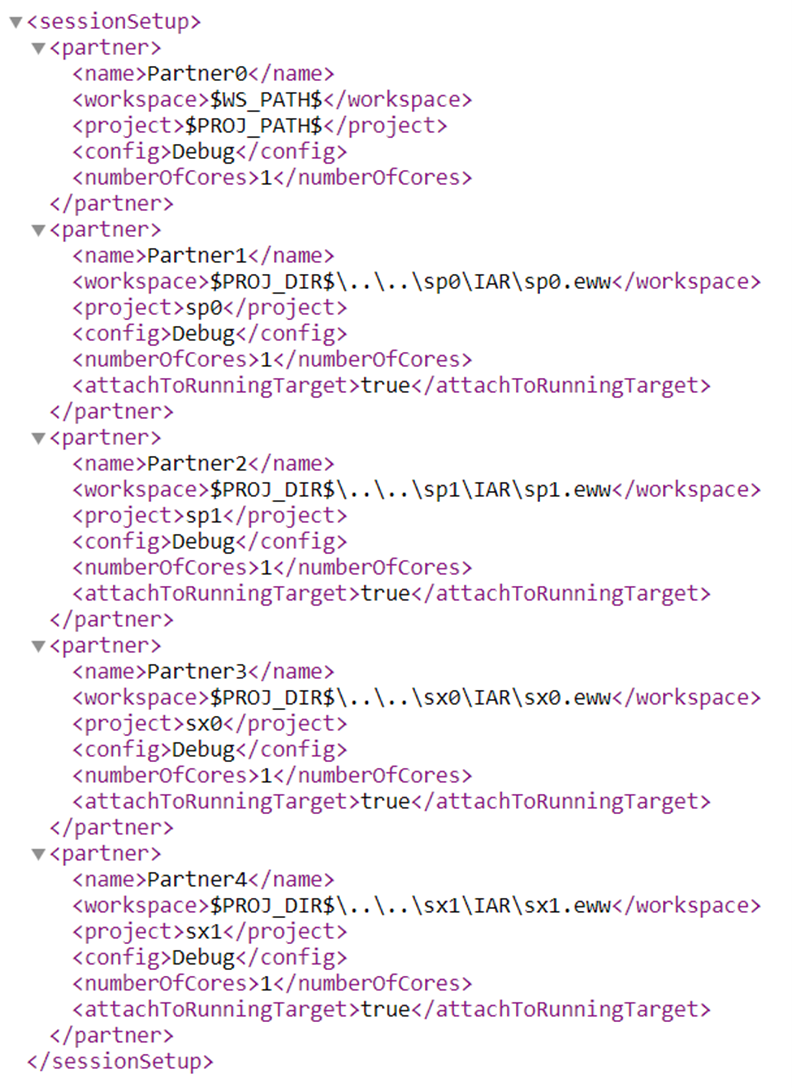

其中xml文件中會描述所有核的相關配置信息(參考如下):

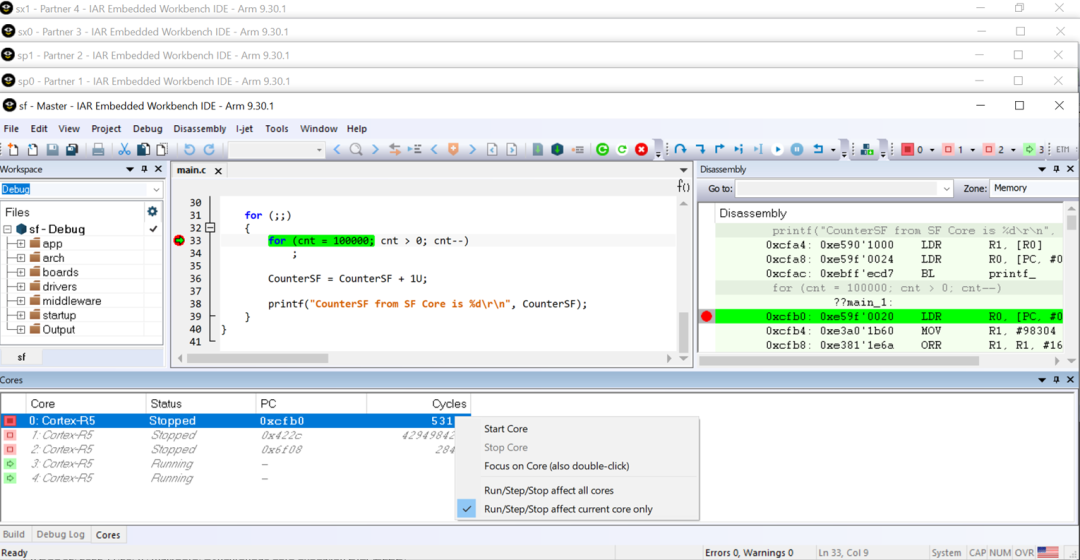

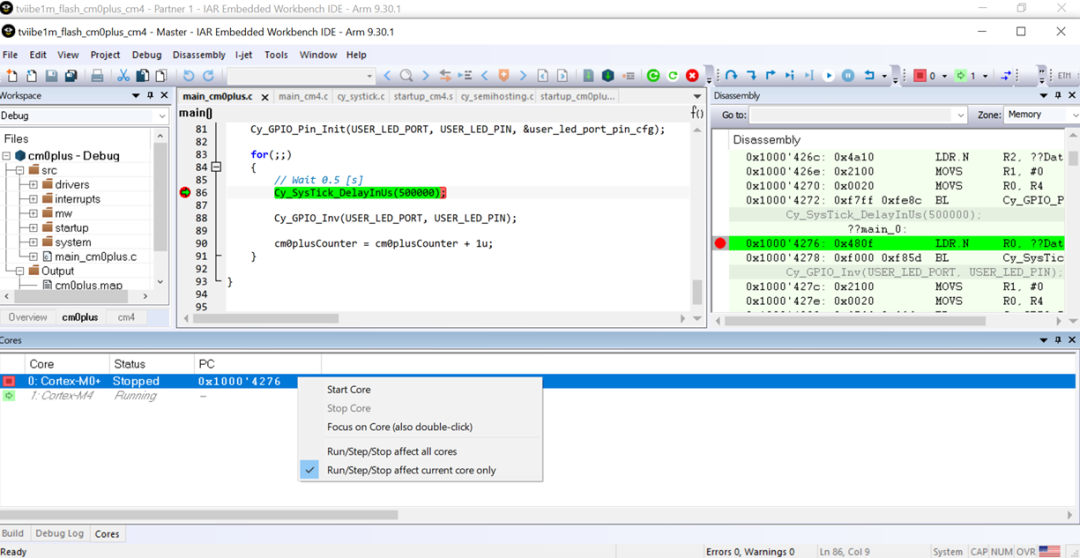

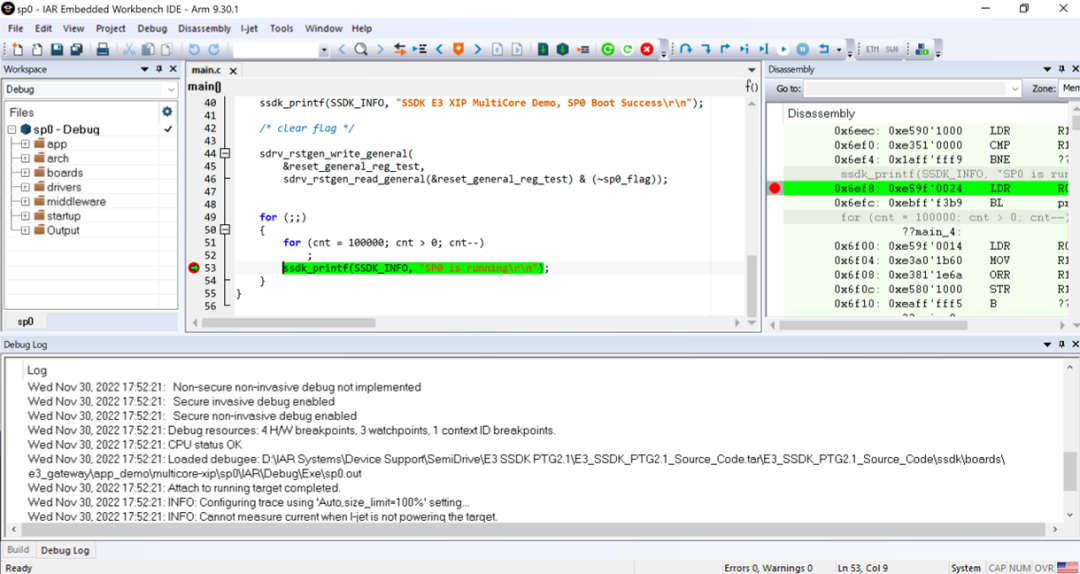

由于AMP中不同的核運行不同的程序,調試時每個核都會開啟獨立的IAR Embedded Workbench IDE,可以通過View > Cores可以打開對應的Cores窗口來查看和操作對應Core的狀態:

異構多核AMP多核調試

對于異構多核AMP多核調試,配置跟同構多核AMP多核調試類似:

由于AMP中不同的核運行不同的程序,調試時每個核都會開啟獨立的IAR Embedded Workbench IDE,可以通過View > Cores可以打開對應的Cores窗口來查看和操作對應Core的狀態:

注意事項

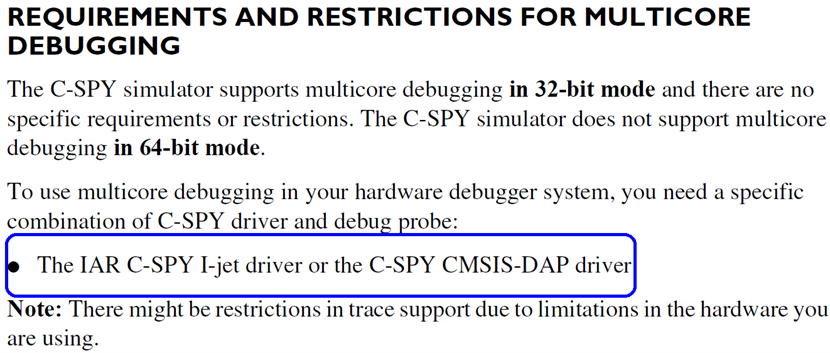

1. 當前IAR Embedded Workbench for Arm多核調試功能只支持I-jet和CMSIS-DAP

2. 如果多核MCU默認開始工作時只使能Master,需要Master來使能其它的核,才能進行多核調試。可以通過單獨調試其它的核來確認對應的核是可以調試的。

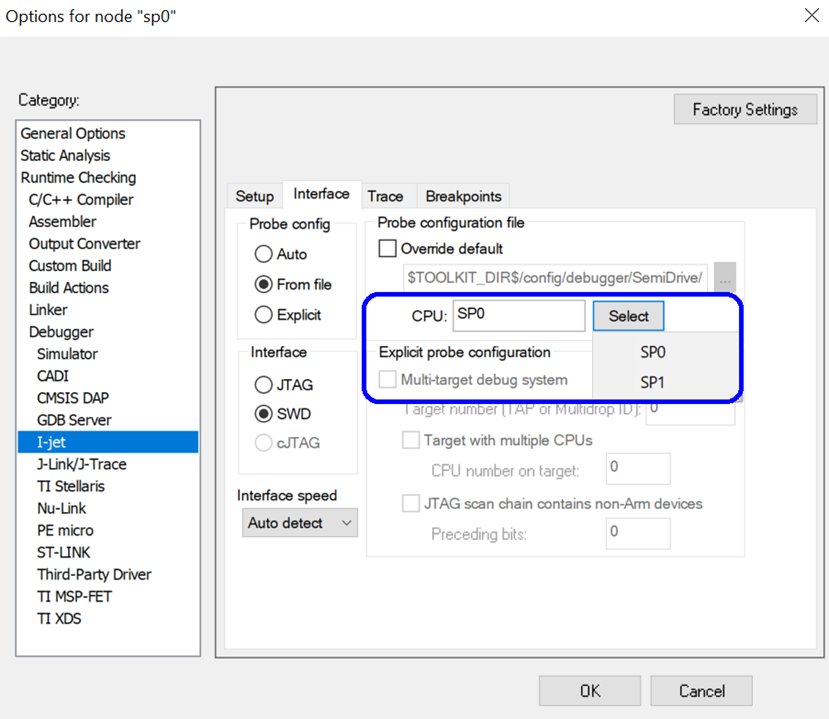

3. 對于同構多核實現AMP,每個核需要指定具體的對應CPU:

4. 多核調試時,每個核可以單獨控制,也可以一起控制,通過Run/Step/Stop affect all cores 和Run/Step/Stop affect current core only選項來選擇:

總結

主要介紹了如何在IAR Embedded Workbench for Arm中進行SMP和AMP多核調試。

審核編輯:湯梓紅

-

mcu

+關注

關注

146文章

17123瀏覽量

350992 -

ARM

+關注

關注

134文章

9084瀏覽量

367387 -

IAR

+關注

關注

5文章

350瀏覽量

36665 -

多核調試

+關注

關注

0文章

3瀏覽量

5660

原文標題:在IAR Embedded Workbench for Arm中進行多核調試

文章出處:【微信號:IAR愛亞系統,微信公眾號:IAR愛亞系統】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

在IAR Embedded Workbench中進行ARM+RISC-V多核調試

在IAR Embedded Workbench中計算多個地址區間的Checksum

在IAR版本為Embedded Workbench 6.5 Kickstart 1.4 編繹報錯怎么解決?

在 IAR Embedded Workbench中進行ARM+RISC-V多核調試

IAR Systems發布 IAR Embedded Wor

IAR_embedded_Workbench用戶指南介紹

IAR Embedded Workbench?集成開發環境已全面支持航順芯片HK32MCU系列

YRDKRX62N 快速入門指南(IAR Embedded Workbench)

YRDKRL78G13 快速入門指南(IAR Embedded Workbench) Rev.1.01

IAR發布最新IAR Embedded Workbench for Arm v9.40版本

YRDKRX62N 快速入門指南(IAR Embedded Workbench)

YRDKRL78G13 快速入門指南(IAR Embedded Workbench) Rev.1.01

在IAR Embedded Workbench for Arm中進行多核調試

在IAR Embedded Workbench for Arm中進行多核調試

評論